# Mobile Computer Display Controller

Version 1.0

Last Updated 05/24/06

Lynx3DM+ Databook

# Silicon Motion®, Inc.

## Lynx3DM+ DataBook

#### **Notice**

Silicon Motion<sup>®</sup>, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by Silicon Motion, Inc. for the use of this information, nor for infringements of patents or other rights of third parties.

#### **Copyright Notice**

Copyright, 2006 Silicon Motion, Inc. All rights reserved. No part of this publication may be reproduced, photocopied, or transmitted in any form, without the prior written consent of Silicon Motion, Inc. Silicon Motion, Inc. reserves the right to make changes to the product specification without reservation and without notice to our users

Microsoft®, Windows®, Windows NT®, and Direct3D® are registered trademarks or trademarks of Microsoft Corporation.

Macrovision®: This product incorporates copyright protection technology that is protected by U.S. patents and other intellectual property rights. Use of this copyright protection technology must be authorized by Macrovision, and is intended for home and other limited pay-per-view uses only unless otherwise authorized by Macrovision. Reverse engineering or disassembly is prohibited

| Version Number | Date    | Note                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1            | 1/23/01 | <ul> <li>Changed External Display Memory Interface &amp; Video Port Interface in Figure 4 on page 5-2</li> <li>Updated in conformance to the Addendum 0.5. Changed FPR33[6] to be Hitachi 24-bit TFT only</li> </ul>                                                                                                                           |

| 0.2            | 1/30/01 | General revision based on Engineering inputs and verification results.                                                                                                                                                                                                                                                                         |

| 0.3            | 2/8/01  | <ul> <li>Changed Power-on Configuration Register bits [27, 25, 24, 2, 1, 0] to reserved</li> <li>Deleted Flat Panel Interface Pins [FPDATA35-FPDATA24]</li> <li>Added definition to register CRT36 bit 2.</li> <li>Changed register MCR62 bit [3:0] to reserved</li> <li>Changed tables in Electrical Specifications chapter to TBD</li> </ul> |

| 0.4            | 5/1/01  | <ul> <li>Added Ordering Information table</li> <li>Added Appendix H</li> <li>Revised Pin List</li> <li>Changed Block Diagram</li> </ul>                                                                                                                                                                                                        |

| 0.5            | 5/30/01 | Added DC operating voltages to Electrical Specification chapter                                                                                                                                                                                                                                                                                |

| 0.6            | 6/29/01 | Changed pin J9 from MVDD to VSS                                                                                                                                                                                                                                                                                                                |

| 0.7            | 8/15/01 | Changed Electrical Specification chapter                                                                                                                                                                                                                                                                                                       |

| 0.8            | 5/21/02 | <ul> <li>Changed Memory Mapped Address Diagram</li> <li>Changed Table 9 - ZV Port (Input mode) column</li> </ul>                                                                                                                                                                                                                               |

| 1.0            | 5/24/06 | Removed page 28-2 (Ordering information)                                                                                                                                                                                                                                                                                                       |

## **Table of Contents**

| Chapter 1: Overview                               |                     |

|---------------------------------------------------|---------------------|

| Overview of Major System Blocks                   | . 1-4               |

| Chapter 2: Pins                                   |                     |

| Lynx3DM+ Pin Descriptions                         | . 2-1               |

| Lynx3DM+ NAND Tree Scan Testing                   |                     |

| General Information                               |                     |

| NAND Tree Simulation                              |                     |

| Lynx3DM+ Power-On Configurations                  |                     |

| Chapter 4: PCI/AGP Bus Interface                  | . ა-ა<br><b>⊿₋1</b> |

| PCI Configuration Registers                       |                     |

| Chapter 5: Display Memory Interface               | . 5-1               |

| Memory Configuration                              |                     |

| Page Break Look Ahead                             |                     |

| Memory Timing Control                             | . 5-1               |

| Chapter 6: Drawing Engine                         | . 6-1               |

| Chapter 7: Video Processor                        | . 7-1               |

| Chapter 8: Zoom Video Port and Video Capture Unit | . 8-1               |

| Zoom Video Port                                   | . 8-1               |

| Video Capture Unit                                |                     |

| Functional Description                            | . 8-3               |

| Theory of Operation                               | . 8-4               |

| Lynx3DM+ Flat Panel Enhancements                  |                     |

| Lynx3DM+ Flat Panel Enhancements                  |                     |

| Lynx3DM+ Graphics/Text Expansion Information      |                     |

| Introduction                                      |                     |

| Horizontal Expansion for Text and Graphics        | . 9-1               |

| Vertical Expansion for Text and Graphics          |                     |

| LCD Dithering Engine                              | . 9-3               |

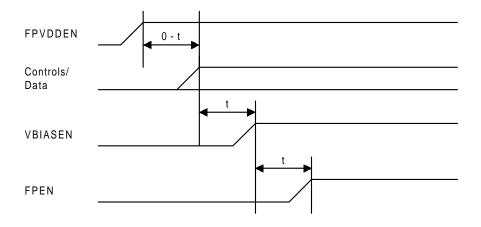

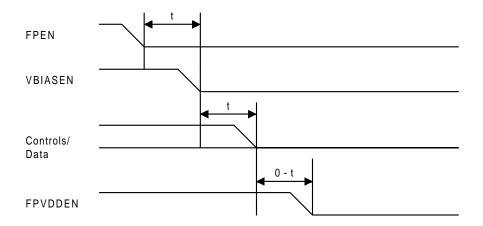

| Flat Panel Power ON/OFF Sequencing                | . 9-3               |

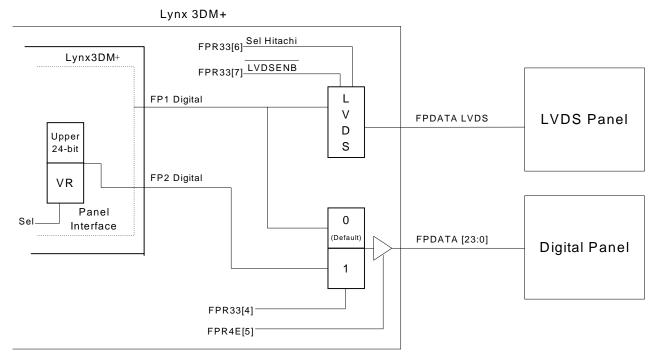

| Lynx3DM+ Dual Digital LCD Support                 | . 9-4               |

| Lynx3DM+ Flat Panel Interface Connections         |                     |

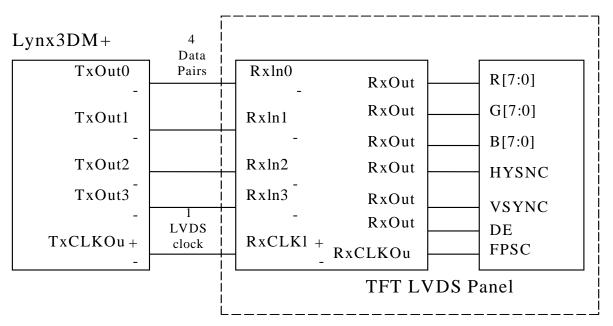

| Integrated LVDS Chipset Interface                 | 9-11                |

| Video BIOS ROM Interface                          |                     |

| VESA DPMS Interface                               |                     |

| I2C Bus or VESA DDC2B Interface                   |                     |

| Chapter 11: Clock Synthesizers                    |                     |

| Chapter 12: Multimedia RAMDAC                     |                     |

| LCD Backend RAM (RAM1)                            |                     |

| Chapter 13: Signature Analyzer                    |                     |

| Chapter 14: Power Management                      |                     |

| ACPI                                              |                     |

| Adaptive Power Management                         |                     |

| Dynamic Control of Functional Blocks              |                     |

| Dynamic Clock Control and Virtual Refresh         | 14-2                |

| Standard Power Management                         | 14-2                |

| Standby Mode                                      | 14-2                |

| Power Saving In Standby Mode                      |                     |

| Sleep Mode                                        | 14-3                |

| Power-down Sleep Mode States                      |                     |

| Chapter 15: Motion Compensation Specification     | 15-1                |

**Table of Contents**

| Overview                                                      | 15-1                  |

|---------------------------------------------------------------|-----------------------|

| Data Flow and External System Responsibilities                |                       |

| MC Top Level Architecture                                     |                       |

| MC Instruction Format and Operation                           |                       |

| Chapter 16: 3D Engine                                         |                       |

| IEEE 754 Floating Point Setup Engine                          |                       |

| Triangle Engine                                               |                       |

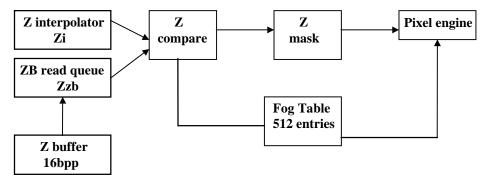

| Z Engine                                                      |                       |

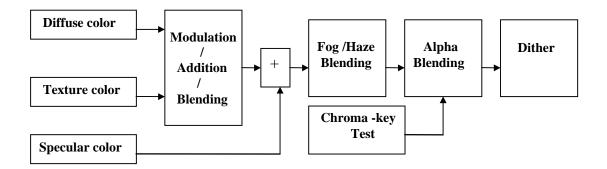

| Pixel Engine                                                  |                       |

| Modulation/Addition Unit                                      |                       |

| Fog Blending Unit                                             | 16-4                  |

| Chroma-Key Test Unit                                          | 16-4                  |

| Alpha Blending Unit                                           | 16-4                  |

| Chapter 17: TV Encoder                                        |                       |

| Function Descriptions                                         |                       |

| Macrovision Antitaping process                                | 17-3                  |

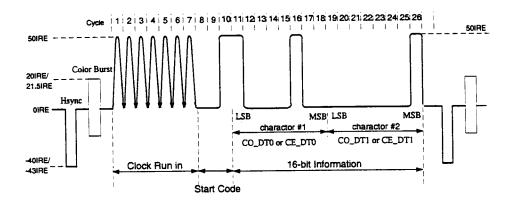

| Closed Captioning                                             | 17-4                  |

| Video data output and Over-sampling.         Synchronization. | 17-5<br>17 <b>-</b> 5 |

| Sub-carrier Generation                                        | 17-5                  |

| Parallel bus I/F                                              | 17-5                  |

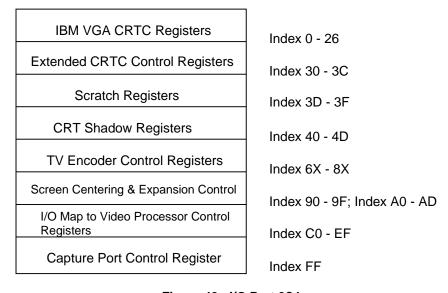

| Chapter 18: Register Overview & Usage                         |                       |

| PCI Configuration Registers                                   | 18-1                  |

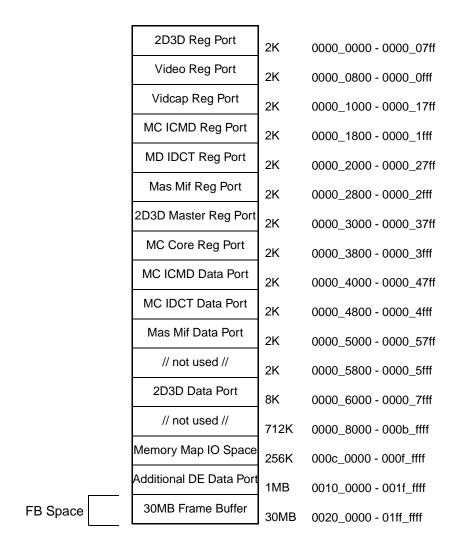

| Memory Mapped Registers                                       |                       |

| Chapter 19: PCI Configuration Space Registers                 | 19-1                  |

| PCI Configuration Space Registers                             | 19-2                  |

| Extended SMI Registers                                        | 19-10                 |

| Chapter 20: Standard VGA Registers                            |                       |

| Standard VGA Registers                                        |                       |

| Sequencer Register                                            | 20-5                  |

| CRTC Controller Registers                                     | 20-8                  |

| Graphics Controller Řegisters                                 |                       |

| Attribute Controller Registers                                | 20-25                 |

| Chapter 21: Extended SMI Registers                            | 20-28                 |

| Extended SMI Registers                                        |                       |

| System Control Registers                                      | 21-6                  |

| Power Down Control Registers                                  | 21-13                 |

| Flat Panel Registers                                          | 21-18<br>21-30        |

| Clock Control Registers                                       |                       |

| General Purpose Registers                                     | 21-48                 |

| Pop-up Icon and Hardware Cursor Registers                     | 21-51                 |

| Pop-up Icon Registers                                         | 21-52<br>21-55        |

| Extended CRT Control Registers                                | 21-57                 |

| Shadow VGA Registers                                          | 21-67                 |

| Automatic Lock/Unlock Scheme for Shadow Registers             | 21-67                 |

| Chapter 22: 2D & Video Registers                              |                       |

| Video Processor Control Registers                             |                       |

| Capture Processor Control Registers                           | 22-45                 |

| Chapter 23: Motion Comp Video Registers                       |                       |

| Motion Comp Bus Master CMD Control Registers                  | 23-2                  |

| Motion Compensation ICMD Control Registers                    |                       |

| would compensation towic control registers                    | ∠4-∠                  |

iv Table of Contents

| Silicon  | Motion <sup>®</sup> . | Inc   |

|----------|-----------------------|-------|

| SIIICULI | IVIOLIOII .           | IIIC. |

## Lynx3DM+

|                                                     | Databook |

|-----------------------------------------------------|----------|

| Motion Compensation IDCT Control Registers          | 24-4     |

| Host Master Control Registers                       | 24-6     |

| Texture 3D Bus Master Control Registers             | 24-9     |

| Chapter 25: 3D Registers                            |          |

| 2D3D DMA Registers                                  | 25-16    |

| Register Descriptions                               |          |

| Common Register                                     |          |

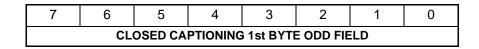

| Closed Captioning Registers                         | 26-2     |

| Chapter 27: Electrical Specifications               | 27-1     |

| Absolute Maximum Ratings                            |          |

| DC Specifications                                   | 27-1     |

| AC Specifications                                   | 27-4     |

| AC Timing Specifications                            |          |

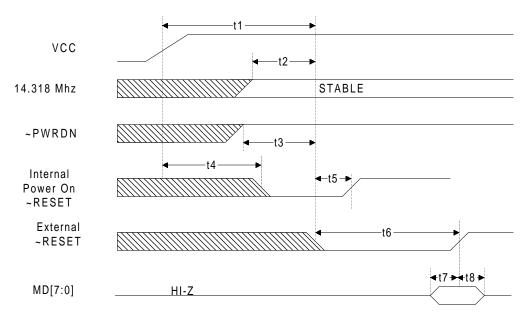

| Power On Reset                                      | 27-6     |

| AGP BUS Cycles                                      | 27-7     |

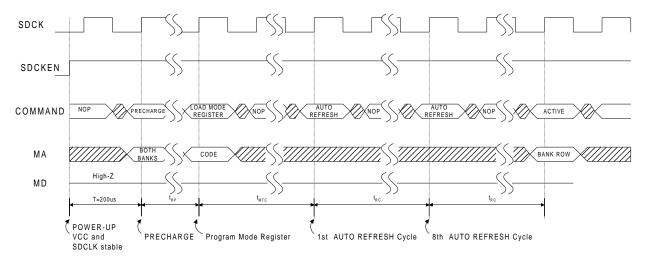

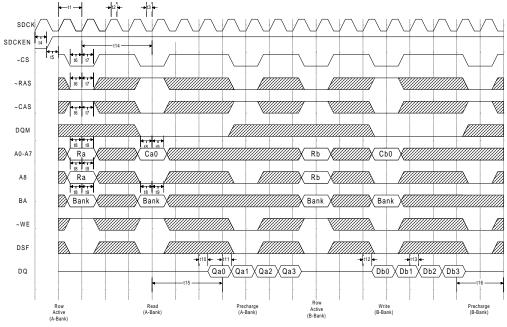

| Synchronous DRAM (SDRAM) and SGRAM Cycles           | 27-9     |

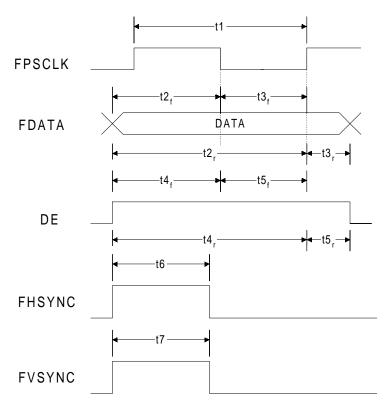

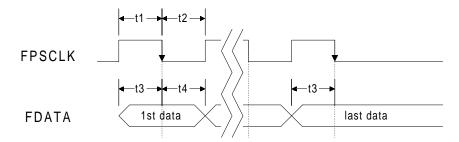

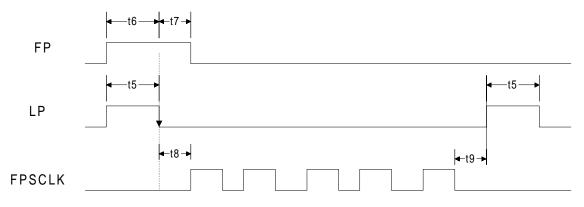

| Flat Panel Interface Cycle Timing                   | 27-10    |

| Chapter 28: Mechanical Dimensions                   |          |

| Appendix A: Video Modes                             |          |

| Standard IBM Compatible VGA Modes                   | A-1      |

| VESA Super VGA Modes                                | A-2      |

| 640 by 480 Resolution Modes                         |          |

| 800 by 600 Resolution Modes                         | A-3      |

| 1024 by 768 Resolution Modes                        | A-4      |

| 1280 by 1024 Resolution Modes                       | A-4      |

| Appendix B: Popup Icon Consideration                |          |

| Introduction                                        |          |

| Popup Icon                                          | B-1      |

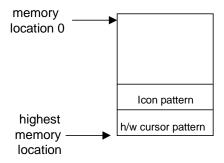

| Icon Pattern Memory Location                        |          |

| Icon Pattern                                        |          |

| Icon Control                                        |          |

| Appendix C: SMI Handler Programming Consideration   | C-1      |

| Introduction                                        |          |

| Background                                          |          |

| System BIOS Consideration                           | C-1      |

| Int10 Vector Entry                                  | C-1      |

| Alternate INT10 Entry                               |          |

| Appendix D: Programming USR [3:0] Pins              |          |

| Application Notes for control of USR [3:0] Pins     |          |

| Appendix E: Monitor & TV Defect                     |          |

| CRT Monitor Detect                                  |          |

| Appendix F: CRT Timing Register Summary             | F-1      |

| CRT Timing Register Summary                         |          |

| Appendix G: 2D/3D Bus Master DMA Data Stream Format | G-1      |

| 2D3D Bus Master - DMA Data Stream Format            |          |

| Appendix H: Lynx3DM+ New Features                   |          |

| Introduction                                        | H-1      |

| New Feature                                         | H-1      |

| New Registers                                       | H-1      |

| Lynx3DM+ Pin Descriptions                           |          |

| Index                                               | I-1      |

Table of Contents

## **List of Figures**

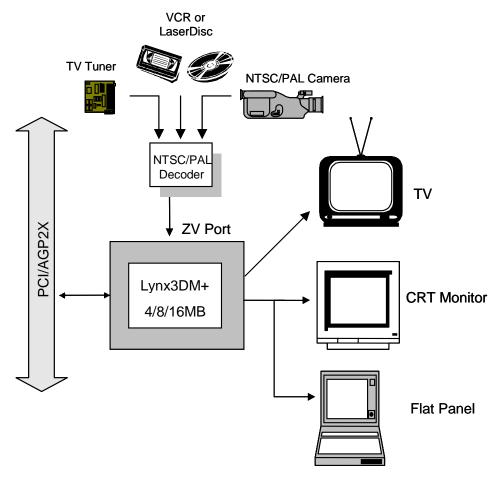

| Figure 1.  | System Block Diagram for Lynx3DM+             | 1-2  |

|------------|-----------------------------------------------|------|

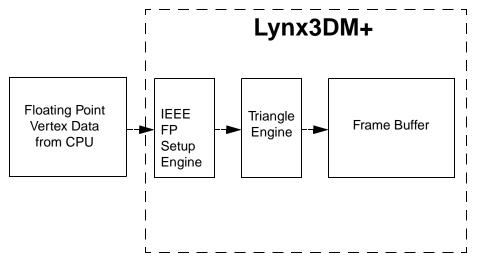

| Figure 2.  | Top Level 3D Flow Diagram                     | 1-5  |

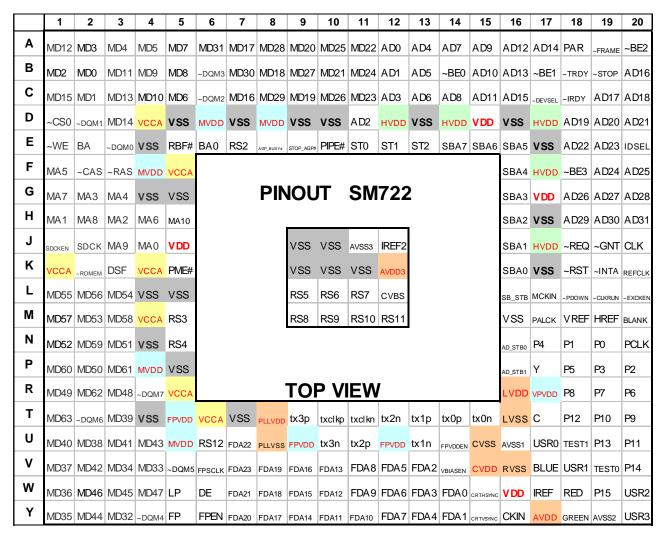

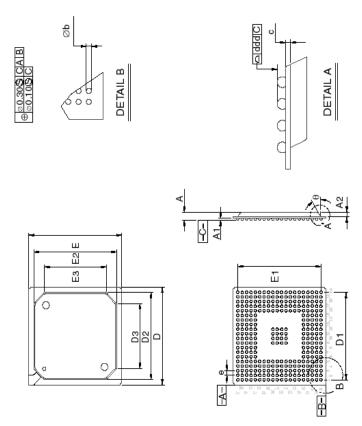

| Figure 3.  | SM722/723 Pin Diagram for 316 BGA Package     | 2-7  |

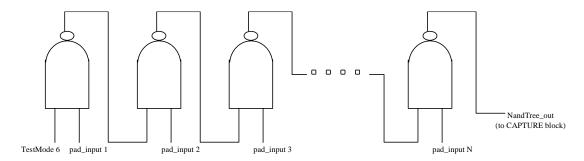

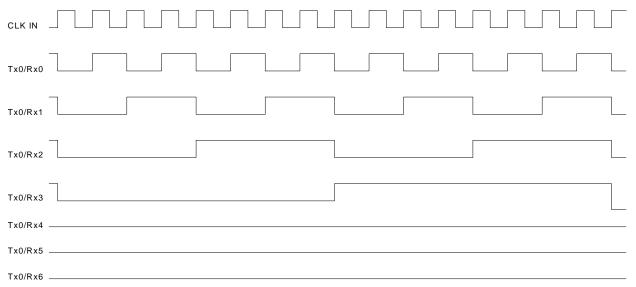

| Figure 4.  | NAND Tree Connection                          | 2-17 |

| Figure 5.  | NAND Tree Simulation Timing Diagram           | 2-17 |

|            | SGRAM Power-Up and Initialization Sequence    |      |

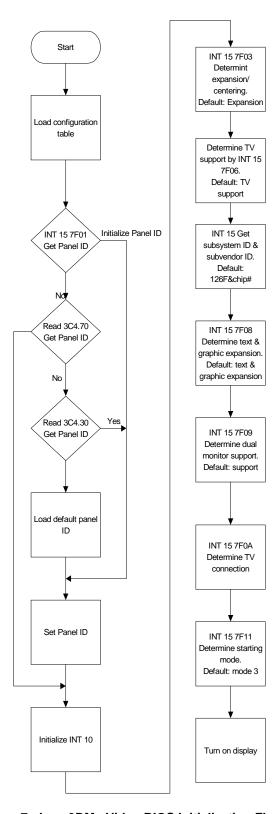

| Figure 7.  | Lynx3DM+ Video BIOS Initialization Flow       | 3-2  |

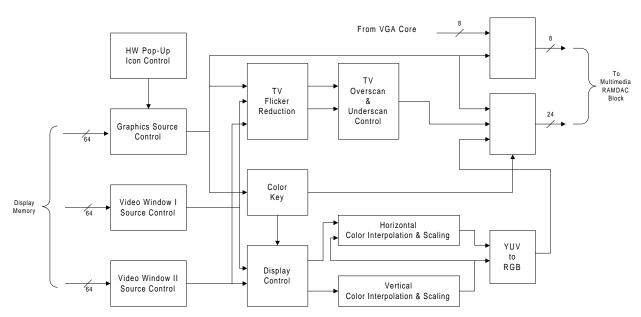

| Figure 8.  | Video Processor Block Diagram                 | 7-1  |

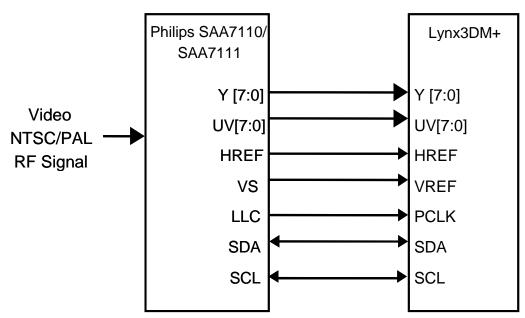

|            | Video Encoder Interface via Video Port        |      |

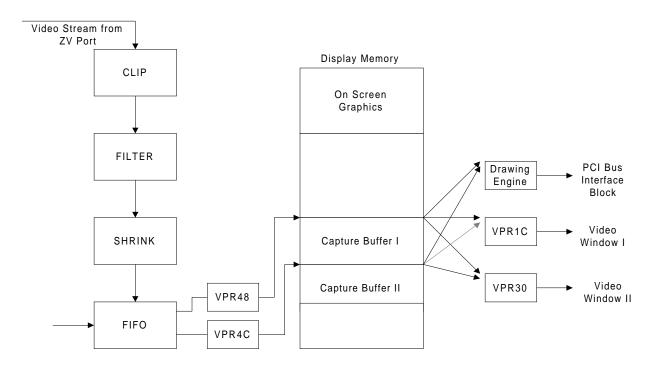

| Figure 10. | Video Capture Block Diagram                   | 8-3  |

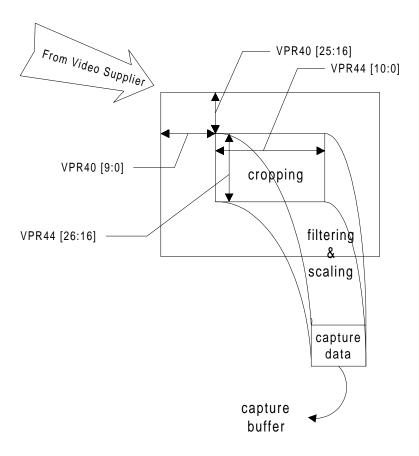

| Figure 11. | Video Capture Data Flow                       | 8-4  |

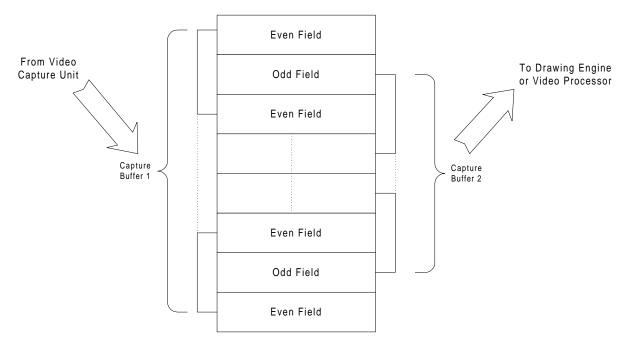

| Figure 12. | Capture Buffer Structure in Interlaced Mode   | 8-7  |

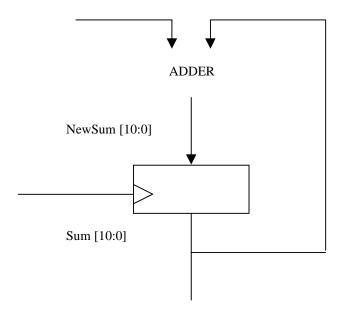

| Figure 13. | DDA Expansion Algorithm                       | 9-2  |

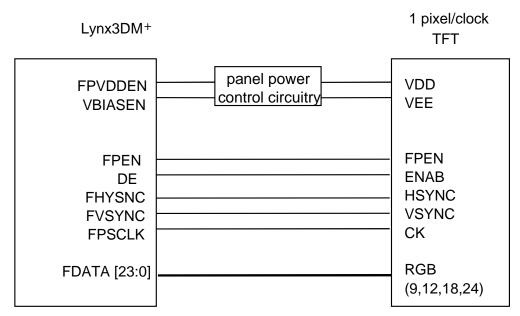

| Figure 14. | TFT (Single Pixel/Clock) Interface Diagram    | 9-7  |

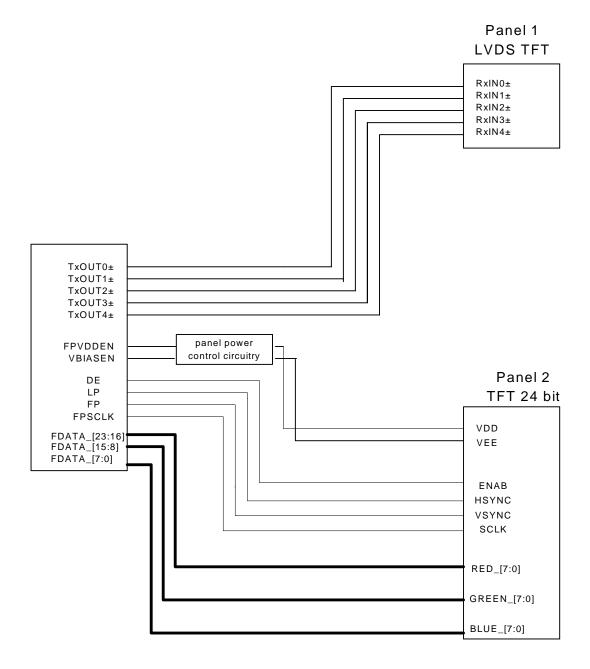

|            | TFT Two Panel Interface Diagram               |      |

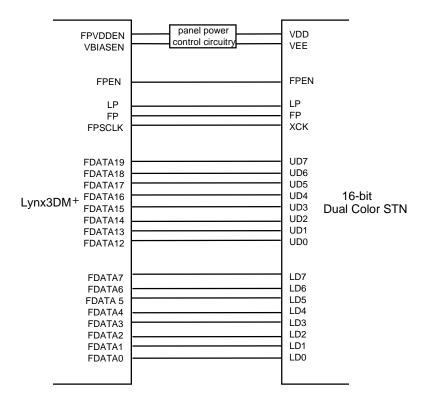

| Figure 16. | 16-bit DSTN Interface Configuration           | 9-9  |

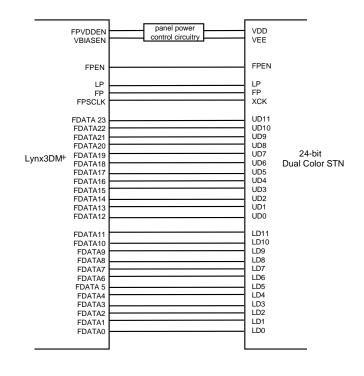

| Figure 17. | 24-bit Dual Color STN Interface Diagram       | 9-9  |

| Figure 18. | Panel Power On Sequencing Timing Diagram      | 9-10 |

| Figure 19. | Panel Power Off Sequencing Timing Diagram     | 9-10 |

| Figure 20. | LVDS Interface with TFT LVDS Panel            | 9-11 |

|            | Lynx 3DM+ Internal LVDS Panel Interface       |      |

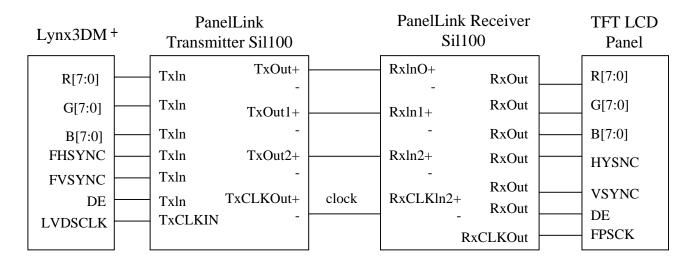

| Figure 22. | PanelLink Interface with TFT LCD Panel        | 9-12 |

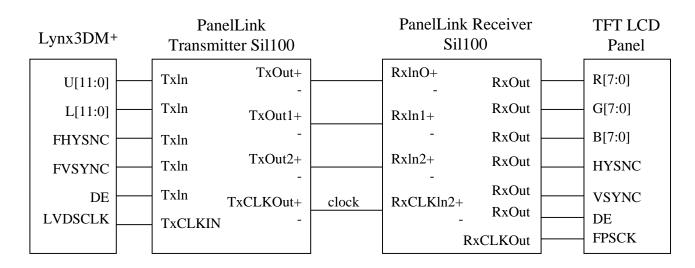

| Figure 23. | PanelLink Interface with DSTN LCD Panel       | 9-13 |

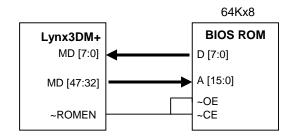

| Figure 24. | Video BIOS ROM Configuration Interface        | 10-1 |

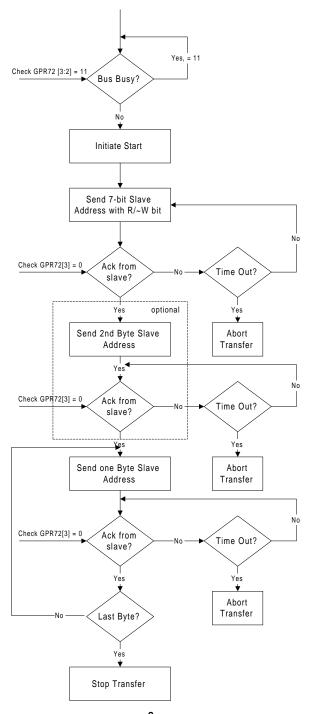

| Figure 25. | Lynx3DM+ I2C Bus Protocol Flow Chart          | 10-3 |

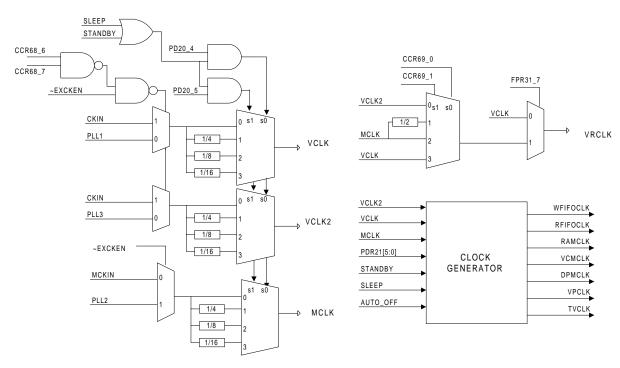

| Figure 26. | Clocks Generator Block Diagram                | 11-1 |

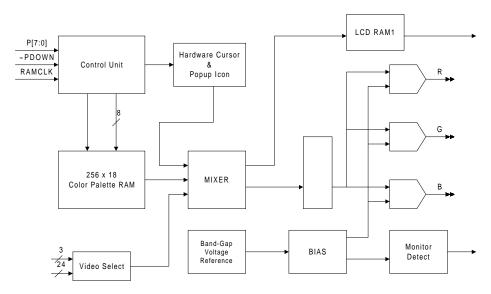

| Figure 27. | Lynx3DM+ RAMDAC Block Diagram                 | 12-1 |

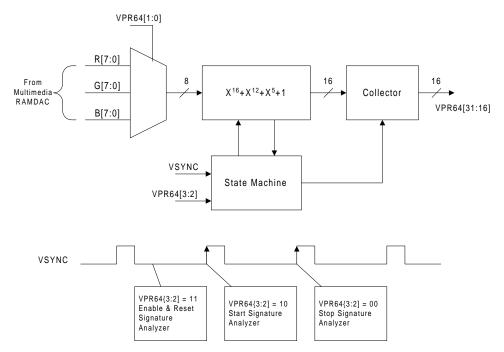

| Figure 28. | Signature Analyzer Block Diagram              | 13-1 |

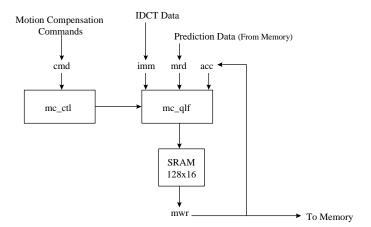

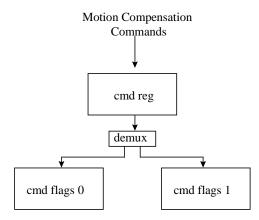

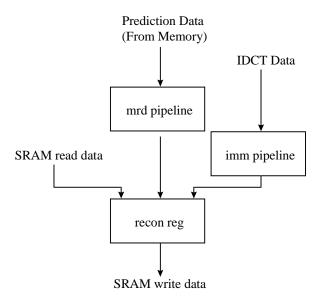

| Figure 29. | MC Top Level Architecture                     | 15-2 |

| Figure 30. | Control Block Diagram                         | 15-2 |

|            | QLF Block Diagram                             |      |

|            | End Stream Instruction                        |      |

| Figure 33. | MC Instruction Format                         | 15-4 |

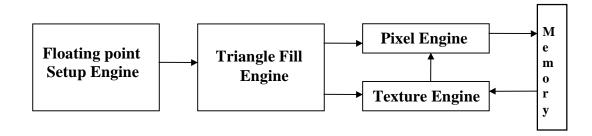

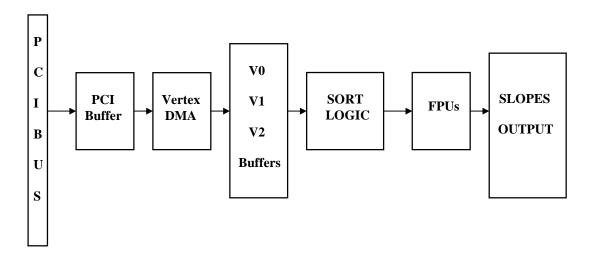

| Figure 34. | 3D Engine Block Diagram                       | 16-1 |

|            | Setup Engine Block Diagram                    |      |

|            | Triangle engine block diagram                 |      |

|            | Z Engine Block Diagram                        |      |

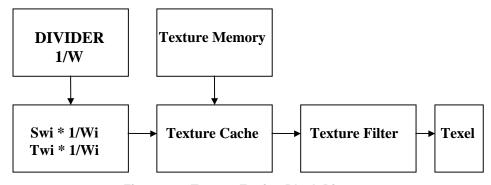

|            | Texture Engine Block Diagram                  |      |

|            | Pixel pipeline block diagram                  |      |

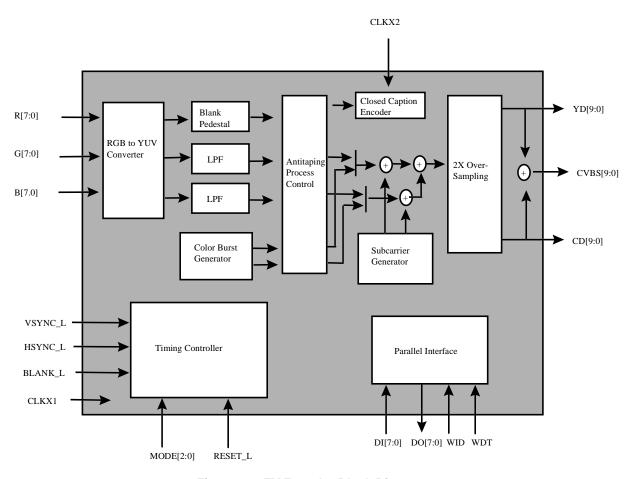

| -          | TV Encoder Block Diagram                      |      |

| •          | I/O Port 3C4                                  |      |

| 0          | I/O Port 3?4                                  |      |

|            | Memory Mapped Address Diagram                 |      |

| •          | Memory Mapped Address Diagram                 |      |

|            | 16 Grayscale Pattern                          |      |

|            | Power-on Reset and Reset Configuration Timing |      |

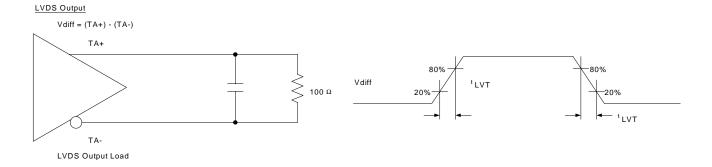

|            | LVDS Transmitter Device Transition Times      |      |

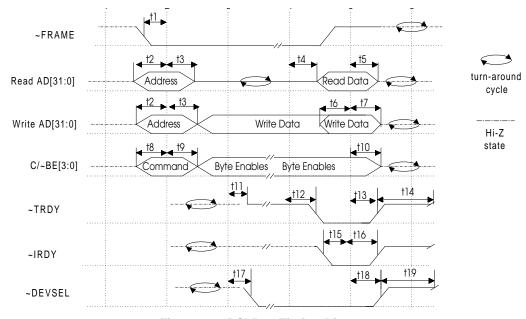

|            | PCI Bus Timing Diagram                        |      |

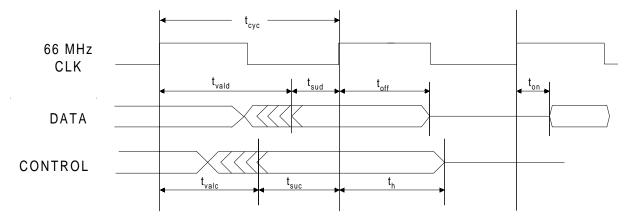

| Figure 49. | AGP Bus Timing Diagram                        | 27-7 |

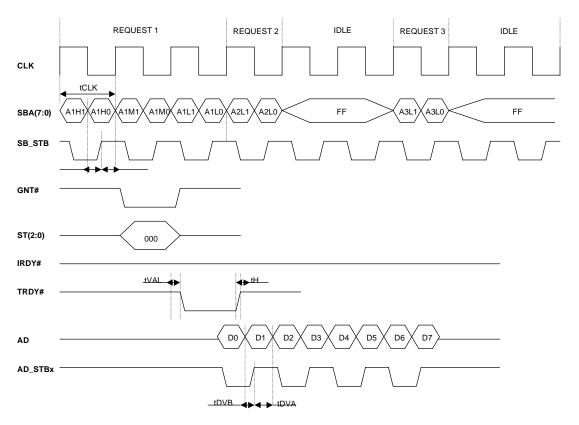

| Figure 50. | AGP 2X Read Request with Return Data (4Qw)     | 27-8  |

|------------|------------------------------------------------|-------|

| Figure 51. | SDRAM/SGRAM Read and Write Cycles              | 27-9  |

| Figure 52. | TFT Interface Timing                           | 27-10 |

| Figure 53. | DSTN Interface (Clock and Data) Timing         | 27-11 |

| Figure 54. | DSTN Interface (Control and Clock) Timing      | 27-11 |

| Figure 55. | 316 BGA Mechanical Dimensions                  | 28-1  |

| Figure 56. | Hardware Cursor and Popup Icon Memory Location | B-1   |

viii List of Figures

## **List of Tables**

| Table 1.               | Lynx3DM+ (4MB): Display Support Modes                              | 1-9  |

|------------------------|--------------------------------------------------------------------|------|

| Table 2.               | Lynx3DM+ (8MB): Display Support Modes                              | 1-10 |

| Table 3.               | Lynx3DM+ (16MB): Display Support Modes                             | 1-11 |

| Table 4.               | Pin Description                                                    |      |

| Table 5.               | Numerical SM722 BGA Pin List                                       | 2-8  |

| Table 6.               | Lynx3DM+ VCC and GROUND Connections                                | 2-16 |

| Table 7.               | NAND Tree Scan Test Order                                          | 2-17 |

| Table 8.               | Power-On Configurations                                            |      |

| Table 9.               | Lynx3DM+ Video Port Interface I/O Compliance                       |      |

| Table 10.              | Bit Setting Summary for Video Capture                              |      |

| Table 11.              | Flat Panel Interface Pins listing for color DSTN and color TFT LCD |      |

| Table 12.              | Dual Panel Interface (One Digital Panel and One LVDS Panel)        |      |

| Table 13.              | LVDS Transmitter Pin Mapping for TFT Interface                     |      |

| Table 14.              | PanelLink Transmitter Pin Mapping for TFT Interface                |      |

| Table 15.              | DPMS Summary                                                       |      |

| Table 16.              | Recommended VNR and VDR Values for Common VCLK Settings            |      |

| Table 17.              | Interface Signals Sleep Mode States                                |      |

| Table 18.              | Instruction Flags and Parameters                                   |      |

| Table 19.              | TV Encoder Block Interface Description                             |      |

| Table 20.              | TV Encoder Sampling Rates                                          |      |

| Table 21.              | Closed Captioning Lines                                            |      |

| Table 22.              | Closed Captioning Odd Field Output Data                            |      |

| Table 23.              | Closed Captioning Even Field Output Data                           |      |

| Table 24.              | PCI Configuration Registers Quick Reference                        |      |

| Table 25.              | Standard VGA Registers Quick Reference                             |      |

| Table 26.              | Extended SMI Registers Quick Reference                             |      |

| Table 27.              | Memory Mapped Registers Quick Reference                            |      |

| Table 28.              | Motion Comp Video Registers Quick Reference                        |      |

| Table 29.              | PCI Bus Master Control Registers Quick Reference                   |      |

| Table 30.              | Summary of Registers                                               |      |

| Table 31.              | 3D Registers Quick Reference                                       |      |

| Table 32.              | TV Encoder Registers Quick Reference                               |      |

| Table 33.              | Absolute Maximum Ratings                                           |      |

| Table 34.              | Digital DC Specification                                           |      |

| Table 35.              | Recommended DC Operating Voltages                                  |      |

| Table 36.              | LVDS Specifications                                                |      |

| Table 37.              | RAMDAC CharacteristicsRAMDAC/Clock Synthesizer DC Specifications   |      |

| Table 38.              |                                                                    |      |

| Table 39.<br>Table 40. | RAMDAC AC Specifications                                           |      |

| Table 40.              | Switching Characteristics                                          |      |

| Table 41.              | PCI Bus Timing (33 MHz)                                            |      |

| Table 42.              | AGP 1X mode BUS Timing                                             |      |

|                        | · · · · · · · · · · · · · · · · · · ·                              |      |

| Table 44.<br>Table 45. | AGP 2X Timing ParametersSDRAM/SGRAM Memory Read Timing             |      |

| Table 45.              | Color TFT Interface Timing                                         |      |

| Table 40.              | Color DSTN Interface Timing                                        |      |

| Table 47.              | Standard IBM Compatible VGA Modes                                  |      |

| Table 49.              | VESA Super VGA Modes.                                              |      |

|                        |                                                                    |      |

List of Tables ix

| Silicon Motion <sup>®</sup> , Inc. |                                            | Lynx3DM+<br>Databook |  |

|------------------------------------|--------------------------------------------|----------------------|--|

| Table 50.                          | Low Resolution Modes                       | A-2                  |  |

| Table 51.                          | 640 x 480 Extended Modes                   | A-3                  |  |

| Table 52.                          | 800 x 600 Extended Modes                   | A-3                  |  |

| Table 53.                          | 1024 x 768 Extended Modes                  | A-4                  |  |

| Table 54.                          | 1280 x 1024 Extended Modes                 | A-4                  |  |

| Table 55.                          | CRT Timing and LCD Shadow Register Summary | F-1                  |  |

| Table 56.                          | New Pin Descriptions for Lynx3DM+          | H-3                  |  |

| Table 57.                          | Numerical SM722 BGA Pin List               |                      |  |

x List of Tables

Silicon Motion®, Inc.

### **Chapter 1: Overview**

The Lynx3DM+ is a power managed, desktop equivalent display controller for notebook PCs. This device delivers full featured 3D, a unique memory architecture designed to enhance 3D/2D performance, enhanced multi-display capabilities, and Motion Compensation for DVD.

The Lynx3DM+ incorporates an IEEE Floating Point Setup engine as well as a full featured 3D rendering engine. The setup engine is designed to balance with the triangle delivery capabilities of high end notebook processors. The rendering engine supports key features such as Mip Mapping, Alpha Blend, Anti-Aliasing, Specular Highlights and Fog.

The Lynx3DM+ integrates 4MB, 8MB or 16MB of video memory. This allows up to a 64-bit memory interface and over 1.0GB/s of memory bandwidth.

Lynx3DM+ continues to support all the Dual Application/Dual View capabilities of its predecessor, LynxE. In addition, Lynx3DM+ can drive two independent digital displays, as well as simultaneously drive LCD, CRT and TV displays (multiview). Support for all of these features is provided under Windows 95, Windows 98, Windows Me, Windows NT 4.0, and Windows 2000.

A robust 128-bit Drawing Engine provides no compromise 2D performance. The Drawing Engine supports 3 ROPs, BitBLT, transparent BLT, pattern BLT, color expansion, and line draw. The Host Interface Unit allows support for AGP and PCI. Support for all ACPI power states is provided. A high quality TV encoder, VGA Core, LCD Backend Controller and 200 MHz RAMDAC are incorporated as well.

The Lynx3DM+'s Motion Compensation block, Video Processor block, and Video Capture Unit provide superior video quality for real-time video playback and capture. When combined with high end notebook CPUs, the Motion Compensation block allows full frame playback of DVD video content without the need for additional hardware. The Video Processor supports multiple independent full screen, full motion video windows with overlay. Each motion video window uses hardware YUV-to-RGB conversion, scaling, and color interpolation. When combined with multi-view capabilities of the chip, these independent video streams can be output to each of two display devices and bilinear scaled to support applications such as full screen display of local and remote images for video conferencing.

Lynx3DM+ is designed with 0.25m, 2.5V CMOS process technology. A hierarchical layout approach provides enhanced internal timing control. In addition to built-in test modes and a signature analyzer, the Lynx3DM+ incorporates a 20 bit test bus which can be used to simultaneously monitor internal signals through the Zoom Video (ZV) Port Interface. The capability can be used to increase fault coverage, and to reduce silicon validation and debugging time. The Lynx3DM+ is available in a 316 pin BGA packages.

Overview 1 - 1

Figure 1: System Block Diagram for Lynx3DM+

| Features                                                                                                                | Benefits                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| High performance, power managed 3D                                                                                      | Desktop level 3D performance within the power budget of a notebook system                                                                                |

| Motion Compensation                                                                                                     | Allows full frame playback of DVD content in software                                                                                                    |

| Multi-Display support under Microsoft Windows 95, Windows NT, Windows 98 and Windows Me with one device                 | <ul> <li>Applications available at the same time across multiple display devices</li> <li>Single chip implementation ideal for mobile systems</li> </ul> |

| SMI Dual View support under Microsoft Windows 95, Windows NT, Windows 98 and Windows Me                                 | Any rectangular portion of primary display can be zoomed up for display on multiple secondary displays                                                   |

| Dual-Digital support                                                                                                    | Independent display support for external digital LCD monitor or LCD projector                                                                            |

| Adaptive Power Management  Dynamic functional block shut-down, clock control                                            | Reduce average power consumption when in operation mode                                                                                                  |

| Multiple independent hardware video windows                                                                             | <ul> <li>Independent full screen, motion video for separate displays.</li> <li>Complete dual view support for video</li> </ul>                           |

| 128-bit, single clock cycle Drawing Engine                                                                              | No compromise 2D graphics performance for mobile systems                                                                                                 |

| High performance memory interface                                                                                       | Delivers over 1.0GB/s bandwidth to support 3D graphics, DVD                                                                                              |

| AGP 2X sideband and PCI 2.1 support                                                                                     | Provides interface capability for today's most popular PC graphics busses                                                                                |

| DSTN and TFT panel support up to 1280x1024                                                                              | Supports all panel requirements for mobile systems                                                                                                       |

| Integrated TV Encoder with Macrovision                                                                                  | Graphics/video display on TV with no external support logic                                                                                              |

| Zoom Video Port                                                                                                         | Provides support for camera, TV tuner input, or output to VCR                                                                                            |

| Hardware support for LCD landscape/portrait rotation                                                                    | Portrait view for desktop publishing, word processing applications                                                                                       |

| PC2001 Compliant, ACPI Compliant                                                                                        | Meets WHQL certification requirements                                                                                                                    |

| SW support for Microsoft Windows 95, Microsoft Windows NT 4.0, Microsoft Windows 98, Windows Me, Windows 2000, and OS/2 | Complete OS software support                                                                                                                             |

Microsoft, Windows, Windows NT, and Direct3D are registered trademarks or trademarks of Microsoft Corporation.

Regarding Macrovision: This product incorporates copyright protection technology that is protected by U.S. patents and other intellectual property rights. Use of this copyright protection technology must be authorized by Macrovision, and is intended for home and other limited pay-per-view uses only unless otherwise authorized by Macrovision. Reverse engineering or disassembly is prohibited.

Overview 1 - 3

#### **Overview of Major System Blocks**

The Lynx3DM+ consists of a logic block which interfaces to a 4MB, 8MB or 16MB block of integrated memory. The integrated memory supports single clock cycle transfers up to 100MHz. Peak memory bandwidth for the integrated 128-bit memory bus is over 1.6GB/s.

The logic within the Lynx3DM+ consists of 11 functional blocks: PCI Interface, Host Interface (HIF), Memory Controller, Drawing Engine, Power Down Control Unit, Video Processor, Video Capture Module, LCD Backend Controller, VGA Core, PLL Module, and RAMDAC. A summary of each of the functional blocks, along with important features follows:

#### AGP/PCI Interface and HIF

Lynx3DM+'s PCI Host Interface Unit supports burst read, burst write, and bus master mode with DMA. The Host Interface Unit decodes I/O read, I/O write, memory read, memory write, memory mapped access, 2D/3D Drawing Engine access, VGA access, and others. The unit also supports Little-Endian and Big-Endian format, and 8-bit ROM decode for on board video BIOS ROM. A dual aperture feature is designed to support VGA modes and non-VGA modes. In addition, a special VGA aperture function is added to allow 64-bit memory access in VGA modes.

Lynx3DM+ has an internal HIF (Host Interface) bus which is designed to transfer data between PCI Host Interface Unit and other functional blocks. The PCI Host Interface Unit controls the HIF bus protocol to effectively deliver PCI I/O and memory cycles to each functional block.

Lynx3DM+ supports 2X with sideband Accelerated Graphics Port (AGP). The AGP interface provides a high bandwidth, low latency connection to the system memory; therefore, it can increase the graphics performance for 2D and 3D applications.

#### Key Feature Summary:

- AGP 2X sideband support

- 33 MHz PCI Master/Slave interface

- PCI 2.1 compliant

- Dual aperture feature for concurrent VGA and video/drawing engine access

#### **Memory Controller**

Independent control is provided for the 4/8/16MB block of integrated memory. Page Break Look Ahead support assures a memory cycle is not broken if there is a change of memory bus agent within the same memory page. Programmable memory arbitration allows memory interface usage to be fully optimized - priority and round robin arbitration is supported. The block write function for SGRAM is supported.

#### Key Feature Summary:

- Independent memory interface control

- Up to 64-bit memory interface

- Over 1.0GB/s memory bandwidth

#### **Drawing Engine**

The Lynx3DM+'s 128-bit Drawing Engine is designed to accelerate 2D and 3D through APIs such as Direct Draw and Direct3D. The engine pipeline runs at a single clock per cycle at speeds of 100MHz+. The engine supports key GUI functions such as 3 operand ALU with 256 raster operations, pattern BLT, color expansion, trapezoid fill, and line draw. Direct3D rendering acceleration is provided by support for features such as arithmetic stretching, source transparent BLT, and double buffering.

1 - 4 Overview

#### Key Feature Summary:

- 100MHz single clock/cycle engine

- Designed to accelerate DirectDraw and Direct3D

#### 3D Engine

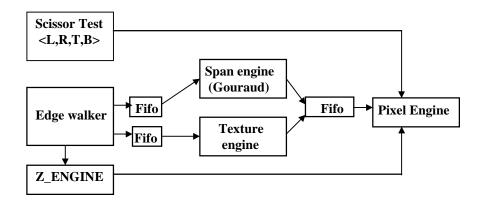

The Lynx3DM+ incorporates an IEEE Floating Point Setup engine as well as a full featured 3D rendering engine. The diagram below illustrates a top level diagram of the Lynx3DM+ setup and rendering pipeline.

Figure 2: Top Level 3D Flow Diagram

The setup engine is designed to balance with the triangle delivery capabilities of high-end notebook processors. The setup engine performs single precision floating point operations to calculate slope parameters (x, y, z; color - RGB, alpha; texture - s, t, perspective) from the triangle vertex data delivered from the CPU. The slope information is derived with sub-pixel accuracy to eliminate misalignment. The rendering engine utilizes the slope information to render the defined triangle to the screen. The rendering engine supports a full set of 3D rendering features. A representative list of features is provided in the Key Feature Summary below.

#### Key Feature Summary:

- IEEE Floating Point Setup Engine

- Complete 3D Rendering Engine set:

- Bi-linear and tri-linear filtering

- Mip Mapping

- Vertex and global fog

- Source and destination alpha blend

- Specular highlights

- Edge anti-aliasing

- Z-buffering

- Gouraud shading

- Mirrored textures

- -Texture decompression

#### **Motion Compensation Engine**

The Motion Compensation Engine offloads the motion compensation portion of the MPEG-2 decode process. This block can reduce CPU overhead requirements for MPEG-2 decode by 20%-40%, depending on CPU type and MPEG-2 data rate. To insure proper handling of MPEG-2 video data streams, the Lynx3DM+ implements a separate bus master control mechanism for motion compensation command and IDCT data. This approach allows for a dedicated pipeline through

Overview 1 - 5

which the motion compensation command and IDCT data can be transferred to the Motion Compensation Engine for processing.

The motion compensation block provides full sub-picture support as well. Both 2-bit/pixel formats and 8-bit/pixel formats (4-bit color data, 4-bit alpha data) are supported.

#### Key Feature Summary:

- Offloads motion compensation portion of MPEG-2 decode process from CPU

- Separate bus master control for motion compensation command and IDCT data

- Sub-picture support

- 2-bit/pixel format

- 8-bit/pixel format

#### **Digital TV-Encoder**

The TV Encoder is an NTSC/PAL Composite Video/S-video Encoder. It receives RGB inputs and converts to digital video signals based on CCIR 624 format.

The input video signal of the TV Encoder is RGB 8 bit each. The sampling rate is corresponding to CCIR 601, Square pixel and 4Fsc.

The output video signals of the TV Encoder are Composite Video signal and S-video signals of 10-bit each. These output signals are over-sampled by a double frequency clock called CLKX2. This feature helps for simplify external analog filtering.

The TV Encoder video timing is controlled by vertical sync and the horizontal sync input signals. The blank signal input is optional. If the blank signal input signal is pulled up, internal blanking control will be performed.

Macrovision 7.1.21 and closed captioning functions are included.

#### Key Feature Summary:

- NTSC/PAL interlace mode digital video encoder

- Composite Video and S-Video digital output

- CCIR 601, Square pixel and 4Fsc (NTSC only) resolution RGB input

- Interlace mode operation

- 2x over-sampling data output to simplify external analog filtering

- Macrovision function (version 7.1.21)

- Closed captioning function

#### **Power Down Control Unit**

The Power Down Control unit provides Dynamic Power Management for all functional blocks within the Lynx3DM+. Dynamic Power Management is made possible by individual clocking control to each of the functional blocks within Lynx3DM+. Each clock to a given functional block is skew matched to maintain synchronization between blocks. The functional blocks can then be turned on/off "on the fly" as needed. Power savings under fully operational conditions is maximized, yet the process completely transparent to the user.

Control for Virtual Refresh is provided through the Power Down Control unit as well. Through Virtual Refresh, LCD panel timing may be driven from a fully independent PLL. VCLK can be significantly reduced, while retaining full graphics performance. The result is significant power savings for LCD only configurations.

Finally, the Power Down Control unit generates power down sequencing for Standby and Suspend modes. Internal autostandby and system standby implementations are supported.

1 - 6 Overview

Under sleep mode, options for memory refresh type and use of internal PLL/external clock for memory refresh clock are provided. Activity detection is supported for resuming from Standby or Suspend modes.

#### Key Feature Summary:

- Dynamic Power Management

- Virtual Refresh

- Standby and Suspend model support

- ACPI, DPMS, APM compliant

#### **Video Processor**

The Video Processor module manages video playback to an LCD, CRT, or TV display. Independent video sources can be scaled up and displayed full screen different display devices - ideal for videoconferencing applications. The Video Processor module supports, bi-linear scaling, YUV to RGB color space conversion, color key, and overlay of graphics over video. The Video Processor module also supports flicker reduction and adjustable overscan/underscan for TV display.

#### Key Feature Summary:

- Multiple video windows in HW

- Independent video sources on different displays

- Bi-linear scaling

- Flicker filter and underscan for TV display

#### **Video Capture**

The Video Capture module processes incoming video data from the Zoom Video Port and sends the data to the local video frame buffer. From there, the data may be displayed, as well as bus mastered out for storage on a hard drive. Incoming data from the Zoom Video port can be interlaced or non-interlace and in YUV or RGB format. The data can be cropped, horizontally filtered (2,3,or 4-tap), and shrunk to ¼ size. Single buffer as well as double buffer capture is supported.

#### Key Feature Summary:

- Support for Zoom Video Port interface

- Crop, filter, shrink support

#### **LCD Backend Controller**

The LCD Backend Controller module manages data flow and generates timing to the selected LCD display. The module provides support for 9, 12, 18, 24 bit TFT and DSTN panels up to SXGA+ resolution. The backend controller contains a color encoder, dithering engines for TFT and DSTN panels, frame accelerator, and a Virtual Refresh timing generation block. Each of the blocks within the LCD Backend controller module can be powered down if not in use.

#### Key Feature Summary:

- TFT and DSTN support up to SXGA+

- Timing generation for Virtual Refresh

#### Popup Icon

The Lynx3DM+ support 64x64 popup icon which can be zoomed up by 2 to become 128x128 popup icon. The popup icon can be programmed to anywhere on the screen display. In addition, the popup icon has transparency support.

#### Key Feature Summary:

- Popup icon location flexible

- Transparency color support

#### **VGA** Core

The Lynx3DM+ has a high performance 32-bit VGA core which is 100% IBM VGA compatible. In addition to standard VGA functions, the Lynx3DM+'s VGA core module generates LCD timing, performs LCD screen autocentering and expansion, generates TV timing, and provides Hardware Cursor control.

Overview 1 - 7

#### Key Feature Summary:

• 100% IBM VGA compatible

#### **PLL Module**

The PLL module provides three separate PLLs for MCLK, VCLK, and Virtual Refresh clock to drive LCD panel timing. A 14.318MHz base clock is used to drive TV timing. This allows for completely independent timing for LCD/CRT or LCD/TV under dual application or dual view. For instance, the LCD panel can be driven at 60Hz while CRT refresh is 85Hz.

#### Key Feature Summary:

Separate PLL for LCD panel timing

#### **RAMDAC**

The integrated RAMDAC supports pixel clock frequencies up to 200MHz. Anti-sparkle logic is provided for read/writes to the palette. An internal band gap voltage reference saves need for external RC components.

#### Key Feature Summary:

200MHz speed provides support for popular LCD panels.

1 - 8 Overview

Table 1: Lynx3DM+ (4MB): Display Support Modes

| CRT Only           |                |             |        |        |  |

|--------------------|----------------|-------------|--------|--------|--|

| Dioplay Bookstien  | Defeate (III-) | Color Depth |        |        |  |

| Display Resolution | Refresh (Hz)   | 8 bpp       | 16 bpp | 24 bpp |  |

|                    | 60             | Х           | Х      | Х      |  |

| 640x480            | 75             | Х           | Х      | Х      |  |

|                    | 85             | Х           | Х      | Х      |  |

|                    | 60             | Х           | Х      | Х      |  |

| 800x600            | 75             | Х           | х      | Х      |  |

|                    | 85             | Х           | х      | Х      |  |

|                    | 60             | Х           | х      | Х      |  |

| 1024x768           | 75             | Х           | х      | Х      |  |

|                    | 85             | Х           | х      | Х      |  |

|                    | 60             | Х           | Х      | Х      |  |

| 1280x1024          | 75             | Х           | Х      | -      |  |

|                    | 85             | Х           | Х      | -      |  |

| LCD/Simultaneous Mode |              |             |        |        |  |

|-----------------------|--------------|-------------|--------|--------|--|

| Diamley Becalution    | Defrech (U-) | Color Depth |        |        |  |

| Display Resolution    | Refresh (Hz) | 8 bpp       | 16 bpp | 24 bpp |  |

| 640x480               | 60           | х           | Х      | Х      |  |

| 800x600               | 60           | х           | Х      | Х      |  |

| 1024x768              | 60           | х           | Х      | Х      |  |

| 1280x1024             | 60           | Х           | Х      | Х      |  |

|                | Dual Display Mode |                  |                         |                    |  |  |  |  |

|----------------|-------------------|------------------|-------------------------|--------------------|--|--|--|--|

| Diamley 4 (D4) | Diamley 2 (D2)    | Color Dept       | th (Max Color Depth Dis | splay 2 bpp)       |  |  |  |  |

| Display 1 (D1) | Display 2 (D2)    | when D1 is 8 bpp | when D1 is 16 bpp       | when D11 is 24 bpp |  |  |  |  |

|                | 640x480           | 24 (D2)          | 24 (D2)                 | -                  |  |  |  |  |

| 640x480        | 800x600           | 24               | 24                      | -                  |  |  |  |  |

| 040X460        | 1024x768          | 24               | 24                      | -                  |  |  |  |  |

|                | 1280x1024         | 16               | 16                      | -                  |  |  |  |  |

|                | 640x480           | 24               | 24                      | -                  |  |  |  |  |

| 900~600        | 800x600           | 24               | 24                      | -                  |  |  |  |  |

| 800x600        | 1024x768          | 24               | 24                      | -                  |  |  |  |  |

|                | 1280x1024         | 16               | 16                      | -                  |  |  |  |  |

|                | 640x480           | 24               | 24                      | -                  |  |  |  |  |

| 1004,760       | 800x600           | 24               | 24                      | -                  |  |  |  |  |

| 1024x768       | 1024x768          | 24               | 24                      | -                  |  |  |  |  |

|                | 1280x1024         | 16               | 16                      | -                  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Max color depth for display 1, 16bpp under dual display

Overview 1 - 9

Table 2: Lynx3DM+ (8MB): Display Support Modes

|                    |              | CRT Only    |        |        |  |  |

|--------------------|--------------|-------------|--------|--------|--|--|

| Dioplay Baseluties | Defrach (U=) | Color Depth |        |        |  |  |

| Display Resolution | Refresh (Hz) | 8 bpp       | 16 bpp | 24 bpp |  |  |

|                    | 60           | Х           | Х      | Х      |  |  |

| 640x480            | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

|                    | 60           | Х           | Х      | Х      |  |  |

| 800x600            | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

|                    | 60           | Х           | Х      | Х      |  |  |

| 1024x768           | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

|                    | 60           | Х           | Х      | Х      |  |  |

| 1280x1024          | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

| LCD/Simultaneous Mode |              |             |        |        |  |  |

|-----------------------|--------------|-------------|--------|--------|--|--|

| Diamina Basalatian    | Pofrach (Uz) | Color Depth |        |        |  |  |

| Display Resolution    | Refresh (Hz) | 8 bpp       | 16 bpp | 24 bpp |  |  |

| 640x480               | 60           | Х           | Х      | Х      |  |  |

| 800x600               | 60           | Х           | Х      | Х      |  |  |

| 1024x768              | 60           | Х           | Х      | Х      |  |  |

| 1280x1024             | 60           | Х           | Х      | -      |  |  |

|                | Dual Display Mode |                                             |                   |                                |  |  |  |  |

|----------------|-------------------|---------------------------------------------|-------------------|--------------------------------|--|--|--|--|

| Diamley 4 (D4) | Diamley 2 (D2)    | Color Depth (Max Color Depth Display 2 bpp) |                   |                                |  |  |  |  |

| Display 1 (D1) | Display 2 (D2)    | when D1 is 8 bpp                            | when D1 is 16 bpp | when D1 <sup>1</sup> is 24 bpp |  |  |  |  |

|                | 640x480           | 24 (D2)                                     | 24 (D2)           | -                              |  |  |  |  |

| 640x480        | 800x600           | 24                                          | 24                | -                              |  |  |  |  |

| 040X460        | 1024x768          | 24                                          | 24                | -                              |  |  |  |  |

|                | 1280x1024         | 24                                          | 24                | -                              |  |  |  |  |

|                | 640x480           | 24                                          | 24                | -                              |  |  |  |  |

| 000,,000       | 800x600           | 24                                          | 24                | -                              |  |  |  |  |

| 800x600        | 1024x768          | 24                                          | 24                | -                              |  |  |  |  |

|                | 1280x1024         | 24                                          | 24                | -                              |  |  |  |  |

|                | 640x480           | 24                                          | 24                | -                              |  |  |  |  |

| 4004700        | 800x600           | 24                                          | 24                | -                              |  |  |  |  |

| 1024x768       | 1024x768          | 24                                          | 24                | -                              |  |  |  |  |

|                | 1280x1024         | 24                                          | 24                | -                              |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Max color depth for display 1, 16bpp under dual display

1 - 10 Overview

Table 3: Lynx3DM+ (16MB): Display Support Modes

| CRT Only           |              |             |        |        |  |  |

|--------------------|--------------|-------------|--------|--------|--|--|

| Diamley Becalution | Defrack (U=) | Color Depth |        |        |  |  |

| Display Resolution | Refresh (Hz) | 8 bpp       | 16 bpp | 24 bpp |  |  |

|                    | 60           | Х           | х      | Х      |  |  |

| 640x480            | 75           | Х           | х      | Х      |  |  |

|                    | 85           | Х           | х      | Х      |  |  |

|                    | 60           | Х           | х      | Х      |  |  |

| 800x600            | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

|                    | 60           | Х           | Х      | Х      |  |  |

| 1024x768           | 75           | Х           | Х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

|                    | 60           | Х           | х      | Х      |  |  |

| 1280x1024          | 75           | Х           | х      | Х      |  |  |

|                    | 85           | Х           | Х      | Х      |  |  |

| LCD/Simultaneous Mode |              |             |        |        |  |  |

|-----------------------|--------------|-------------|--------|--------|--|--|

| Dianley Becelution    | Defrech (U=) | Color Depth |        |        |  |  |

| Display Resolution    | Refresh (Hz) | 8 bpp       | 16 bpp | 24 bpp |  |  |

| 640x480               | 60           | Х           | Х      | Х      |  |  |

| 800x600               | 60           | Х           | Х      | Х      |  |  |

| 1024x768              | 60           | Х           | Х      | Х      |  |  |

| 1280x1024             | 60           | Х           | Х      | х      |  |  |

| Dual Display Mode |                |                                             |                   |                    |  |  |  |

|-------------------|----------------|---------------------------------------------|-------------------|--------------------|--|--|--|

| Diamley 4 (D4)    | Diamby 2 (D2)  | Color Depth (Max Color Depth Display 2 bpp) |                   |                    |  |  |  |

| Display 1 (D1)    | Display 2 (D2) | when D1 is 8 bpp                            | when D1 is 16 bpp | when D11 is 24 bpp |  |  |  |

|                   | 640x480        | 24 (D2)                                     | 24 (D2)           | -                  |  |  |  |

| 640×490           | 800x600        | 24                                          | 24                | -                  |  |  |  |

| 640x480           | 1024x768       | 24                                          | 24                | -                  |  |  |  |

|                   | 1280x1024      | 24                                          | 24                | -                  |  |  |  |

|                   | 640x480        | 24                                          | 24                | -                  |  |  |  |

| 000,4000          | 800x600        | 24                                          | 24                | -                  |  |  |  |

| 800x600           | 1024x768       | 24                                          | 24                | -                  |  |  |  |

|                   | 1280x1024      | 24                                          | 24                | -                  |  |  |  |

|                   | 640x480        | 24                                          | 24                | -                  |  |  |  |

| 4004-700          | 800x600        | 24                                          | 24                | -                  |  |  |  |

| 1024x768          | 1024x768       | 24                                          | 24                | -                  |  |  |  |

|                   | 1280x1024      | 24                                          | 24                | -                  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Max color depth for display 1, 16bpp under dual display

Overview 1 - 11

### **Chapter 2: Pins**

The Lynx3DM+ is provided in a 316 BGA package.

Figure 3 illustrates the pinout diagram for the SM722/SM723 316 BGA package. Figure 55 illustrate the mechanical dimensions of the BGA package.

#### Lynx3DM+ Pin Descriptions

The following table, Table 4, provides brief description of each BGA ball of the Lynx3DM+. Signal names with ~ preceding are active "LOW" signals, whereas signal names without ~ preceding are active "HIGH" signals. Also, the following abbreviations are used for Pin Type.

Table 4 outlines the numerical SM722/723 BGA pins.

I - INPUT SIGNAL

O - Output Signal

I/O - Input or Output Signal

'Note: All Outputs and I/O signals are tri-stated. Internal pull-up for I/O pad are all  $100 K\Omega$  resistor. Internal pull-down for I/O pads are all  $100 K\Omega$  resistors.

**Table 4: Pin Description**

| Signal Name      | Туре     | Pull-up/<br>Pull-Down | IOL<br>(mA) | Max.<br>Load (pF)                            | Description                                                                                                                                                               |

|------------------|----------|-----------------------|-------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface ( | PCI or A | AGP)                  |             |                                              |                                                                                                                                                                           |

| AD [31:0]        | I/O      |                       | TBD         | 120                                          | Multiplexed Address and Data Bus. A bus transaction consists of an address cycle followed by one or more data cycles.                                                     |

| C/<br>~BE [3:0]  | I/O      |                       | TBD         | 120                                          | Bus Command and Byte Enables. These signals carry the bus command during the address cycle and byte enable during data cycles.                                            |

| PAR              | 1/0      |                       | TBD         | 120                                          | Parity. Lynx3DM+ asserts this signal to verify even parity across AD [31:0] and C/~BE [3:0].                                                                              |

| ~FRAME           | I/O      |                       | TBD         | 120                                          | Cycle Frame. Lynx3DM+ asserts this signal to indicate the beginning and duration of a bus transaction. It is deasserted during the final data cycle of a bus transaction. |

| ~TRDY            | I/O      |                       | TBD         | 120                                          | Target Ready. A bus data cycle is completed when both ~IRDY and ~TRDY are asserted on the same cycle.                                                                     |

| ~IRDY            | I/O      |                       | TBD         | 120                                          | Initiator Ready. A bus data cycle is completed when both ~IRDY and ~TRDY are asserted on the same cycle.                                                                  |

| ~STOP            | I/O      |                       | TBD         | 120                                          | Stop. Lynx3DM+ asserts this signal to indicate that the current target is requesting the master to stop current transaction.                                              |

| ~DEVSEL          | I/O      |                       | TBD         | 120                                          | Device Select. Lynx3DM+ asserts this signal when it decodes its addresses as the target of the current transaction.                                                       |

| IDSEL            | _        |                       |             |                                              | ID Select. This input is used during PCI configuration read/write cycles.                                                                                                 |

| CLK              | Ι        |                       |             |                                              | System Clock, 33MHz. for PCI and 66MHz for AGP                                                                                                                            |

| ~RST             | _        |                       |             |                                              | System Reset. Lynx3DM+ asserts this signal to force registers and state machines to initial default values                                                                |

| ~REQ             | 0        |                       | TBD         | 120                                          | Bus Request (bus master mode)                                                                                                                                             |

| ~GNT             | Ι        |                       |             |                                              | Bus Grant (bus master mode)                                                                                                                                               |

| ~INTA            | 0        |                       | TBD         | 120                                          | Interrupt                                                                                                                                                                 |

| PME#             | 0        |                       | TBD         | 120                                          | Power management event signals                                                                                                                                            |

| ~PIPE            | 0        |                       | TBD         | 120                                          | Pipe signal. Initiates pipelined AGP request. Signal indicates beginning and duration of pipelined AGP access.                                                            |

| ~RBF             | 0        |                       | TBD         | 120                                          | Read Buffer Full. Indicates if graphics device can accept previously low priority read data                                                                               |

| AD_STB[1:0]      | I/O      |                       | TBD         | 120                                          | Address strobes 1, 0 for 2X transfer support                                                                                                                              |

| ST[2:0]          | I        |                       |             |                                              | Status bus for AGP support                                                                                                                                                |

| SBA[7:0]         | 0        |                       | TBD         | 120                                          | Sideband address bits 7-0                                                                                                                                                 |

| SB_STB           | 0        |                       | TBD         | 120                                          | Sideband strobe                                                                                                                                                           |

| ~AGP_BUSY        | 0        |                       | TBD         | 120                                          | Power management signal for AGP bus.                                                                                                                                      |

| ~STP_AGP         | I        |                       |             |                                              | Power management signal for AGP bus.                                                                                                                                      |

| Power Down Int   | erface   | 1                     |             | <u>.                                    </u> |                                                                                                                                                                           |

2 - 2 Pins

| Signal Name          | Туре   | Pull-up/<br>Pull-Down   | IOL<br>(mA) | Max.<br>Load (pF) | Description                                                                                                                                                                                                                                            |

|----------------------|--------|-------------------------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ~PDOWN               | I      | pull-up                 |             |                   | Power down mode enable                                                                                                                                                                                                                                 |

| ~CLKRUN/<br>ACTIVITY | 0      | pull-up                 | TBD         | 60                | ~CLKRUN or<br>Lynx3DM+ Memory and I/O activity detection depending<br>on SCR18 [7]<br>0 = select ~CLKRUN<br>1 = select ACTIVITY                                                                                                                        |

| Clock Interface      |        |                         |             |                   |                                                                                                                                                                                                                                                        |

| REFCLK               | I      | pull-up                 |             |                   | 32KHz refresh clock source for power down                                                                                                                                                                                                              |

| PALCLK               | I      | pull-up                 |             |                   | 27MHz clock source for PAL TV                                                                                                                                                                                                                          |

| CKIN                 | I      | pull-up                 |             |                   | 14.318MHz clock (~EXCKEN = 1) or Video Clock (~EXCKEN = 0)                                                                                                                                                                                             |

| MCKIN/<br>LVDSCLK    | I/O    | pull-up                 | TBD         | 60                | Memory Clock In (~EXCKEN = 0) LVDSCLK Out (~EXCKEN = 1). LVDSCLK is a free running clock which can be used to drive LVDS transmitter for DSTN panels. Note: this pin is used as CLK2 for dual panel configuration. For this case configure as LVDSCLK. |

| ~EXCKEN              | I      | pull-up                 |             | 60                | External Clock Enable. Select external VCLK from CKIN and MCLK from MCKIN.                                                                                                                                                                             |

| External Display     | / Memo | ry Interface (f         | or refer    | rence only)       |                                                                                                                                                                                                                                                        |

| MA [10:0]            | 0      | pull-down               | TBD         | 50                | External Memory Address Bus. The video memory row and column addresses are multiplexed on these lines.                                                                                                                                                 |

| MD [63:0]            | I/O    | MD [63:33]<br>pull-down | TBD         | 20                |                                                                                                                                                                                                                                                        |

| MD [63:0]            | I/O    | MD[32:0]<br>pull-up     | TBD         | 20                |                                                                                                                                                                                                                                                        |

| ~WE                  | 0      | pull-up                 | TBD         | 50                |                                                                                                                                                                                                                                                        |

| ~RAS                 | 0      | pull-up                 | TBD         | 50                |                                                                                                                                                                                                                                                        |

| ~CAS                 | 0      | pull-up                 | TBD         | 50                | External SGRAM Column Address Select                                                                                                                                                                                                                   |

| ~CS0                 | 0      | pull-up                 | TBD         | 50                | External SGRAM Chip Select 0, select 1st 1MB within the 2MB memory, or select 1st 2MB within the 4MB memory                                                                                                                                            |

| ~DQM<br>[7:0]        | 0      | pull-up                 | TBD         | 50                | External SGRAM I/O mask [7:0]. DQM [7:0] are byte specific. DQM0 masks MD [7:0], DQM1 masks MD [15:8],Ö,and DQM7 masks MD [63:58].                                                                                                                     |

| DSF                  | 0      | pull-up                 | TBD         | 50                | External SGRAM Block write                                                                                                                                                                                                                             |

| BA[1:0]              | 0      |                         | TBD         | 50                | External SGRAM Bank Select. SDRAM has 2/4 internal banks. Bank address defines to which bank the current command is being applied.                                                                                                                     |