#### features

- 11.2-GHz Bandwidth

- 5.5-kΩ Differential Transimpedance

- 8.5-pA/\/Hz Typical Input Referred Noise

- 2-mA Maximum Input Current

- Received Signal Strength Indication

- CML Data Outputs

- Offset Cancellation

- Single 3.3-V Supply

- Bare-Die Option

#### description

applications

- SONET OC-192

- 10-Gbps Ethernet Receivers

- 10-Gbps Fibre Channel Receivers

The ONET9901TA is a high-speed transimpedance amplifier used in SDH/SONET systems with data rates up to 10.7 Gbps. It features a low input referred noise, 11.2-GHz bandwidth and a 5.5-k $\Omega$  transimpedance.

The ONET9901TA device is available in die form and requires a single 3.3-V supply. The ONET9901TA is power efficient and dissipates less than 100 mW (typical). The ONET9901TA is characterized for operations from 0°C to 85°C.

#### available options

| TA          | PACKAGED DEVICE |

|-------------|-----------------|

| 0°C to 85°C | ONET9901TAY     |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2004, Texas Instruments Incorporated

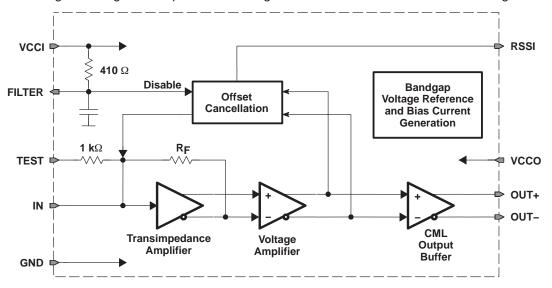

#### block diagram

The ONET9901TA is a high performance 10.7-Gbps transimpedance amplifier that can be segmented into the signal path, filter, and offset cancellation block. The signal path consists of a transimpedance amplifier stage, a voltage amplifier, and an output buffer. The filter circuit provides a filtered VCC for the photodiode. The offset correction circuit uses an internal low-pass filter to cancel the dc on the input and it provides a signal to monitor the received signal strength. A simplified block diagram of the ONET9901TA is shown in Figure 1.

Figure 1. Block Diagram

# signal path

The first stage of the signal path is a transimpedance amplifier that takes the photodiode current and converts it to a voltage signal. The second stage is a voltage amplifier that provides additional gain. The output of the second stage feeds the output buffer and the offset cancellation circuitry. The third and final signal path stage of the ONET9901TA is the output buffer. The output buffer provides CML outputs with an on-chip  $50-\Omega$  back-termination to VCCO.

#### filter circuitry

The filter pin provides a filtered VCC for the photodiode bias. The on-chip low-pass filter for the photodiode VCC is implemented using a filter resistor of 410  $\Omega$  and an internal capacitor. If additional filtering is required for the application, an external capacitor should be connected to the FILTER pin.

#### offset cancellation and RSSI

The offset cancellation circuitry performs low pass filtering of the output of the voltage amplifier. This senses the dc offset at the input of the ONET9901TA. The circuitry subtracts current from the input to effectively cancel the dc. The sensed current is mirrored and is used to generate the RSSI output through an external  $10-k\Omega$  resistor. To disable the offset correction loop, the FILTER pin should be tied to GND.

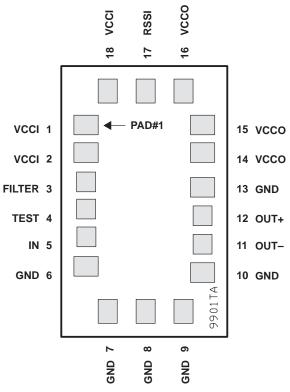

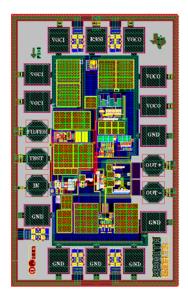

### bond pad assignment

The ONET9901TA is available as bare-die. The location of the bondpads is shown in Figure 2. The circuit is characterized for ambient temperatures between 0°C and 85°C.

Figure 2. Bond Pad Assignment of the ONET9901TA

#### terminal functions

The following table shows a pad description for the ONET9901TA.

| TERMINAL |          |            |                                                                                                                                                                 |  |  |  |

|----------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.      | TYPE       | DESCRIPTION                                                                                                                                                     |  |  |  |

| VCCI     | 1, 2, 18 | Supply     | Input stage 3.3-V ±10% supply voltage.                                                                                                                          |  |  |  |

| FILTER   | 3        | Analog     | Bias voltage for the photodiode (connects to an internal 410- $\Omega$ resistor to VCCI). To disable the offset correction loop, connect the FILTER pin to GND. |  |  |  |

| TEST     | 4        | Analog in  | Test pad. Connects to IN via a 1-k $\Omega$ resistor.                                                                                                           |  |  |  |

| IN       | 5        | Analog in  | Data input to TIA                                                                                                                                               |  |  |  |

| GND      | 6–10,13  | Supply     | Circuit ground                                                                                                                                                  |  |  |  |

| OUT-     | 11       | Analog out | Inverted data output. On-chip 50- $\Omega$ back-terminated to VCCO.                                                                                             |  |  |  |

| OUT+     | 12       | Analog out | Non-inverted data output. On-chip 50- $\Omega$ back-terminated to VCCO.                                                                                         |  |  |  |

| VCCO     | 14–16    | Supply     | Output stage 3.3-V ±10% supply voltage.                                                                                                                         |  |  |  |

| RSSI     | 17       | Analog out | Analog output voltage proportional to the input data amplitude. Indicates the strength of the received signal (RSSI).                                           |  |  |  |

#### absolute maximum ratings

over operating free-air temperature range unless otherwise noted<sup>†</sup>

|                                      |                                                     | VALUE     | UNIT     |

|--------------------------------------|-----------------------------------------------------|-----------|----------|

| VCCI, VCCO                           | Supply voltage, See Note 1                          | -0.3 to 4 | V        |

| V(FILTER), V(OUT+), V(OUT-), V(RSSI) | Voltage at FILTER, OUT+, OUT–, and RSSI, See Note 1 | -0.3 to 4 | V        |

| I(IN), I(TEST)                       | Supply current into IN and TEST                     | –5 to 5   | mA       |

| I(FILTER)                            | Supply current into FILTER                          | -8 to 8   | mA       |

| I(OUT+), I(OUT-)                     | Continuous current at outputs                       | -25 to 25 | mA       |

| ESD                                  | ESD rating at all pins                              | 2         | kV (HBM) |

| T <sub>J(max)</sub>                  | Maximum junction temperature                        | 125       | °C       |

| T <sub>stg</sub>                     | Storage temperature range                           | -65 to 85 | °C       |

| TA                                   | Operating free-air temperature range                | 0 to 85   | °C       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to the network ground terminal.

#### recommended operating conditions

|                                                     | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------|-----|-----|-----|------|

| Supply voltage, V <sub>CCI</sub> , V <sub>CCO</sub> | 3   | 3.3 | 3.6 | V    |

| Operating free-air temperature, T <sub>A</sub>      | 0   |     | 85  | °C   |

# dc electrical characteristics

over recommended operating conditions (unless otherwise noted), typical operating condition is at  $V_{CCI} = V_{CCO} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$

|                       | PARAMETER                    | TEST CONDITIONS     | MIN | TYP  | MAX  | UNIT |

|-----------------------|------------------------------|---------------------|-----|------|------|------|

| VCC                   | Supply voltage               |                     | 3   | 3.3  | 3.6  | V    |

| ICC                   | Supply current               |                     |     | 30   | 41   | mA   |

| VIN                   | Input bias voltage           |                     |     | 0.84 | 0.96 | V    |

| r <sub>o</sub>        | Output resistance            | Single-ended to VCC |     | 50   |      | Ω    |

| <sup>r</sup> (FILTER) | Photodiode filter resistance |                     | 330 | 410  | 500  | Ω    |

#### ac electrical characteristics

over recommended operating conditions (unless otherwise noted), typical operating condition is at  $V_{CCI} = V_{CCO} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$

|                                              | PARAMETER                     | TEST CONDITIONS                                                              | MIN  | TYP  | MAX  | UNIT              |

|----------------------------------------------|-------------------------------|------------------------------------------------------------------------------|------|------|------|-------------------|

| I <sub>IN,OVL</sub>                          | AC input overload current     |                                                                              | 2    |      |      | mA <sub>p-p</sub> |

|                                              | Input linear range            | 0.95 < linearity < 1.05                                                      | 50   | 60   |      | μA <sub>p-p</sub> |

| ARSSI                                        | RSSI gain                     | 10-k $\Omega$ load, See Note 2                                               | 1500 | 2000 | 2500 | V/A               |

| Z <sub>(21)</sub>                            | Small signal transimpedance   | Differential output, 10 $\mu$ Ap-p < IIN = < 50 $\mu$ Ap-p                   | 4400 | 5500 | 6600 | Ω                 |

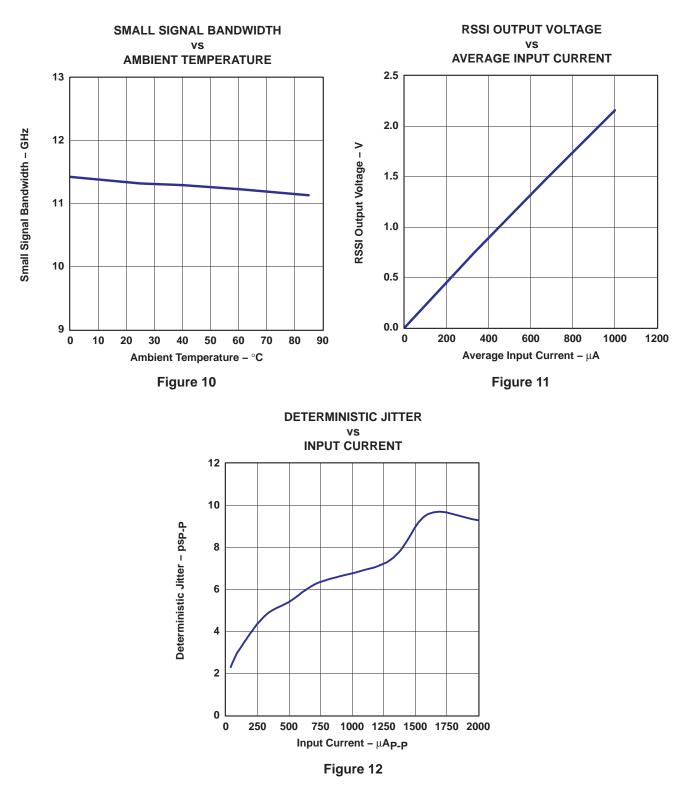

| BW(H_3dB)                                    | Small signal bandwidth        | C <sub>PD</sub> = 0.2 pF                                                     |      | 11.2 |      | GHz               |

| BW(L_3dB)                                    | Low frequency -3 dB bandwidth | $-3 \text{ dB}, \text{ I}_{\text{IN}} = < 50 \ \mu\text{A}_{p-p} \text{ dc}$ |      | 17   |      | kHz               |

| BW(H_3dB_RSSI)                               | RSSI bandwidth                |                                                                              |      | 5    |      | kHz               |

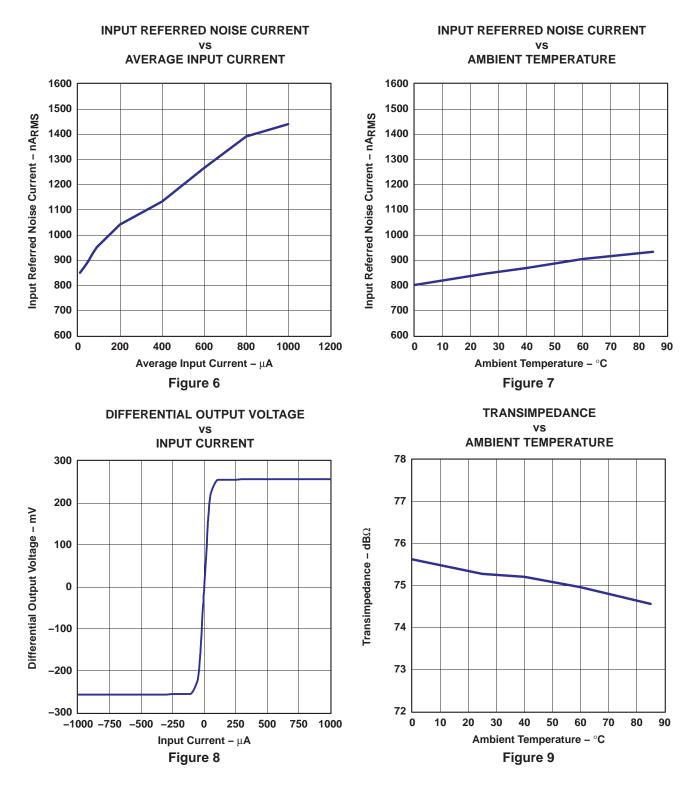

| I <sub>N,IN</sub>                            | Input referred RMS noise      | C <sub>PD</sub> = 0.2 pF                                                     |      | 900  |      | nA                |

|                                              | Input referred noise density  | C <sub>PD</sub> = 0.2 pF                                                     |      | 8.5  |      | pA/√Hz            |

|                                              |                               | I <sub>IN</sub> < 1.3 mA <sub>p-p</sub> (K28.5 pattern)                      |      | 7    |      |                   |

| DJ                                           | Deterministic jitter          | $I_{IN} = 2 \text{ mA}_{p-p}$ (K28.5 pattern)                                |      | 11   | 22   | ps <sub>p-p</sub> |

| VOD(max) Maximum differential output voltage |                               | $I_{IN} = 1 \text{ mA}_{p-p}$                                                |      | 500  | 700  | mV <sub>p-p</sub> |

NOTE 2: On the chip, a 6725-Ω resistor is used in parallel to the external 10-kΩ resistor, resulting in a total 4-kΩ resistor for a typical process. By choosing an appropriate external resistor, the typical RSSI gain can be adjusted. Without an external resistor, the RSSI gain is approximately 3360 V/A under typical conditions.

# **APPLICATION INFORMATION**

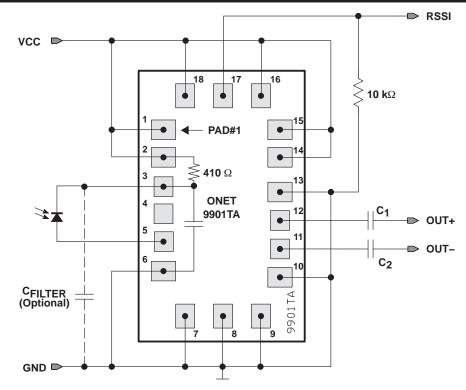

Figure 3 shows the ONET9901TA being used as a receiver in a typical fiber optic application. The ONET9901TA converts the electrical current generated by the PIN photodiode into a differential voltage output. The FILTER input provides a dc bias voltage for the PIN that is low pass filtered by the combination of the internal 410- $\Omega$  resistor and internal capacitor. For additional power supply filtering, use an external capacitor (C<sub>FILTER</sub>). The RSSI output is used to mirror the photodiode output current and must be connected via a 10-k $\Omega$  resistor to GND or left open. Within the ONET9901TA, the OUT+ and OUT– pins are internally terminated by a 50- $\Omega$  pullup to VCCO.

Figure 3. Basic Application Circuit

# board layout

Careful attention to board layout parasitics and external components is necessary to achieve optimal performance with a high-performance transimpedance amplifier like the ONET9901TA.

Recommendations that optimize performance include:

- Minimize total capacitance on the IN pad by using a low-capacitance photodiode and paying attention to stray capacitances. Place the photodiode close to the ONET9901TA die in order to minimize the bond wire length and thus the parasitic inductance.

- 2. The external filter capacitor (C<sub>FILTER</sub>) may have an impact on the transfer function of the TIA and must be chosen with care based on the module implementation.

- 3. Use identical termination and symmetrical transmission lines at the differential output pins OUT+ and OUT-.

- 4. Use short bond wire connections for the supply terminals VCCI, VCCO, and GND. Provide sufficient supply voltage filtering.

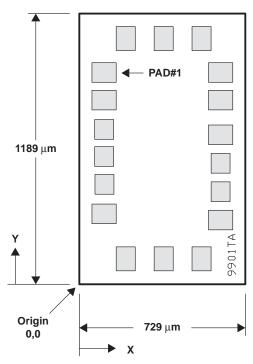

# chip dimensions and pad locations

Figure 5. Chip Layout

| PAD | LOWER LEFT<br>COORDINATE |               | UPPER RIGHT<br>COORDINATE |                        | SYMBOL | TYPE       | DESCRIPTION                                         |  |

|-----|--------------------------|---------------|---------------------------|------------------------|--------|------------|-----------------------------------------------------|--|

|     | <b>χ [μm]</b>            | <b>y [μm]</b> | <b>χ [μm]</b>             | <b>y [</b> μ <b>m]</b> |        |            |                                                     |  |

| 1   | 57                       | 887           | 162                       | 972                    | VCCI   | Supply     | Input stage 3.3-V $\pm$ 10% supply voltage          |  |

| 2   | 57                       | 767           | 162                       | 852                    | VCCI   | Supply     | Input stage 3.3-V $\pm$ 10% supply voltage          |  |

| 3   | 67                       | 637           | 152                       | 722                    | FILTER | Analog     | Bias voltage for photodiode                         |  |

| 4   | 67                       | 517           | 152                       | 602                    | TEST   | Analog in  | Test pad. Connects to IN via a $1-k\Omega$ resistor |  |

| 5   | 67                       | 397           | 152                       | 482                    | IN     | Analog in  | Data input to TIA                                   |  |

| 6   | 57                       | 267           | 162                       | 352                    | GND    | Supply     | Circuit ground                                      |  |

| 7   | 162                      | 57            | 247                       | 162                    | GND    | Supply     | Circuit ground                                      |  |

| 8   | 327                      | 57            | 412                       | 162                    | GND    | Supply     | Circuit ground                                      |  |

| 9   | 492                      | 57            | 577                       | 162                    | GND    | Supply     | Circuit ground                                      |  |

| 10  | 567                      | 237           | 672                       | 322                    | GND    | Supply     | Circuit ground                                      |  |

| 11  | 577                      | 367           | 662                       | 452                    | OUT-   | Analog out | Inverted data output                                |  |

| 12  | 577                      | 487           | 662                       | 572                    | OUT+   | Analog out | Non-inverted data output                            |  |

| 13  | 567                      | 617           | 672                       | 702                    | GND    | Supply     | Circuit ground                                      |  |

| 14  | 567                      | 747           | 672                       | 832                    | VCCO   | Supply     | Output stage 3.3-V $\pm$ 10% supply voltage         |  |

| 15  | 567                      | 877           | 672                       | 962                    | VCCO   | Supply     | Output stage 3.3-V ±10% supply voltage              |  |

| 16  | 492                      | 1027          | 577                       | 1132                   | VCCO   | Supply     | Output stage 3.3-V ±10% supply voltage              |  |

| 17  | 327                      | 1027          | 412                       | 1132                   | RSSI   | Analog out | RSSI output voltage signal                          |  |

| 18  | 162                      | 1027          | 247                       | 1132                   | VCCI   | Supply     | Input stage 3.3-V ±10% supply voltage               |  |

Table 1. Pad Locations and Description of the ONET9901TA

#### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

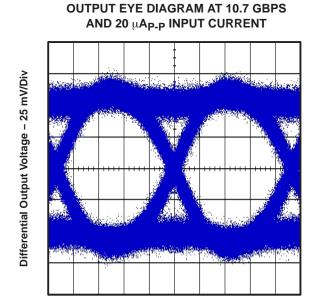

Time – 20 ps/Div Figure 13

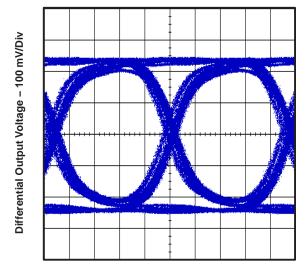

#### OUTPUT EYE DIAGRAM AT 10.7 GBPS AND 2 mA<sub>P-P</sub> INPUT CURRENT

Time – 20 ps/Div Figure 14

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated