# VX-Series STD Bus Industrial Card Cages

#### REFERENCE MANUAL

VX-03R Rev. 0.01 VX-03T Rev. 0.01 VX-06R Rev. 0.01 VX-06T Rev. 0.01 VX-09R Rev. 0.01 VX-09T Rev. 0.01 VX-12R Rev. 0.01 VX-12T Rev. 0.01

Doc. Rev. 03/23/94

VersaLogic Corporation 3888 Stewart Rd. • Eugene, OR 97402

> (503) 485-8575 Fax (503) 485-5712

Contents Copyright 1994 All Rights Reserved

#### NOTICE:

Although every effort has been made to ensure this documentation is error-free, VersaLogic makes no representations or warranties with respect to this product and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

VersaLogic reserves the right to revise this product and associated documentation at any time without obligation to notify anyone of such changes.

MVX3/12

## Table of Contents

| troduction             | <b>. 2</b> |

|------------------------|------------|

| ard Orientation        | . 2        |

| ounting Options        | . 3        |

| mensions               | . 4        |

| otherboard             |            |

| Termination            |            |

| Power Supply Options   | . 5        |

| Priority Chain Signal  | .5         |

| Distributed Processing | . 5        |

| onnection Points       | . 6<br>. 7 |

| D Bus Pinout           | .8         |

## Introduction

The VX Series card cages are high quality STD Bus card cages especially suitable for industrial applications. They feature heavy-duty cold-rolled steel construction with sealed black oxide finish, 5/8" card spacing, card restraint bar, and the VXMB low noise motherboard with shielded signal lines and high reliability bus connectors.

The VX Series card cages are available in several sizes and configurations. Cages can be purchased in 3, 6, 9, and 12-slot versions, with or without motherboard, and are available with table or rack/panel-mount end plates. Other mounting positions are possible by rotating the left and right end plates 180 degrees. Additionally the mounting flanges can be oriented inwards or outwards.

The VXMB Series motherboards feature interleaved signal and ground traces for increased immunity to crosstalk and signal noise, high speed/low capacitance two-layer construction, high reliability card connectors with gold plated contacts, and clearly labeled power supply connection points.

## **Card Orientation**

STD Bus cards which are inserted in the card cage must be oriented correctly. Most STD Bus board manufacturers provide a card ejector on the top edge of their cards. Be certain to position these card ejectors toward the top of the card cage. For upside down or unusual mounting positions note the large white arrow(s) on the motherboard (between connectors) that indicate the proper card ejector orientation.

\*\* CAUTION \*\* Cards should be inserted or removed from the STD Bus card cage only when the system power is off.

2

# **Mounting Options**

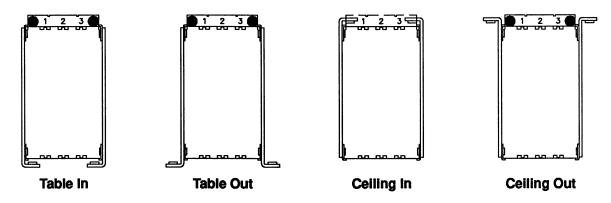

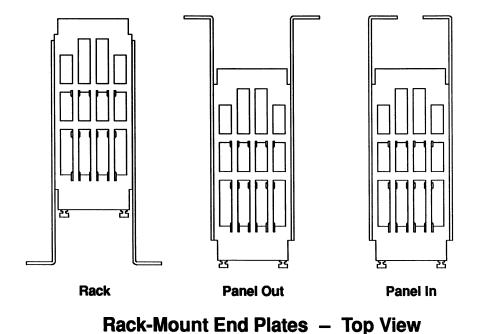

The VX Series cages can be mounted in a variety of ways by changing the orientation of the end plates. The figures below show the various combinations for the table and rack/panel-mount versions of the cage.

The four threaded mounting holes in the table-mount flanges accept #8-32 screws. The four 0.281" slots in the rack/panel flanges will clear #12 or smaller diameter screws.

**Table-Mount End Plates - Front View**

Figure 1. Mounting Configurations

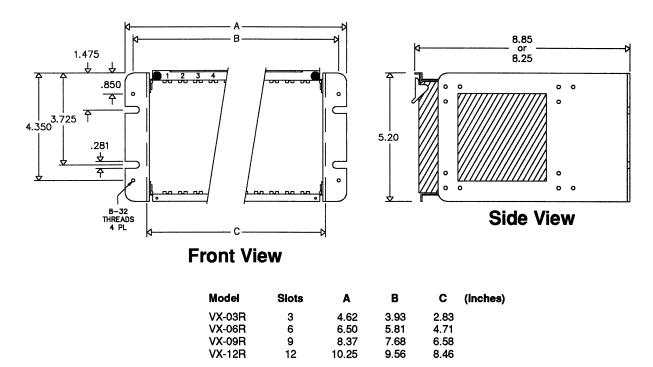

Figure 2. Overall Dimensions (Rack/Panel-Mount Models)

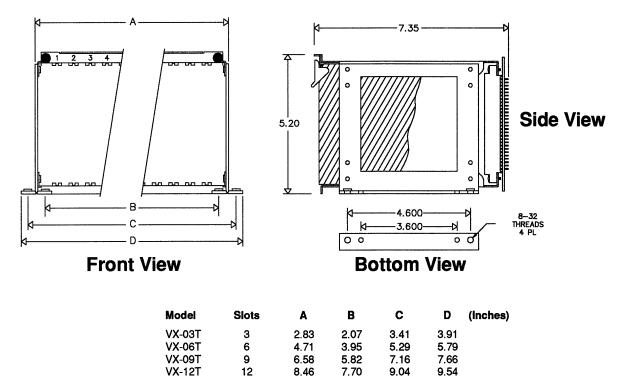

Figure 3. Overall Dimensions (Table-Mount Models)

## **Motherboard**

#### **Termination**

The VXMB motherboard used in the VX Series card cages features fully shielded signal lines (interwoven ground plane) to reduce noise and signal crosstalk on the bus. This design provides excellent, high speed performance and does not require any other type of noise control such as bus termination networks. The two-sided PCB design reduces the capacitive loading and associated problems that occur with multilayer mother board designs.

#### **Bus Speed**

All VX Series motherboards are designed to operate correctly, unterminated, when run at clock speeds less than or equal to those set forth in the STD Z-80 6 MHz, or STD-80 Series Compatible 8 MHz bus timing specifications. Operation at the high end of these specifications requires the use of 74LSxxx or 74HCxxx bus driving components on the CPU (bus master). All motherboards work properly at 10 MHz when using CPU cards manufactured by VersaLogic.

#### **Power Supply Options**

The STD Bus system can be powered with a plug-in, in-slot power supply such as VersaLogic's PSC card, or by connecting an external power supply to the solder pads on the back of the motherboard.

#### **Priority Chain Signal**

The STD Bus includes a Priority Chain In (PCI) and a Priority Chain Out (PCO) signal line which can be used in a daisy chain (i.e., card slot dependent) interrupt structure. The VX Series motherboards connect each PCO line to the PCI line of the card slot on its left. This results in the card slot in the far right position being the highest priority slot. The far left slot is the lowest priority slot.

### **Jumper Options**

Jumper V1 ties STD Bus pin 5 (VBB1) and pin 6 (VBB2) together for applications which require these two pins to be common. Jumper V2 ties AUXGND (pins 53 and 54) to GND (pins 3 and 4). Refer to the solder pad layout drawings for jumper locations.

#### **Distributed Processing**

The VX Series card cages are designed to allow the mounting of several electrically isolated mother-boards within a single cage. Multiple motherboards can be combined without the loss of a card slot (e.g., a 6 and 3-slot motherboard installed into a 9-slot cage).

#### **Connection Points**

In addition to the STD Bus boards which plug into the bus, a number of external connections may be made to the motherboard. Pads for these connections are provided along the top and bottom edges of the motherboard. The available connection points are:

| +5V  | Connection to the +5 volt power supply line.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GND  | Ground connection for the +5 volt power supply.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| VBB1 | Connection for -5 volt or battery backup voltage (VBAT) STD Bus pin 5. By soldering a shorting wire across jumper V1, bus pins 5 and 6 can be tied together. Refer to the solder pad layout drawings for jumper location.                                                        |  |  |  |  |  |  |

| VBB2 | Connection for loss-of-power indication (DCPD*) STD Bus pin 6. Note, if jumper V1 is inserted, this pad is tied in common with VBB1.                                                                                                                                             |  |  |  |  |  |  |

| +12V | Connection to +12 volt power input (if used).                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| AGND | Ground connection for the ±12 volt power supply (AUXGND). By soldering a shorting wire across jumper V2, AUXGND can be tied to GND for systems which need these two grounds to be common. Refer to the solder pad layout drawings at the end of this manual for jumper location. |  |  |  |  |  |  |

| -12V | Connection to -12 volt power input (if used).                                                                                                                                                                                                                                    |  |  |  |  |  |  |

PB RST Connection to a system reset push button switch (normally open).

#### **SOLDER SIDE**

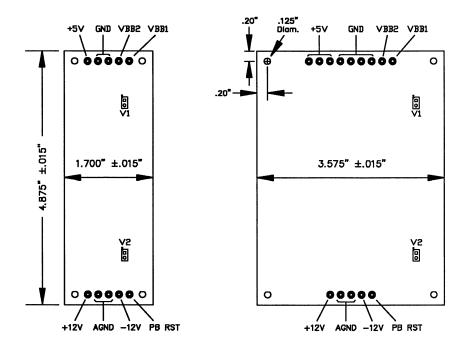

Figure 4. Solder Pad Layout (3 and 6-slot motherboards)

#### **SOLDER SIDE**

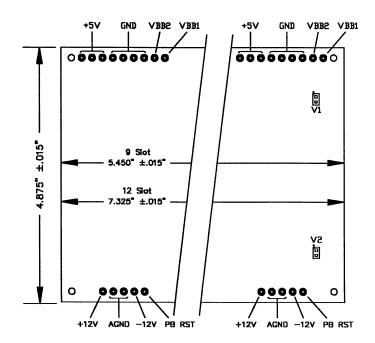

Figure 5. Solder Pad Layout (9 and 12-slot motherboards)

## **STD Bus Pinout**

The connector pin assignments for STD Bus cards are shown below. Pins 1 and 2 are at the top (card ejector) edge of the board. As noted below the odd numbered pins are on the component side of the board, while the even numbered pins are on the solder side. Direction of signal flow is referenced to the bus master (i.e., processor card).

| Pin         Signal         Flow         Description         Pin         Signal         Flow         Description           1         +5V         In         +5 volt power         2         +5V         In         +5 volt power           3         GND         In         Digital ground         4         GND         In         Digital ground           5         VBB1         In         -5V or Bat Backup         6         VBB2         In         -5V or Power Down           7         D3 / A19         I/O         Data / Address bus         10         D6 / A22         I/O         Data / Address bus           9         D2 / A18         I/O         Data / Address bus         10         D6 / A22         I/O         Data / Address bus           11         D1 / A17         I/O         Data / Address bus         12         D5 / A21         I/O         Data / Address bus           13         D0 / A16         I/O         Data / Address bus         14         D4 / A20         I/O         Data / Address bus           15         A7         Out         Address bus         18         A14         Out         Address bus           19         A5         Out         Address bus         22                     | COMPONENT SIDE |                   |      | SOLDER SIDE        |     |                   |      |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|------|--------------------|-----|-------------------|------|---------------------|

| 3 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin            | Signal            | Flow | Description        | Pin | Signal            | Flow | Description         |

| 3 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1              | +5V               | In   | +5 volt power      | 2   | +5V               | In   | +5 volt power       |

| 5         V <sub>BB</sub> 1         In         -5V or Bat Backup         6         V <sub>BB</sub> 2         In         -5V or Power Down           7         D3 / A19         I/O         Data / Address bus         8         D7 / A23         I/O         Data / Address bus           9         D2 / A18         I/O         Data / Address bus         10         D6 / A22         I/O         Data / Address bus           11         D1 / A17         I/O         Data / Address bus         12         D5 / A21         I/O         Data / Address bus           13         D0 / A16         I/O         Data / Address bus         14         D4 / A20         I/O         Data / Address bus           15         A7         Out         Address bus         16         A15         Out         Address bus           17         A6         Out         Address bus         20         A13         Out         Address bus           21         A4         Out         Address bus         22         A12         Out         Address bus           25         A2         Out         Address bus         26         A10         Out         Address bus           26         A2         Out         Address bus         28         A | 3              | GND               | In   | Digital ground     | 4   | GND               | ln   |                     |

| 9 D2 / A18 I/O Data / Address bus 11 D1 / A17 I/O Data / Address bus 12 D5 / A21 I/O Data / Address bus 13 D0 / A16 I/O Data / Address bus 14 D4 / A20 I/O Data / Address bus 15 A7 Out Address bus 16 A15 Out Address bus 17 A6 Out Address bus 18 A14 Out Address bus 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Interrupt request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Push button reset 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 53 AUXGND In ±12 volt ground                                                                           | 5              | V <sub>BB</sub> 1 | In   | -5V or Bat Backup  | 6   | V <sub>BB</sub> 2 | In   |                     |

| 9 D2 / A18 I/O Data / Address bus 11 D1 / A17 I/O Data / Address bus 12 D5 / A21 I/O Data / Address bus 13 D0 / A16 I/O Data / Address bus 14 D4 / A20 I/O Data / Address bus 15 A7 Out Address bus 16 A15 Out Address bus 17 A6 Out Address bus 18 A14 Out Address bus 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Interrupt request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Push button reset 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 53 AUXGND In ±12 volt ground                                                                           | 7              | D3 / A19          | I/O  | Data / Address bus | 8   | D7 / A23          | I/O  | Data / Address bus  |

| 11 D1 / A17 I/O Data / Address bus 12 D5 / A21 I/O Data / Address bus 13 D0 / A16 I/O Data / Address bus 14 D4 / A20 I/O Data / Address bus 15 A7 Out Address bus 16 A15 Out Address bus 17 A6 Out Address bus 18 A14 Out Address bus 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 ORQ* Out Address bus 30 A8 Out Address bus 31 ORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Bus acknowledge 42 BUSRQ* In Bus request 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* Out Priority chain out 52 PCI Out Priority chain in 53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                             |                |                   |      |                    |     |                   |      |                     |

| 13 D0 / A16 I/O Data / Address bus 14 D4 / A20 I/O Data / Address bus 15 A7 Out Address bus 16 A15 Out Address bus 17 A6 Out Address bus 18 A14 Out Address bus 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                              | 11             | D1 / A17          | 1/0  | Data / Address bus |     |                   |      | Data / Address bus  |

| 17 A6 Out Address bus 18 A14 Out Address bus 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 32 RD* Out Address bus 31 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                     | 13             | D0 / A16          | 1/0  | Data / Address bus | 14  |                   |      | Data / Address bus  |

| 19 A5 Out Address bus 20 A13 Out Address bus 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 32 RD* Out Address bus 31 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                               | 15             | A7                | Out  | Address bus        | 16  | A15               | Out  | Address bus         |

| 21 A4 Out Address bus 22 A12 Out Address bus 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Interrupt request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17             | A6                | Out  | Address bus        | 18  | A14               | Out  | Address bus         |

| 23 A3 Out Address bus 24 A11 Out Address bus 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 31 ORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19             | A5                | Out  | Address bus        | 20  | A13               | Out  | Address bus         |

| 25 A2 Out Address bus 26 A10 Out Address bus 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 32 RD* Out Memory addr. select 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                           | 21             | A4                | Out  | Address bus        | 22  | A12               | Out  | Address bus         |

| 27 A1 Out Address bus 28 A9 Out Address bus 29 A0 Out Address bus 30 A8 Out Address bus 30 A8 Out Address bus 31 WR* Out Write strobe 32 RD* Out Memory addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23             | <b>A</b> 3        | Out  | Address bus        | 24  | A11               | Out  | Address bus         |

| 29 A0 Out Address bus 30 A8 Out Address bus  31 WR* Out Write strobe 32 RD* Out Memory addr. select  33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select  35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion  37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync.  39 STATUS1* Out CPU status 40 STATUS0* Out CPU status  41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request  43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request  45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt  47 SYSRESET* Out System reset 48 PBRESET* In Push button reset  49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing  51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25             | A2                | Out  | Address bus        | 26  | A10               | Out  | Address bus         |

| 31 WR* Out Write strobe 32 RD* Out Memory addr. select 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27             | <b>A</b> 1        | Out  | Address bus        | 28  | <b>A9</b>         | Out  | Address bus         |

| 33 IORQ* Out I/O addr. select 34 MEMRQ* Out Memory addr. select 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUSO* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29             | A0                | Out  | Address bus        | 30  | A8                | Out  | Address bus         |

| 35 IOEXP I/O I/O expansion 36 MEMEX I/O Memory expansion 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUSO* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | WR*               | Out  |                    | 32  | RD*               | Out  | Read strobe         |

| 37 REFRESH* Out Refresh timing 38 MCSYNC* Out Machine cycle sync. 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |      | I/O addr. select   | 34  | MEMRQ*            |      | Memory addr. select |

| 39 STATUS1* Out CPU status 40 STATUS0* Out CPU status 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                   |      |                    |     |                   | 1/0  | Memory expansion    |

| 41 BUSAK* Out Bus acknowledge 42 BUSRQ* In Bus request 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                   |      |                    |     |                   |      |                     |

| 43 INTAK* Out Interrupt acknowledge 44 INTRQ* In Interrupt request 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                   |      |                    |     |                   | Out  |                     |

| 45 WAITRQ* In Wait request 46 NMIRQ* In Non-maskable Interrupt 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in  53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                   |      |                    |     |                   |      | •                   |

| 47 SYSRESET* Out System reset 48 PBRESET* In Push button reset 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in 53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                   |      |                    |     |                   |      |                     |

| 49 CLOCK* Out CPU clock 50 CNTRL* In AUX timing 51 PCO Out Priority chain out 52 PCI Out Priority chain in 53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                   |      |                    |     |                   |      |                     |

| 51 PCO Out Priority chain out 52 PCI Out Priority chain in 53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                   |      |                    |     |                   |      |                     |

| 53 AUXGND In ±12 volt ground 54 AUXGND In ±12 volt ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                   |      |                    |     |                   |      |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51             | PCO               | Out  | Priority chain out | 52  | PCI               | Out  | Priority chain in   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53             | AUXGND            | In   | ±12 volt ground    | 54  | AUXGND            | In   | ±12 volt ground     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55             | AUX+V             | In   |                    | 56  | AUX-V             | In   |                     |