## **Initial PCN**

STATS ChipPAC\* Assembly Site Transfer from Shanghai to Jiangyin CHINA and Bill of Materials Substrate Core Change

Dear Customer,

This is notification of the STATS ChipPAC\* Assembly Site Transfer from Shanghai to Jiangyin CHINA and Bill of Materials Substrate Core Change. STATS ChipPAC\* was acquired by Jiangsu Changjiang Electronics Technology Co., Ltd. (JCET) in 2015. All assets will be consolidating to the JCET site location in Jiangyin CHINA targeted for the end of Q1 2017.

The described change(s) within this PCN will not take effect (i.e. Shipped) any earlier than 90 days from Initial PCN notification or the successful completion of the Cirrus Logic qualification, unless a customer agreement has been reached on an earlier implementation of the identified process change.

Cirrus Logic requests acknowledgement of receipt for this Initial PCN notification within 30 calendar days and acceptance of the identified change(s) within 90 days from receipt. Shipment of said material will commence after the 90 day period or upon successful completion of the Cirrus Logic defined qualification; lack of acknowledgement / communication is considered as acceptance.

Cirrus Logic would like to take this opportunity to thank our customers for their cooperation and assistance in this respective matter. Any specific or immediate inquiries should be directed to your local Field Sales Representative.

Sincerely,

Quality Systems Administrator Cirrus Logic Corporate Quality Phone: +1(512) 851-4000

\* - STATS ChipPAC was acquired by Jiangsu Changjiang Electronics Technology Co., Ltd. (JCET) in 2015.

Rev. 02172015A

Cirrus Logic | 800 W. 6th St., Austin, TX 78701 | 512-851-4000

Page 1 of 7

CONFIDENTIAL

www.cirrus.com

PCN Notification Date: 09/30/2016 PCN Number: PCN-2016-63

### **Products Affected:**

The devices listed on this page are the complete list of affected devices. According to our records, one or more of these devices have been purchased by your organization within the past twenty-four (24) months. The corresponding customer part number is also listed, if available.

Technical details of this Process / Product Change follow on the next page(s).

| Tit                       | ile:                        | STATS ChipPAC* Assembly Site Transfer from Shanghai to Jiangyin CHINA and Bill Of Materials Substrate Core Change |                                                                                                                                                                                                           |                          |         |                  |                     |                     |           |                   |  |

|---------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|------------------|---------------------|---------------------|-----------|-------------------|--|

| Customer Local Field Sale |                             |                                                                                                                   | es ,                                                                                                                                                                                                      |                          | Phone:  | (512) 851-4000   | ) De                | Dept: Corpora       |           | rato Quality      |  |

|                           | ontact:                     | Representative                                                                                                    | <u> </u>                                                                                                                                                                                                  | r none.                  |         | (312) 631-4000   |                     | bept.               |           | Corporate Quality |  |

| Pr                        | oposed 1 <sup>st</sup> Ship | Date:                                                                                                             | Q1_                                                                                                                                                                                                       | 2017                     | Estimat | ed Sample Availa | bility I            | Date:               |           | Q1_2017           |  |

| Change Type:              |                             |                                                                                                                   | Site Transfer: Change Type = Major, but considered Minor; as the subcontractor (STATS ChipPAC*) is an existing qualified supplier for Cirrus Logic and there are no changes to the equipment or material. |                          |         |                  |                     | qualified           |           |                   |  |

| Χ                         | Assembly Site               |                                                                                                                   |                                                                                                                                                                                                           | Assembly Process         |         | ess              |                     | Assembly Materials  |           |                   |  |

|                           | Wafer Fab Site              |                                                                                                                   |                                                                                                                                                                                                           | Wafer Fab Process        |         | ess              | W                   | Wafer Fab Materials |           | terials           |  |

|                           | Wafer Bump Site             | е                                                                                                                 |                                                                                                                                                                                                           | Wafer Bump Process       |         | ocess            | Wafer Bump Material |                     | /laterial |                   |  |

|                           | Test Site                   |                                                                                                                   |                                                                                                                                                                                                           | Test Process             |         |                  | Design              |                     |           |                   |  |

|                           | Electrical Specification    |                                                                                                                   |                                                                                                                                                                                                           | Mechanical Specification |         | cification       | Pa                  | art Nu              | ımber     |                   |  |

|                           | Packing/Shipping/Labeling   |                                                                                                                   | Χ                                                                                                                                                                                                         | Other                    |         |                  |                     | •                   |           |                   |  |

| Co                        | Comments: Substrate Core    |                                                                                                                   |                                                                                                                                                                                                           | al Chan                  | ge      |                  |                     |                     |           |                   |  |

### **PCN Details**

### **Description of Change:**

Cirrus Logic is qualifying the STATS ChipPAC\* Assembly Site Transfer from Shanghai to Jiangyin CHINA and Bill Of Materials Substrate Core Change.

Below you will find an outline of the described changes for these components:

**Special Note:** Change Type = Major, but considered Minor.

The subcontractor (STATS ChipPAC\*) is an existing qualified supplier.

### **BOM Change:**

Rev. 02172015A

Substrate Core Material

From: CCL-HL832 Series (Halogenated)

CCL-HL832NXA Series (Non-Halogenated)

**Reference**: Appendix A – Substrate Material Comparison Information

**Assembly Site Change:**

From: STATS ChipPAC\* site location in Shanghai CHINA STATS ChipPAC\* site location in Jiangyin CHINA To:

All equipment associated with the Assembly processes will remain the same Note:

Cirrus Logic | 800 W. 6th St., Austin, TX 78701 | 512-851-4000 Page 2 of 7 CONFIDENTIAL www.cirrus.com

PCN Notification Date: 09/30/2016 PCN Number: PCN-2016-63

### Reason for Change:

STATS ChipPAC\* was acquired by Jiangsu Changjiang Electronics Technology Co., Ltd. (JCET) in 2015. All assets will be consolidating to the JCET site location in Jiangyin CHINA targeted for the end of Q1\_2017.

### Special Note:

Earlier production level material may be available from the qualified Jiangyin CHINA site location, but shipment(s) from Cirrus Logic are contingent on successful qualification completion of the designated site transfer.

### Anticipated Impact on Form, Fit, Function, Quality or Reliability:

No anticipated adverse impact to the Quality and/or Reliability of said product; as the transfer site is part of an already existing Cirrus Logic qualified subcontractor STATS ChipPAC\* and there are no changes to the equipment or material.

### **Product Affected:**

## **Cirrus Logic Part Number(s):**

EP9307-CRZ[R]/E2 EP9307-IRZ[R]/E2

## **Changes To Product Identification Resulting From This PCN:**

The Cirrus Logic component symbolization on the external face of the device reflects the designated Assembly Site location. The Assembly Site Code on the external face of the designated components will change. Specifically, the 1<sup>st</sup> two characters of the PackMark will change:

"BA" From: Note: All other symbolization will remain the same.

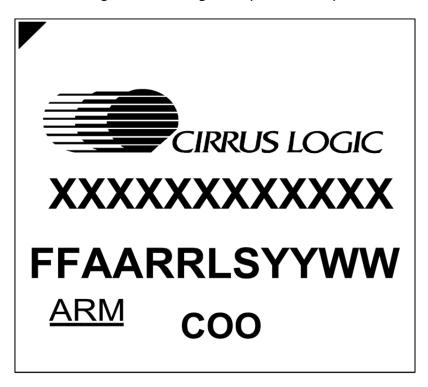

## Top Side Mark:

| Mark Lay-out | Top Side Brand                        | STATS ChipPAC<br>(Shanghai CHINA)                                                                                                                   | STATS ChipPAC<br>(Jiangyin CHINA)                                                                                                                            | Comparison<br>Results |

|--------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| See Below    | 1st Line:<br>Logo Line                | CIRRUS                                                                                                                                              | CIRRUS                                                                                                                                                       | Same                  |

| Illustration | 2nd Line:<br>Cirrus Part Number       | EP9307-xRZx                                                                                                                                         | EP9307-xRZx                                                                                                                                                  | Same                  |

|              | 3 <sup>rd</sup> Line:<br>Package Mark | (FFBARRLSYYWW) FF = Foundry Code AA = Assembly Site Code RR = Die Rev LS = Lot Sequence Code YY = Year of Manufacture WW = Work Week of Manufacture | (FF <b>BB</b> RRLSYYWW) FF = Foundry Code AA = Assembly Site Code RR = Die Rev LS = Lot Sequence Code YY = Year of Manufacture WW = Work Week of Manufacture | Different             |

Rev. 02172015A Cirrus Logic | 800 W. 6th St., Austin, TX 78701 | 512-851-4000 CONFIDENTIAL

# CIRRUS LOGIC® Process Change Notification

PCN Number: PCN-2016-63 PCN Notification Date: 09/30/2016

| 4 <sup>th</sup> Line:<br>ARM Logo                   | ARM | ARM | Same |

|-----------------------------------------------------|-----|-----|------|

| 5 <sup>th</sup> Line:<br>Country of Origin<br>(COO) | CN  | CN  | Same |

Note: \*Lot code and Date code characters vary according to the lot and timeframe of build

Below is a 2D representative image of the Package: MF (Mark Format) = 242 Rev B

### PACKAGE MARK FIELDS

12 character Package Mark appears on PO as 6 fields of 2 characters each in the following format:

**FFAARRLSYYWW**

where,

### TOP SIDE BRAND

Line 1: Logo Line. Use CIRRUS LOGIC logo as shown.

Line 2: Part Number (12 spaces max.) Line 3: Package Mark (12 spaces max.)

Line 4: ARM logo

Line 5: Country of Origin (COO).

FF = Foundry Code

AA = Assembly Site Code

RR = Die Rev Code

LS = Lot Sequence Code

YY = Year of Manufacture

WW = Work Week of Manufacture

Rev. 02172015A

Cirrus Logic | 800 W. 6th St., Austin, TX 78701 | 512-851-4000

Page 4 of 7

**CONFIDENTIAL**

www.cirrus.com

# **Family Qualification Data:**

This qualification has been specifically developed for the validation of this change. The qualification data validates that the proposed change meets the applicable released technical specifications.

| Qualification Schedule | Start: | Sep 2016 | End: | Dec 2016 |

|------------------------|--------|----------|------|----------|

|                        |        |          |      |          |

| Qualification Device Family Construction Details |                                             |                                             |                                              |  |  |  |  |

|--------------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|--|--|--|--|

| Detail Description                               | Device 1                                    | Device 2                                    | Device 3                                     |  |  |  |  |

| Part Number(s):                                  | EP9307-*RZ[R]                               | CS4208-CRZ[R]                               | JSCC Qual Vehicle                            |  |  |  |  |

| Die Size:                                        | 41.73 mm²                                   | 21.98 mm²                                   | 22.21 mm²                                    |  |  |  |  |

| Package Type/Code:                               | 272 TFBGA                                   | 129 VFBGA                                   | 285 TFBGA                                    |  |  |  |  |

| Mold Compound:                                   | Sumitomo EME-G770LC                         | Kyocera KE-G1250LKDS                        | Sumitomo EME-G750S-E                         |  |  |  |  |

| Substrate Material:                              | 2 layer, Substrate UMTC:<br>046043ESUB-A_00 | 2 layer, Substrate UMTC,<br>030848Jsub-A_07 | 4 layer, Substrate UMTC:<br>0.8P, 030356L_U2 |  |  |  |  |

| Die Attach Material:                             | Ablebond 2000                               | Ablebond 2000                               | Ablebond 2300                                |  |  |  |  |

| Wire Material:                                   | Au 2N                                       | Cu Pd                                       | EX1 Type (Cu Pd Coated)                      |  |  |  |  |

| Wire Size:                                       | 1.0 mil                                     | 0.8 mil                                     | 0.8 mil                                      |  |  |  |  |

| Solder Ball<br>Composition - Size:               | Sn / 4% Ag / 0.5% Cu – 400um                | Sn / 3% Ag / 0.5% Cu – 250um                | Sn / 3% Ag / 0.5% Cu – 300um                 |  |  |  |  |

Rev. 02172015A

The Qualification Plans are designed using JEDEC and other applicable industry standards. An overall summary of the Qualification results will be submitted upon completion.

# **Device Package Level Qualification Plan**

## **Purpose**

STATS ChipPAC\* Package level Qualification for Assembly Site Transfer from Shanghai to Jiangyin CHINA

| Stress Name                                 | Stress<br>Method                                                       | Conditions                                                                                | # of<br>Lots | Qty per<br>Lot                               | Read Points                                    | Failure<br>Criteria                | Results<br>(PASS/FAIL) |

|---------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|----------------------------------------------|------------------------------------------------|------------------------------------|------------------------|

| PC<br>(Pre-Condition)                       | JESD22-A113<br>Per component<br>MSL<br>classification per<br>J-STD-020 | Bake: 24Hr +125'C; MSL 3 192Hr 30'C /<br>60% RH Soak, (Reflow 260'C x 3)                  | 5            | Sufficient<br>for stress<br>test<br>coverage | Precon MSL3                                    | 0 fails                            |                        |

| TC<br>(Temperature Cycle)                   | JEDEC<br>JESD22-A104                                                   | -40°C to +125°C for 850 cycles or<br>-55°C to +125°C for 1000 cycles<br>Post Precondition | 5            | 77                                           | 850 or 1000 Cycles                             | 0 fails                            |                        |

| THB / BHAST<br>(Temperature- Humidity-Bias) | JEDEC<br>JESD22-A101<br>and A110                                       | 85°C/85% RH/1000 Hrs /<br>+110'C 85% RH 264 Hrs                                           | 4            | 77                                           | 1000 / 264 Hrs                                 | 0 fails                            |                        |

| UHAST<br>(Unbiased HAST)                    | JEDEC<br>JESD22-A118                                                   | +110'C/85% RH, 17.7 PSIA, 264Hrs                                                          | 5            | 77                                           | 264 Hrs                                        | 0 fails                            |                        |

| HTSL<br>(High Temperature Storage Life)     | JEDEC<br>JESD22-A103                                                   | +150°C for 1000Hrs                                                                        | 3            | 45                                           | 1000 Hrs                                       | 0 fails                            |                        |

| WBP<br>(Wire Bond Pull)                     | MIL-STD-883<br>M2011                                                   | Paragraph 3 of Reference Specification<br>Table 1<br>Figure 2011-2                        |              |                                              |                                                | 0 fails                            |                        |

| WBS<br>(Wire Bond Shear)                    | JESD22-B116                                                            |                                                                                           |              |                                              |                                                | 0 fails                            |                        |

| PPD<br>(Package Physical Dimensions)        | Case Outline<br>Drawing                                                |                                                                                           |              |                                              | Meet all case<br>outline drawing<br>tolerances | No deviations from package drawing |                        |

### Notes:

Qualification tests "pass" on zero fails for each test

Rev. 02172015A

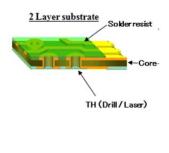

# **Appendix A - Substrate Material Comparison Information**

# **Nexus 2 Layer Substrate Cross Section**

| Layer             | Current                           | New                               |           |

|-------------------|-----------------------------------|-----------------------------------|-----------|

| Top Pad Finish    | Ni 5um<br>Au 0.5 um (Min)         | Ni 5um<br>Au 0.5 um (Min)         | No Change |

| Solder Mask       | AUS303                            | AUS303                            | No Change |

| Copper Trace      | Cu Foil 12 um<br>Cu Plating 15 um | Cu Foil 12 um<br>Cu Plating 15 um | No Change |

| Core Material     | HL832                             | HL832NXA-EX                       | Changed   |

| Copper Trace      | Cu Foil 12 um<br>Cu Plating 15 um | Cu Foil 12 um<br>Cu Plating 15 um | No Change |

| Solder Mask       | AUS303                            | AUS303                            | No Change |

| Bottom Pad Finish | Ni 5um<br>Au 0.5 – 1.0 um         | Ni 5um<br>Au 0.5 – 1.0 um         | No Change |

Note: There are no changes to the Top/Bottom Pad, Solder Mask or Copper Trace material

# **Existing Non-NXA material versus NXA Core Material Comparison**

| Item                       | Con                                                    | dition  | Unit     | HL832              | HL832NX<br>type A      |  |

|----------------------------|--------------------------------------------------------|---------|----------|--------------------|------------------------|--|

|                            | DMA<br>TMA                                             |         | degC     | 210                | 230                    |  |

| Тд                         |                                                        |         | degC     | 180                | 200                    |  |

|                            | 101                                                    | < Tg    | ppm/degC | 15                 | 14                     |  |

|                            | XY                                                     | > Tg    | ppm/degC | 5                  | 5                      |  |

| CTE                        |                                                        | < Tg    | ppm/degC | 55                 | 30                     |  |

|                            | Z                                                      | > Tg    | ppm/degC | 220                | 140                    |  |

| Cu peel strength           | 12um Cu (UP) 25degC 25degC 25degC 25degC 25degC 25degC |         | kN/m     | 0.9                | 0.85                   |  |

| Rexural strength           |                                                        |         | MPa      | 550                | 450                    |  |

| Flexural modulus           |                                                        |         | GPa      | 24                 | 28                     |  |

| Tensile strength           |                                                        |         | MPa      | 320                | 270                    |  |

| Youngs modulus             |                                                        |         | GPa      | 24                 | 28                     |  |

| Poisson ratio              |                                                        |         |          | 0.18               | 0.19                   |  |

| Thermal conductivity       |                                                        |         | W/mK     | 0.30               | 0.80                   |  |

| Moisture absorption        | C168                                                   | 8/85/85 | wt%      | 0.42               | 0.44                   |  |

| Dielectric constant        | 1                                                      | GHz     | 100      | 4.3                | 4.9                    |  |

| Dissipation factor         | 1                                                      | GHz     |          | 0.016              | 0.011                  |  |

| Hame resistance<br>(Green) | Б1                                                     | 68 / 70 | UL94     | V-0<br>Halogenated | V-0<br>Non Halogenated |  |

Note: NXA material has a higher Tg, lower CTE and is Non-Halogenated