#### CHANGE NOTIFICATION

October 6, 2016

Dear Sir/Madam: PCN#100616

### Subject: Notification of Change to LTC2440, LTC2442, LTC2444, LTC2445, LTC2446, LTC2447, LTC2448, LTC2449 Datasheets

Please be advised that Linear Technology Corporation has made a change to the datasheet specifications of subject devices in order to improve device manufacturability. The changes are mentioned below.

The Maximum External Oscillator Frequency (f<sub>EOSC</sub>) in the Timing Characteristics is being reduced from 20MHz to 12MHz. There are many applications that are using the part at 20MHz and the performance is perfectly adequate. But at 20MHz, performance is reduced from the limits guaranteed in the specification table. This change is intended to apply to future customer designs. No changes are being made to the circuit or the test methodology, so customers who are using these devices with F0 frequencies between 12MHz and 20MHz and are satisfied with the performance will continue to receive the same product.

An error in the Conversion Time calculation using the External Oscillator was corrected to display 178 in the calculation (incorrectly shown as 170). No changes are being made to all devices or test program, this is just a change to the datasheet. The changes are shown on the attached pages of the marked up datasheet. There was no change in form, fit, function, test programs, quality or reliability of the product; this is just a change to the datasheet. New customer designs after December 6, 2014 should adhere to the new datasheet limit.

Should you have any further questions, please feel free to contact your local Linear Technology sales person or you may contact me at 408-432-1900 ext. 2077, or by E-mail <u>JASON.HU@LINEAR.COM</u>. If I do not hear from you by December 06, 2016, we will consider this change approved by your company.

Sincerely,

Jason Hu Quality Assurance Engineer

### **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

|                 | -                                               | •                                                 |   |     |     |          |          |

|-----------------|-------------------------------------------------|---------------------------------------------------|---|-----|-----|----------|----------|

| SYMBOL          | PARAMETER                                       | CONDITIONS                                        |   | MIN | TYP | MAX      | UNITS    |

| V <sub>CC</sub> | Supply Voltage                                  |                                                   | • | 4.5 |     | 5.5      | V        |

| Icc             | Supply Current<br>Conversion Mode<br>Sleep Mode | CS = 0V (Note 7)<br>CS = V <sub>CC</sub> (Note 7) | • |     | 8   | 11<br>30 | mA<br>μΑ |

### **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                             |   | MIN         | TYP                                       | MAX              | UNITS     |

|------------------------|--------------------------------------|------------------------------------------------------------------------|---|-------------|-------------------------------------------|------------------|-----------|

| f <sub>EOSC</sub>      | External Oscillator Frequency Range  |                                                                        | • | 0.1         |                                           | 12 <del>20</del> | MHz       |

| t <sub>HEO</sub>       | External Oscillator High Period      |                                                                        | • | 25          |                                           | 10000            | ns        |

| t <sub>LEO</sub>       | External Oscillator Low Period       |                                                                        | • | 25          |                                           | 10000            | ns        |

| t <sub>CONV</sub>      | Conversion Time                      | OSR = 256 (SDI = 0)<br>OSR = 32768 (SDI = 1)                           | : | 0.99<br>126 | 1.13<br>145                               | 1.33<br>170      | ms<br>ms  |

|                        |                                      | External Oscillator (Note 10, 13)                                      | • |             | 40 • OSR + 176<br>f <sub>EOSC</sub> (kHz) | <u>−</u> 178     | ms        |

| f <sub>ISCK</sub>      | Internal SCK Frequency               | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10)      | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10              | 1                | MHz<br>Hz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Note 9)                                                               | • | 45          |                                           | 55               | %         |

| fesck                  | External SCK Frequency Range         | (Note 8)                                                               | • |             |                                           | 20               | MHz       |

| t <sub>LESCK</sub>     | External SCK Low Period              | (Note 8)                                                               | • | 25          |                                           |                  | ns        |

| t <sub>HESCK</sub>     | External SCK High Period             | (Note 8)                                                               | • | 25          |                                           |                  | ns        |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | • | 30.9        | 35.3<br>320/f <sub>E0SC</sub>             | 41.6             | μs<br>s   |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time | (Note 8)                                                               | • |             | 32/f <sub>ESCK</sub>                      |                  | s         |

| t <sub>1</sub>         | CS ↓to SD0 Low Z                     | (Note 12)                                                              | • | 0           |                                           | 25               | ns        |

| t <sub>2</sub>         | CS ↑ to SDO High Z                   | (Note 12)                                                              | • | 0           |                                           | 25               | ns        |

| t <sub>3</sub>         | CS ↓ to SCK ↓                        | (Note 9)                                                               | • |             | 5                                         |                  | μs        |

| t <sub>4</sub>         | CS ↓ to SCK ↑                        | (Notes 8, 12)                                                          | • | 25          |                                           |                  | ns        |

| t <sub>KOMAX</sub>     | SCK ↓ to SDO Valid                   |                                                                        | • |             |                                           | 25               | ns        |

| t <sub>KOMIN</sub>     | SDO Hold After SCK ↓                 | (Note 5)                                                               | • | 15          |                                           |                  | ns        |

| t <sub>5</sub>         | SCK Set-Up Before CS↓                |                                                                        | • | 50          |                                           |                  | ns        |

| t <sub>7</sub>         | SDI Setup Before SCK ↑               | (Note 5)                                                               | • | 10          |                                           |                  | ns        |

| t <sub>8</sub>         | SDI Hold After SCK ↑                 | (Note 5)                                                               | • | 10          |                                           |                  | ns        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to GND.

Note 3:  $V_{CC} = 4.5$  to 5.5V unless otherwise specified.

$V_{REF} = REF^+ - REF^-, V_{REFCM} = (REF^+ + REF^-)/2;$

$V_{IN} = IN^+ - IN^-, V_{INCM} = (IN^+ + IN^-)/2.$

Note 4:  $f_Q$  pin tied to GND or to external conversion clock source with  $f_{EOSC} = 10 MHz$  unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band. Note 7: The converter uses the internal oscillator.

Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>ESCK</sub> and is expressed in Hz.

**Note 9:** The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of C<sub>LOAD</sub> = 20pF.

Note 10: The external oscillator is connected to the  $f_0$  pin. The external oscillator frequency,  $f_{EOSC}$ , is expressed in kHz.

Note 11: The converter uses the internal oscillator,  $f_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional to the conversion time.

5 to 15 f<sub>0</sub> cycle to

TIMEAD

The sample rate  $f_S$  and NULL  $f_N$ , my also be adjusted by driving the  $f_O$  pin with an external oscillator. The sample rate is  $f_S = f_{EOSC}/5$ , where  $f_{EOSC}$  is the frequency of the clock applied to  $f_O$ . Combining a large OSR with a reduced sample rate leads to notch frequencies  $f_N$  near DC while maintaining simple antialiasing requirements. A 100kHz clock applied to  $f_O$  results in a NULL at 0.6Hz plus all harmonics up to 20kHz, see Figure 14. This is useful in applications requiring digitalization of the DC component of a noisy input signal and eliminates the need of placing a 0.6Hz filter in front of the ADC.

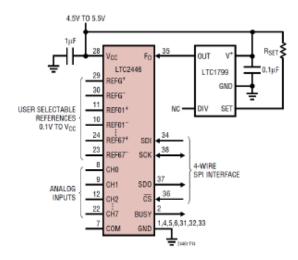

An external oscillator operating from 100kHz to 26MHz can be implemented using the LTC1799 (resistor set SOT-23 oscillator), see Figure 22. By floating pin 4 (DIV) of the LTC1799, the output oscillator frequency is:

$$f_{OSC} = 10MHz \cdot \left(\frac{10k}{10 \cdot R_{SET}}\right)$$

The normal mode rejection characteristic shown in Figure 14 is achieved by applying the output of the LTC1799 (with  $R_{SET} = 100k$ ) to the  $f_0$  pin on the LTC2440 with SDI tied HIGH (OSR = 32768).

#### Reduced Power Operation

In addition to adjusting the speed/resolution of the LTC2440, the speed/resolution/power dissipation may also be adjusted using the automatic sleep mode. During the conversion cycle, the LTC2440 draws 8mA supply current independent of the programmed speed. Once the conversion cycle is completed, the device automatically enters a low power sleep state drawing 8 $\mu$ A. The device remains in this state as long as  $\overline{\text{CS}}$  is HIGH and data is not shifted out. By adjusting the duration of the sleep state (hold  $\overline{\text{CS}}$  HIGH longer) and the duration of the conversion cycle (programming OSR) the DC power dissipation can be reduced, see Figure 16.

For example, if the OSR is programmed at the fastest rate (OSR = 64,  $t_{CONV} = 0.285 ms$ ) and the sleep state is 10ms, the effective output rate is approximately 100Hz while the average supply current is reduced to 240 $\mu$ A. By further extending the sleep state to 100ms, the effective output rate of 10Hz draws on average 30 $\mu$ A. Noise, power, and speed can be optimized by adjusting the OSR (Noise/Speed) and sleep mode duration (Power).

Figure 14. LTC2440 Normal Mode Rejection (External Oscillator at 90kHz)

2440fc

#### TIMING CHARACTERISTICS The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°C. (Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                             |   | MIN         | TYP                                                 | MAX                 | UNITS     |

|------------------------|--------------------------------------|------------------------------------------------------------------------|---|-------------|-----------------------------------------------------|---------------------|-----------|

| feosc                  | External Oscillator Frequency Range  |                                                                        | • | 0.1         |                                                     | 12 <del>-20 -</del> | MHz       |

| t <sub>HEO</sub>       | External Oscillator High Period      |                                                                        | • | 25          |                                                     | 10000               | ns        |

| t <sub>LEO</sub>       | External Oscillator Low Period       |                                                                        | • | 25          |                                                     | 10000               | ns        |

| tconv                  | Conversion Time                      | OSR = 256 (SDI = 0)<br>OSR = 32768 (SDI = 1)                           | • | 0.99<br>126 | 1.13<br>145                                         | 1.33<br>170         | ms<br>ms  |

|                        |                                      | External Oscillator (Notes 10, 13)<br>1x Mode                          | • |             | 40 • OSR + <del>17</del><br>f <sub>EOSC</sub> (KHz) | <del>'0-</del> 178  | ms        |

| fisck                  | Internal SCK Frequency               | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10)      | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10                        | 1                   | MHz<br>Hz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Note 9)                                                               | • | 45          |                                                     | 55                  | %         |

| f <sub>ESCK</sub>      | External SCK Frequency Range         | (Note 8)                                                               | • |             |                                                     | 20                  | MHz       |

| fLESCK                 | External SCK Low Period              | (Note 8)                                                               | • | 25          |                                                     |                     | ns        |

| thesck                 | External SCK High Period             | (Note 8)                                                               | • | 25          |                                                     |                     | ns        |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | : | 30.9        | 35.3<br>320/f <sub>EOSC</sub>                       | 41.6                | μs<br>s   |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time | (Note 8)                                                               | • |             | 32/f <sub>ESCK</sub>                                |                     | s         |

| t <sub>1</sub>         | CS ↓ to SDO Low Z                    | (Note 12)                                                              | • | 0           |                                                     | 25                  | ns        |

| t <sub>2</sub>         | CS ↑ to SDO High Z                   | (Note 12)                                                              | • | 0           |                                                     | 25                  | ns        |

| t <sub>3</sub>         | CS ↓ to SCK ↓                        | (Note 9)                                                               |   |             | 5                                                   |                     | μs        |

| t <sub>4</sub>         | CS ↓ to SCK ↑                        | (Note 8, 12)                                                           | • | 25          |                                                     |                     | ns        |

| tkamax                 | SCK ↓ to SDO Valid                   |                                                                        | • |             |                                                     | 25                  | ns        |

| t <sub>KOMIN</sub>     | SDO Hold After SCK ↓                 | (Note 5)                                                               | • | 15          |                                                     |                     | ns        |

| t <sub>5</sub>         | SCK Setup Before CS ↓                |                                                                        | • | 50          |                                                     |                     | ns        |

| t <sub>6</sub>         | SCK Hold After CS ↓                  |                                                                        | • |             |                                                     | 50                  | ns        |

| t <sub>7</sub>         | SDI Setup Before SCK ↑               | (Note 5)                                                               | • | 10          |                                                     |                     | ns        |

| t <sub>8</sub>         | SDI Hold After SCK ↑                 | (Note 5)                                                               | • | 10          |                                                     |                     | ns        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to GND.

Note 3: V<sub>CC</sub> = 4.5V to 5.5V unless otherwise specified.

$V_{REF} = REF^{+} - REF^{-}, V_{REFCM} = (REF^{+} + REF^{-})/2;$   $V_{IN} = SEL^{+} - SEL^{-}, V_{INCM} = (SEL^{+} + SEL^{-})/2.$

Note 4: Fo pin tied to GND or to external conversion clock source with

feosc = 10MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7: The converter uses the internal oscillator.

Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>ESCK</sub> and is expressed in Hz.

Note 9: The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of CLOAD = 20pF.

Note 10: The external oscillator is connected to the Fo pin. The external oscillator frequency, fEOSC, is expressed in Hz.

Note 11: The converter uses the internal oscillator. Fo = 0V.

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional 1µs (typ) to the 5 to 15 fo cycle to the

Note 14: In order to achieve optimum linearity, the amplifier power positive supply input (V+) must exceed the maximum input voltage level by 2V or greater. The negative amplifier power supply input (VT) must be at least 200mV below the minimum input voltage level.

Note 15: Amplifiers are externally compensated with 0.1 µF.

For more information www.linear.com/LTC2442

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \, ^{\circ}\text{C}$ . (Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                             |   | MIN         | TYP                                                 | MAX                 | UNITS     |

|------------------------|--------------------------------------|------------------------------------------------------------------------|---|-------------|-----------------------------------------------------|---------------------|-----------|

| feosc                  | External Oscillator Frequency Range  |                                                                        | • | 0.1         |                                                     | 12 <del>-20 -</del> | MHz       |

| t <sub>HEO</sub>       | External Oscillator High Period      |                                                                        | • | 25          |                                                     | 10000               | ns        |

| t <sub>LEO</sub>       | External Oscillator Low Period       |                                                                        | • | 25          |                                                     | 10000               | ns        |

| tconv                  | Conversion Time                      | OSR = 256 (SDI = 0)<br>OSR = 32768 (SDI = 1)                           | • | 0.99<br>126 | 1.13<br>145                                         | 1.33<br>170         | ms<br>ms  |

|                        |                                      | External Oscillator (Notes 10, 13)<br>1x Mode                          | • |             | 40 • OSR + <del>17</del><br>f <sub>EOSC</sub> (KHz) |                     | ms        |

| fisck                  | Internal SCK Frequency               | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10)      | • | 0.8         | 0.9<br>f <sub>E0SC</sub> /10                        | 1                   | MHz<br>Hz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Note 9)                                                               | • | 45          |                                                     | 55                  | %         |

| fesck                  | External SCK Frequency Range         | (Note 8)                                                               | • |             |                                                     | 20                  | MHz       |

| fLESCK                 | External SCK Low Period              | (Note 8)                                                               | • | 25          |                                                     |                     | ns        |

| thesck                 | External SCK High Period             | (Note 8)                                                               | • | 25          |                                                     |                     | ns        |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | • | 30.9        | 35.3<br>320/f <sub>EOSC</sub>                       | 41.6                | μs<br>s   |

| tDOUT_ESCK             | External SCK 32-Bit Data Output Time | (Note 8)                                                               | • |             | 32/f <sub>ESCK</sub>                                |                     | s         |

| t <sub>1</sub>         | CS ↓ to SD0 Low Z                    | (Note 12)                                                              | • | 0           |                                                     | 25                  | ns        |

| t <sub>2</sub>         | CS ↑ to SD0 High Z                   | (Note 12)                                                              | • | 0           |                                                     | 25                  | ns        |

| t <sub>3</sub>         | CS ↓ to SCK ↓                        | (Note 9)                                                               |   |             | 5                                                   |                     | μs        |

| t <sub>4</sub>         | CS ↓ to SCK ↑                        | (Note 8, 12)                                                           | • | 25          |                                                     |                     | ns        |

| †KOMAX                 | SCK ↓ to SDO Valid                   |                                                                        | • |             |                                                     | 25                  | ns        |

| t <sub>KOMIN</sub>     | SDO Hold After SCK ↓                 | (Note 5)                                                               | • | 15          |                                                     |                     | ns        |

| t <sub>5</sub>         | SCK Setup Before CS ↓                |                                                                        | • | 50          |                                                     |                     | ns        |

| t <sub>6</sub>         | SCK Hold After CS ↓                  |                                                                        | • |             |                                                     | 50                  | ns        |

| t <sub>7</sub>         | SDI Setup Before SCK ↑               | (Note 5)                                                               | • | 10          |                                                     |                     | ns        |

| t <sub>8</sub>         | SDI Hold After SCK ↑                 | (Note 5)                                                               | • | 10          |                                                     |                     | ns        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to GND.

Note 3:  $V_{CC} = 4.5V$  to 5.5V unless otherwise specified.

$V_{REF} = REF^+ - REF^-, V_{REFCM} = (REF^+ + REF^-)/2;$

$V_{IN} = SEL^+ - SEL^-$ ,  $V_{INCM} = (SEL^+ + SEL^-)/2$ .

Note 4:  $F_0$  pin tied to GND or to external conversion clock source with  $f_{EOSC} = 10$ MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7: The converter uses the internal oscillator.

**Note 8:** The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>ESCK</sub> and is expressed in Hz.

Note 9: The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of  $C_{LOAD} = 20pF$ .

Note 10: The external oscillator is connected to the  $F_0$  pin. The external oscillator frequency,  $f_{EOSC}$ , is expressed in Hz.

Note 11: The converter uses the internal oscillator,  $F_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional 14x (typ) to the conversion time. 5 to 15 f<sub>0</sub> cycle to the

Note 14: In order to achieve optimum linearity, the amplifier power positive supply input (V\*) must exceed the maximum input voltage level by 2V or greater. The negative amplifier power supply input (V\*) must be at least 200mV below the minimum input voltage level.

Note 15: Amplifiers are externally compensated with 0.1 µF.

2442fa

If  $F_0$  is grounded,  $f_S$  is set by the on-chip oscillator at 1.8MHz $_{\pm}$ 5% (over supply and temperature variations). At an OSR of 32,768, the first NULL is at  $f_N = 55$ Hz and the no latency output rate is  $f_N/8 = 6.9$ Hz. At the maximum OSR, the noise performance of the device is 220nV $_{RMS}$  with better than 80dB rejection of 50Hz  $\pm$ 2% and 60Hz  $\pm$ 2%. Since the OSR is large (32,768) the wide band rejection is extremely large and the antialiasing requirements are simple. The first multiple of  $f_S$  occurs at 55Hz • 32,768 = 1.8MHz, see Figure 12.

The first NULL becomes  $f_N = 7.03 \, \text{kHz}$  with an OSR of 256 (an output rate of 879Hz) and  $F_0$  grounded. While the NULL has shifted, the sample rate remains constant. As a result of constant modulator sampling rate, the linearity, offset and full-scale performance remains unchanged as does the first multiple of  $f_S$ .

The sample rate  $f_S$  and NULL  $f_N$ , may also be adjusted by driving the  $F_O$  pin with an external oscillator. The sample rate is  $f_S = f_{EOSC}/5$ , where  $f_{EOSC}$  is the frequency of the

sample rate leads to notch frequencies f<sub>N</sub> near DC while maintaining simple antialiasing requirements. A 100kHz clock applied to F<sub>O</sub> results in a NULL at 0.6Hz plus all harmonics up to 20kHz, see Figure 13. This is useful in applications requiring digitalization of the DC component of a noisy input signal and eliminates the need of placing a 0.6Hz filter in front of the ADC.

An external oscillator operating from 100kHz to 20MHz can

clock applied to F<sub>0</sub>. Combining a large OSR with a reduced

An external oscillator operating from 100kHz to 29MHz can be implemented using the LTC1799 (resistor set SOT-23 oscillator), see Figure 14. By floating pin 4 (DIV) of the LTC1799, the output oscillator frequency is:

$$f_{OSC} = 10MHz \cdot \left(\frac{10k}{10 \cdot R_{SET}}\right)$$

The normal mode rejection characteristic shown in Figure 13 is achieved by applying the output of the LTC1799 (with  $R_{SET} = 100k$ ) to the  $F_0$  pin on the LTC2442 with OSR = 32.768.

Figure 12. Normal Mode Rejection (Internal Oscillator)

Figure 13. Normal Mode Rejection (Internal Oscillator at 90kHz)

**TUNEAR**

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL          | PARAMETER                                                             | CONDITIONS                                  |   | MIN                    | TYP | MAX  | UNITS |

|-----------------|-----------------------------------------------------------------------|---------------------------------------------|---|------------------------|-----|------|-------|

| V <sub>IH</sub> | High Level Input Voltage<br>CS, F <sub>0</sub> . SDI                  | $4.5V \le V_{QC} \le 5.5V$                  | • | 2.5                    |     |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage<br>CS, F <sub>0</sub> . SDI                   | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V               | • |                        |     | 0.8  | V     |

| V <sub>IH</sub> | High Level Input Voltage<br>SCK                                       | $4.5V \le V_{CC} \le 5.5V \text{ (Note 8)}$ | • | 2.5                    |     |      | ٧     |

| V <sub>IL</sub> | Low Level Input Voltage<br>SCK                                        | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V (Note 8)      | • |                        |     | 0.8  | V     |

| IIN             | Digital Input Current<br>CS, F <sub>0</sub> , EXT, <del>301</del> SDI | $0V \le V_{IN} \le V_{CC}$                  | • | -10                    |     | 10   | μА    |

| IIN             | Digital Input Current<br>SCK                                          | $0V \le V_{IN} \le V_{CC}$ (Note 8)         | • | -10                    |     | 10   | μА    |

| CIN             | Digital Input Capacitance<br>CS, F <sub>D</sub> , SDI                 |                                             |   |                        | 10  |      | pF    |

| CIN             | Digital Input Capacitance<br>SCK                                      | (Note 8)                                    |   |                        | 10  |      | pF    |

| V <sub>OH</sub> | High Level Output Voltage<br>SDO, BUSY                                | I <sub>O</sub> = -800µA                     | • | V <sub>CC</sub> - 0.5V |     |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SDO, BUSY                                 | I <sub>O</sub> = 1.6mA                      | • |                        |     | 0.4V | V     |

| V <sub>OH</sub> | High Level Output Voltage<br>SCK                                      | I <sub>O</sub> = -800μA (Note 9)            | • | V <sub>CC</sub> - 0.5V |     |      | V     |

| Vol             | Low Level Output Voltage<br>SCK                                       | I <sub>O</sub> = 1.6mA (Note 9)             | • |                        |     | 0.4V | V     |

| loz             | Hi-Z Output Leakage<br>SDO                                            |                                             | • | -10                    |     | 10   | μA    |

|                 |                                                                       |                                             |   |                        |     |      |       |

## **POWER REQUIREMENTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL | PARAMETER                                       | CONDITIONS                                                                         |   | MIN | TYP | MAX      | UNITS    |

|--------|-------------------------------------------------|------------------------------------------------------------------------------------|---|-----|-----|----------|----------|

| Vcc    | Supply Voltage                                  |                                                                                    | • | 4.5 |     | 5.5      | V        |

| loc    | Supply Current<br>Conversion Mode<br>Sleep Mode | $\overline{CS} = 0V \text{ (Note 7)}$<br>$\overline{CS} = V_{CC} \text{ (Note 7)}$ | : |     | 8   | 11<br>30 | mΑ<br>μΑ |

# **TIMING CHARACTERISTICS** The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL           | PARAMETER                           | CONDITIONS                                                        |   | MIN         | TYP                          | MAX                 | UNITS     |

|------------------|-------------------------------------|-------------------------------------------------------------------|---|-------------|------------------------------|---------------------|-----------|

| feosc            | External Oscillator Frequency Range |                                                                   | • | 0.1         |                              | 12 <del>-20 -</del> | MHz       |

| †HEO             | External Oscillator High Period     |                                                                   | • | 25          |                              | 10000               | ns        |

| t <sub>LEO</sub> | External Oscillator Low Period      |                                                                   | • | 25          |                              | 10000               | ns        |

| tconv            | Conversion Time                     | OSR = 256 (SDI = 0)<br>OSR = 32768 (SDI = 1)                      | : | 0.99<br>126 | 1.13<br>145                  | 1.33<br>170         | ms<br>ms  |

|                  |                                     | External Oscillator (Notes 10, 13)  1x Mode                       | • |             | 40 • OSR •<br>feosc (kH      |                     | ms        |

| fisck            | Internal SCK Frequency              | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10) | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10 | 1                   | MHz<br>Hz |

**TUNEAR**

#### TIMING CHARACTERISTICS The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°C. (Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                             |   | MIN  | TYP                           | MAX  | UNITS   |

|------------------------|--------------------------------------|------------------------------------------------------------------------|---|------|-------------------------------|------|---------|

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Note 9)                                                               | • | 45   |                               | 55   | %       |

| f <sub>ESCK</sub>      | External SCK Frequency Range         | (Note 8)                                                               | • |      |                               | 20   | MHz     |

| t <sub>LESCK</sub>     | External SCK Low Period              | (Note 8)                                                               | • | 25   |                               |      | ns      |

| t <sub>HESCK</sub>     | External SCK High Period             | (Note 8)                                                               | • | 25   |                               |      | ns      |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | • | 41.6 | 35.3<br>320/f <sub>EOSC</sub> | 30.9 | μs<br>s |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time | (Note 8)                                                               | • |      | 32/f <sub>ESCK</sub>          |      | S       |

| t <sub>1</sub>         | CS ↓ to SDO Low Z                    | (Note 12)                                                              | • | 0    |                               | 25   | ns      |

| t <sub>2</sub>         | CS ↑ to SDO High Z                   | (Note 12)                                                              | • | 0    |                               | 25   | ns      |

| t <sub>3</sub>         | CS ↓ to SCK ↓                        | (Note 9)                                                               |   |      | 5                             |      | μs      |

| t <sub>4</sub>         | CS ↓ to SCK ↑                        | (Notes 8, 12)                                                          | • | 25   |                               |      | ns      |

| t <sub>KOMAX</sub>     | SCK ↓ to SDO Valid                   |                                                                        | • |      |                               | 25   | ns      |

| t <sub>KOMIN</sub>     | SDO Hold After SCK ↓                 | (Note 5)                                                               | • | 15   |                               |      | ns      |

| t <sub>5</sub>         | SCK Set-Up Before CS ↓               |                                                                        | • | 50   |                               |      | ns      |

| t <sub>6</sub>         | SCK Hold After CS ↓                  |                                                                        | • |      |                               | 50   | ns      |

| t <sub>7</sub>         | SDI Set-Up Before SCK ↑              | (Note 5)                                                               | • | 10   |                               |      | ns      |

| t <sub>8</sub>         | SDI Hold After SCK 1                 | (Note 5)                                                               | • | 10   |                               |      | ns      |

|                        |                                      |                                                                        |   |      |                               |      |         |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to GND.

Note 3:  $V_{CC} = 4.5V$  to 5.5V unless otherwise specified.  $V_{REF} = REF^+ - REF^-$ ,  $V_{REFCM} = (REF^+ + REF^-)/2$ ;  $V_{IN} = IN^+ - IN^-$ ,  $V_{INCM} = (IN^+ + IN^-)/2$ .

Note 4: Fo pin tied to GND or to external conversion clock source with

fEOSC = 10MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7: The converter uses the internal oscillator.

Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>ESCK</sub> and is expressed in Hz

Note 9: The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of CLOAD = 20pF.

Note 10: The external oscillator is connected to the Fo pin. The external oscillator frequency, f<sub>EOSC</sub>, is expressed in Hz.

Note 11: The converter uses the internal oscillator.  $F_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional 4uc (typ) to the conversion time. 5 to 15 fo cycle to the

### PIN FUNCTIONS

GND (Pins 1, 4, 5, 6, 31, 32, 33): Ground. Multiple ground pins internally connected for optimum ground current flow and V<sub>CC</sub> decoupling. Connect each one of these pins to a common ground plane through a low impedance connection. All 7 pins must be connected to ground for proper operation.

BUSY (Pin 2): Conversion in Progress Indicator. This pin is HIGH while the conversion is in progress and goes LOW indicating the conversion is complete and data is ready. It remains LOW during the sleep and data output states. At the conclusion of the data output state, it goes HIGH indicating a new conversion has begun.

EXT (Pin 3): Internal/External SCK Selection Pin. This pin is used to select internal or external SCK for outputting/ inputting data. If EXT is tied low, the device is in the external SCK mode and data is shifted out of the device under the control of a user applied serial clock. If EXT is tied high, the internal serial clock mode is selected. The device generates its own SCK signal and outputs this on the SCK pin. A framing signal BUSY (Pin 2) goes low indicating data is being output.

COM (Pin 7): The common negative input (IN-) for all single ended multiplexer configurations. The voltage on CH0-CH15 and COM pins can have any value between

If  $F_0$  is grounded,  $f_S$  is set by the on-chip oscillator at 1.8MHz $\pm 5\%$  (over supply and temperature variations). At an OSR of 32,768, the first NULL is at  $f_N$  = 55Hz and the no latency output rate is  $f_N$ /8 = 6.9Hz. At the maximum OSR, the noise performance of the device is 280nV<sub>RMS</sub> (LTC2444/LTC2448) and 200nV<sub>RMS</sub> (LTC2445/LTC2449) with better than 80dB rejection of 50Hz $\pm 2\%$  and 60Hz $\pm 2\%$ . Since the OSR is large (32,768) the wide band rejection is extremely large and the antialiasing requirements are simple. The first multiple of  $f_S$  occurs at 55Hz • 32,768 = 1.8MHz, see Figure 12.

The first NULL becomes  $f_N = 7.04 kHz$  with an OSR of 256 (an output rate of 880Hz) and  $F_O$  grounded. While the NULL has shifted, the sample rate remains constant. As a result of constant modulator sampling rate, the linearity, offset and full-scale performance remains unchanged as does the first multiple of  $f_S$ .

The sample rate  $f_S$  and NULL  $f_N$ , may also be adjusted by driving the  $F_O$  pin with an external oscillator. The sample rate is  $f_S = f_{FOSC}/5$ , where  $f_{FOSC}$  is the frequency of the

Figure 12. LTC2444/LTC2445/LTC2448/LTC2449 Normal Mode Rejection (Internal Oscillator)

clock applied to  $F_0$ . Combining a large OSR with a reduced sample rate leads to notch frequencies  $f_N$  near DC while maintaining simple antialiasing requirements. A 100kHz clock applied to  $F_0$  results in a NULL at 0.6Hz plus all harmonics up to 20kHz, see Figure 13. This is useful in applications requiring digitalization of the DC component of a noisy input signal and eliminates the need of placing a 0.6Hz filter in front of the ADC.

An external oscillator operating from 100kHz to 20MHz can be implemented using the LTC1799 (resistor set SOT-23 oscillator), see Figure 16. By floating pin 4 (DIV) of the LTC1799, the output oscillator frequency is:

$$f_{OSC} = 10MHz \cdot \left(\frac{10k}{10 \cdot R_{SET}}\right)$$

The normal mode rejection characteristic shown in Figure 13 is achieved by applying the output of the LTC1799 (with  $R_{SET} = 100k$ ) to the  $F_0$  pin on the LTC2444/LTC2445/LTC2448/LTC2449 with SDI tied HIGH (OSR = 32768).

Figure 13. LTC2444/LTC2445/LTC2448/LTC2449 Normal Mode Rejection (External Oscillator at 90kHz)

24445890

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL          | PARAMETER                                                               | CONDITIONS                                                              |   | MIN                    | TYP | MAX               | UNITS |

|-----------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|---|------------------------|-----|-------------------|-------|

| V <sub>IH</sub> | High Level Input Voltage<br>CS, F <sub>0</sub> , SDI                    | $4.5V \le V_{CC} \le 5.5V$                                              | • | 2.5                    |     |                   | V     |

| VIL             | Low Level Input Voltage<br>CS, F <sub>0</sub> , SDI                     | $4.5 \text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$                | • |                        |     | 8.0               | V     |

| V <sub>IH</sub> | High Level Input Voltage<br>SCK                                         | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V (Note 8)                                  | • | 2.5                    |     |                   | V     |

| VIL             | Low Level Input Voltage<br>SCK                                          | $4.5\text{V} \le \text{V}_{\text{CC}} \le 5.5\text{V} \text{ (Note 8)}$ | • |                        |     | 0.8               | V     |

| I <sub>IN</sub> | Digital Input Current<br>CS, F <sub>0</sub> , EXT, <del>COI -</del> SDI | $0V \le V_{IN} \le V_{CC}$                                              | • | -10                    |     | 10                | μА    |

| I <sub>IN</sub> | Digital Input Current<br>SCK                                            | $0V \le V_{IN} \le V_{CC} \text{ (Note 8)}$                             | • | -10                    |     | 10                | μА    |

| CIN             | Digital Input Capacitance<br>CS, F <sub>0</sub> , SDI                   |                                                                         |   |                        | 10  |                   | pF    |

| CIN             | Digital Input Capacitance<br>SCK                                        | (Note 8)                                                                |   |                        | 10  |                   | pF    |

| V <sub>OH</sub> | High Level Output Voltage<br>SDO, BUSY                                  | I <sub>0</sub> = -800µA                                                 | • | V <sub>CC</sub> - 0.5V |     |                   | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SDO, BUSY                                   | I <sub>0</sub> = 1.6mA                                                  | • |                        |     | 0.4 <del>V-</del> | V     |

| V <sub>OH</sub> | High Level Output Voltage<br>SCK                                        | I <sub>O</sub> = -800μA (Note 9)                                        | • | V <sub>CC</sub> - 0.5V |     |                   | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SCK                                         | I <sub>O</sub> = 1.6mA (Note 9)                                         | • |                        |     | 0.4 <del>V</del>  | ٧     |

| I <sub>OZ</sub> | Hi-Z Output Leakage<br>SDO                                              |                                                                         | • | -10                    |     | 10                | μA    |

## **POWER REQUIREMENTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 3)

| SYMBOL          | PARAMETER                                       | CONDITIONS                                        |   | MIN | TYP | MAX      | UNITS    |

|-----------------|-------------------------------------------------|---------------------------------------------------|---|-----|-----|----------|----------|

| V <sub>CC</sub> | Supply Voltage                                  |                                                   | • | 4.5 |     | 5.5      | V        |

| Icc             | Supply Current<br>Conversion Mode<br>Sleep Mode | CS = 0V (Note 7)<br>CS = V <sub>CC</sub> (Note 7) | • |     | 8   | 11<br>30 | mA<br>μA |

# TIMING CHARACTERISTICS The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL            | PARAMETER                           | CONDITIONS                                                        |   | MIN         | TYP                          | MAX                  | UNITS     |

|-------------------|-------------------------------------|-------------------------------------------------------------------|---|-------------|------------------------------|----------------------|-----------|

| f <sub>EOSC</sub> | External Oscillator Frequency Range |                                                                   | • | 0.1         |                              | 12 <del>- 20 -</del> | MHz       |

| t <sub>HEO</sub>  | External Oscillator High Period     |                                                                   | • | 25          |                              | 10000                | ns        |

| t <sub>LEO</sub>  | External Oscillator Low Period      |                                                                   | • | 25          |                              | 10000                | ns        |

| tconv             | Conversion Time                     | OSR = 256<br>OSR = 32768                                          | : | 0.99<br>126 | 1.13<br>145                  | 1.33<br>170          | ms<br>ms  |

|                   |                                     | External Oscillator (Notes 10, 13)  1x Mode                       | • |             | 40 • OSR ₹<br>feosc (kH      |                      | ms        |

| fisck             | Internal SCK Frequency              | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10) | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10 | 1                    | MHz<br>Hz |

/TINEAD

#### TIMING CHARACTERISTICS The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 3)

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                             |   | MIN  | TYP                           | MAX  | UNITS    |

|------------------------|--------------------------------------|------------------------------------------------------------------------|---|------|-------------------------------|------|----------|

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle              | (Note 9)                                                               | • | 45   |                               | 55   | %        |

| fesck                  | External SCK Frequency Range         | (Note 8)                                                               | • |      |                               | 20   | MHz      |

| t <sub>LESCK</sub>     | External SCK Low Period              | (Note 8)                                                               | • | 25   |                               |      | ns       |

| THESCK                 | External SCK High Period             | (Note 8)                                                               | • | 25   |                               |      | ns       |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | : | 41.6 | 35.3<br>320/f <sub>EOSC</sub> | 30.9 | ļiS<br>S |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time | (Note 8)                                                               | • |      | 32/f <sub>ESCK</sub>          |      | s        |

| t <sub>1</sub>         | CS ↓ to SD0 Low Z                    | (Note 12)                                                              | • | 0    |                               | 25   | ns       |

| 12                     | CS ↑ to SDO High Z                   | (Note 12)                                                              | • | 0    |                               | 25   | ns       |

| t <sub>3</sub>         | CS ↓ to SCK ↓                        | (Note 9)                                                               |   |      | 5                             |      | μS       |

| t <sub>4</sub>         | CS ↓ to SCK ↑                        | (Notes 8, 12)                                                          | • | 25   |                               |      | ns       |

| † <sub>KQMAX</sub>     | SCK ↓ to SD0 Valid                   |                                                                        | • |      |                               | 25   | ns       |

| tkamin                 | SD0 Hold After SCK ↓                 | (Note 5)                                                               | • | 15   |                               |      | ns       |

| t <sub>5</sub>         | SCK Setup Before CS ↓                |                                                                        | • | 50   |                               |      | ns       |

| t <sub>6</sub>         | SCK Hold After CS ↓                  |                                                                        | • |      |                               | 50   | ns       |

| t <sub>7</sub>         | SDI Setup Before SCK ↑               | (Note 5)                                                               | • | 10   |                               |      | ns       |

| tg                     | SDI Hold After SCK ↑                 | (Note 5)                                                               | • | 10   |                               |      | ns       |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to GND.

Note 3: V<sub>CC</sub> = 4.5V to 5.5V unless otherwise specified. V<sub>REF</sub> = REF\* - REF\*, V<sub>REFCM</sub> = (REF\* + REF\*)/2; REF\* is the positive reference input, REF is the negative reference input; VIN = IN+ - IN-,  $V_{INCM} = (IN^{+} + IN^{-})/2.$

Note 4: Fo pin tied to GND or to external conversion clock source with f<sub>EOSC</sub> = 10MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7: The converter uses the internal oscillator.

Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>ESCK</sub> and is expressed in Hz.

Note 9: The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of  $C_{LOAD} = 20 pF$ .

Note 10: The external oscillator is connected to the F<sub>O</sub> pin. The external oscillator frequency, f<sub>EOSC</sub>, is expressed in Hz.

Note 11: The converter uses the internal oscillator.  $F_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional-1::5 5 to 15 f<sub>0</sub> cycle to the conversion time.

### PIN FUNCTIONS

GND (Pins 1, 4, 5, 6, 31, 32, 33): Ground. Multiple ground pins internally connected for optimum ground current flow and V<sub>CC</sub> decoupling. Connect each one of these pins to a common ground plane through a low impedance connection. All seven pins must be connected to ground for proper operation.

BUSY (Pin 2): Conversion in Progress Indicator. This pin is HIGH while the conversion is in progress and goes LOW indicating the conversion is complete and data is ready. It remains LOW during the sleep and data output states. At the conclusion of the data output state, it goes HIGH indicating a new conversion has begun.

EXT (Pin 3): Internal/External SCK Selection Pin. This pin is used to select internal or external SCK for outputting/ inputting data. If EXT is tied low, the device is in the external SCK mode and data is shifted out of the device under the control of a user applied serial clock. If EXT is tied high, the internal serial clock mode is selected. The device generates its own SCK signal and outputs this on the SCK pin. A framing signal BUSY (Pin 2) goes low indicating data is being output.

COM (Pin 7): The common negative input (IN-) for all single ended multiplexer configurations. The voltage on CHO-CH7 and COM pins can have any value between GND

offset and full-scale performance remain unchanged as does the first multiple of f<sub>S</sub>.

The sample rate  $f_S$  and NULL  $f_N$ , may also be adjusted by driving the  $F_O$  pin with an external oscillator. The sample rate is  $f_S = f_{EOSC}/5$ , where  $f_{EOSC}$  is the frequency of the clock applied to  $F_O$ . Combining a large OSR with a reduced sample rate leads to notch frequencies  $f_N$  near DC while maintaining simple antialiasing requirements. A 100kHz clock applied to  $F_O$  results in a NULL at 0.6Hz plus all harmonics up to 20kHz, see Figure 13. This is useful in applications requiring digitalization of the DC component of a noisy input signal and eliminates the need of placing a 0.6Hz filter in front of the ADC.

Figure 13. LTC2446/LTC2447 Normal Mode Rejection (External Oscillator at 90kHz)

An external oscillator operating from 100kHz to 20MHz can be implemented using the LTC1799 (resistor set SOT-23 oscillator), see Figure 14. By floating pin 4 (DIV) of the LTC1799, the output oscillator frequency is:

$$f_{OSC} = 10MHz \cdot \left(\frac{10k}{10 \cdot R_{SET}}\right)$$

The normal mode rejection characteristic shown in Figure 13 is achieved by applying the output of the LTC1799 (with  $R_{SET} = 100$ k) to the  $F_0$  pin on the LTC2446/LTC2447 with SDI tied HIGH (OSR = 32768).

#### Multiple Ratiometric and Absolute Measurements

The LTC2446/LTC2447 combine a high precision, high speed delta-sigma converter with a versatile front-end

Figure 14. Simple External Clock Source

multiplexer. The unique no latency architecture allows seamless changes in both input channel and reference while the absolute accuracy ensures excellent matching between both analog input channels and reference channels. Any set of inputs (differential or single-ended) can perform a conversion with one of two references. For Bridges, RTDs and other ratiometric devices, each set of channels can perform a conversion with respect to a unique reference voltage. For Thermocouples, voltage sense, current sense and other absolute sensors, each set of channels can perform a conversion with respect to a single global reference voltage (see Figure 15). This allows users to measure both multiple absolute and multiple ratio metric sensors with the same device in such applications as flow, gas chromatography, multiple RTDs or bridges, or universal data acquisition.

#### Average Input Current

The LTC2446 switches the input and reference to a 2pF capacitor at a frequency of 1.8MHz. A simplified equivalent circuit is shown in Figure 16. The sample capacitor for the LTC2447 is 4pF, and its average input current is externally buffered from the input source.

The average input and reference currents can be expressed in terms of the equivalent input resistance of the sample capacitor, where: Req = 1/(f<sub>SW</sub> • Ceq).

24467fa