# CoolRunner-II CPLD Solutions for Cell Phone Handsets and Terminals

A Designer's Guide

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2005 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# **Table of Contents**

| Preface: About This Handbook                            |

|---------------------------------------------------------|

| Guide Contents                                          |

| Additional Resources 10                                 |

| Chapter 1: Introduction to Handset Design               |

| CPLDs in Cell Phone Handsets and Terminals              |

| Quick Look at a Handset 14                              |

| Functional Components of a Digital Handset and Terminal |

| Cell Phone Chipsets                                     |

| GPS Added into a Phone 17                               |

| MediPhone—A Speculative Example 18                      |

| Power and Packaging are Key! 19                         |

| Looking Forward to 4G 20                                |

# Implementing Keypad Scanners

| Introduction                    | 23 |

|---------------------------------|----|

| Expanding I/O                   | 24 |

| Scanning and Encoding           | 24 |

| CPLD Design Details             | 25 |

| Implementation and Verification | 26 |

#### **Level Translation**

| Introduction                                            | 27 |

|---------------------------------------------------------|----|

| Configuring I/O to Use I/O Standards                    | 28 |

| Using the CPLD as a Level Shifter                       | 28 |

| Incorporating the Level Shifter into a Common Interface | 28 |

| CPLDs Can be Used to Supply Current                     | 29 |

| Powering VCCIO Between Specifications                   |    |

#### **Character LCD Module Interface**

| Introduction                      | 31 |

|-----------------------------------|----|

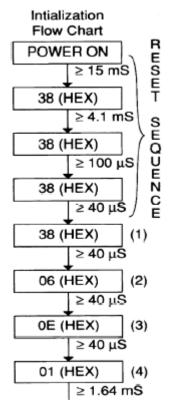

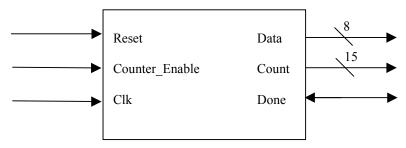

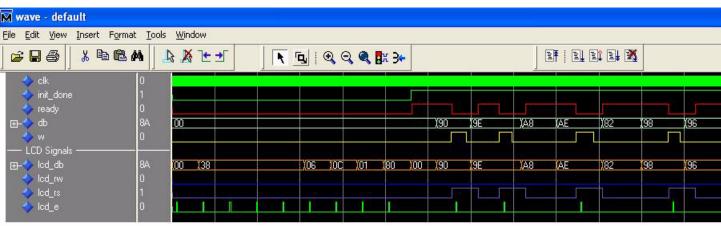

| CPLD Implementation               | 32 |

| LCD Controller Main State Machine | 35 |

| Resource Summary                  | 35 |

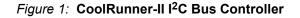

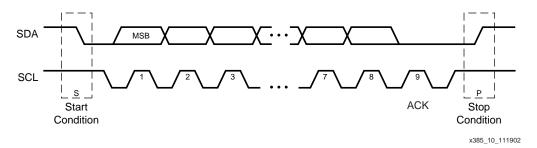

### I<sup>2</sup>C Bus Controller

| Introduction                | 37 |

|-----------------------------|----|

| I <sup>2</sup> C Background | 37 |

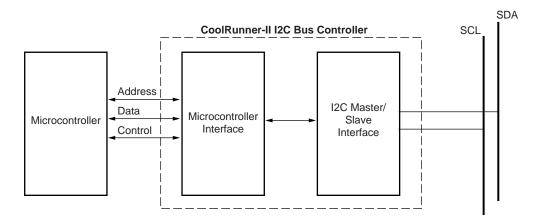

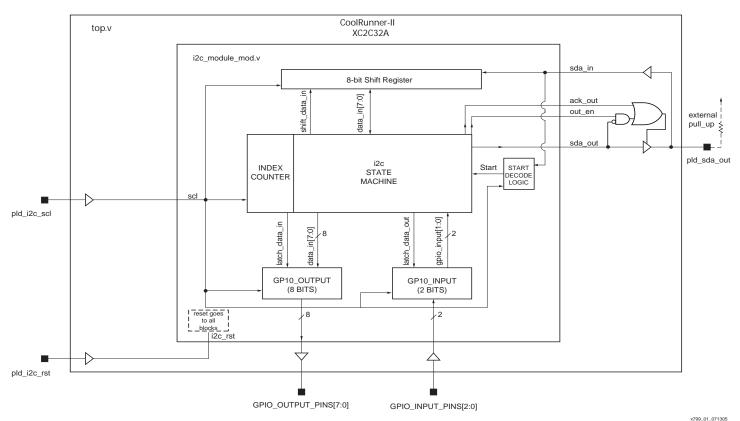

| CoolRunner-II I <sup>2</sup> C Controller 3           | 9 |

|-------------------------------------------------------|---|

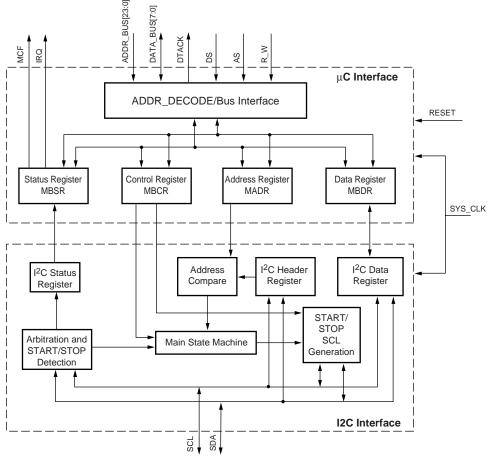

| Microcontroller Logic 4                               | 1 |

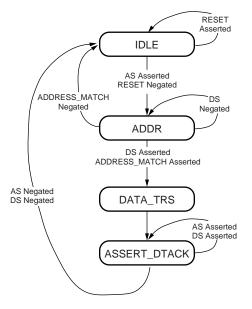

| Microcontroller Bus Interface State Machine 4         | 1 |

| CoolRunner-II I <sup>2</sup> C Controller Registers 4 | 2 |

| I <sup>2</sup> C Interface Logic                      | 5 |

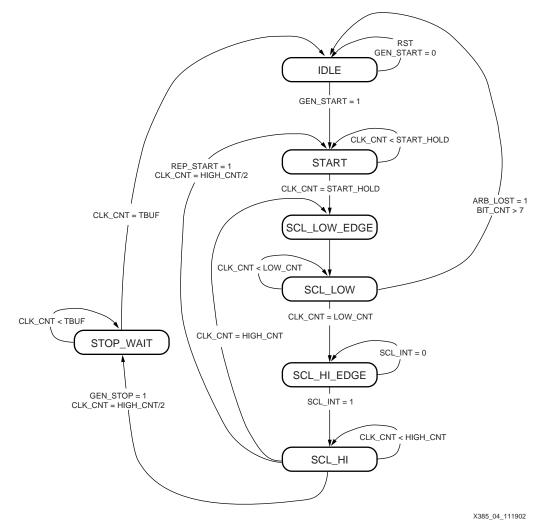

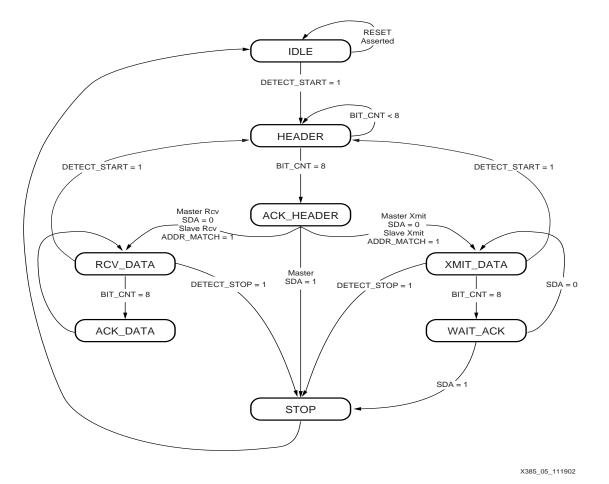

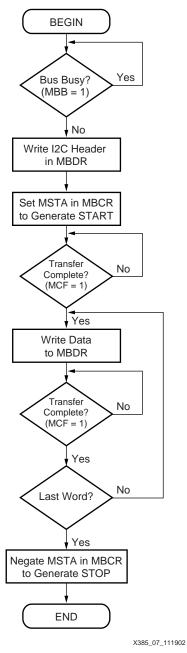

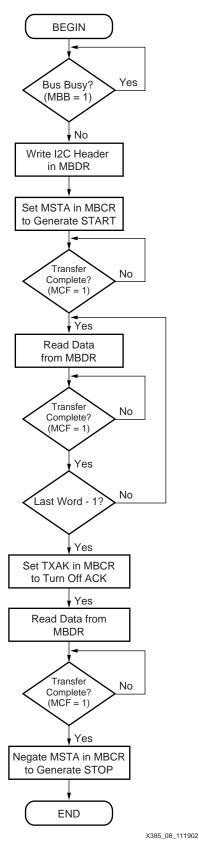

| Operational Flow Diagrams 5                           | 1 |

| CoolRunner-II CPLD Implementation 5                   | 4 |

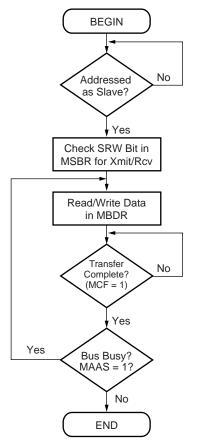

# Interfacing to Mobile SDRAM

| Introduction        | 7 |

|---------------------|---|

| Signal Definitions  | 7 |

| CPLD Design         | 8 |

| SDRAM State Machine | 0 |

| System Interface    | 1 |

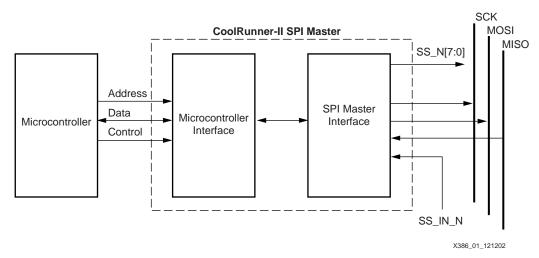

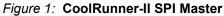

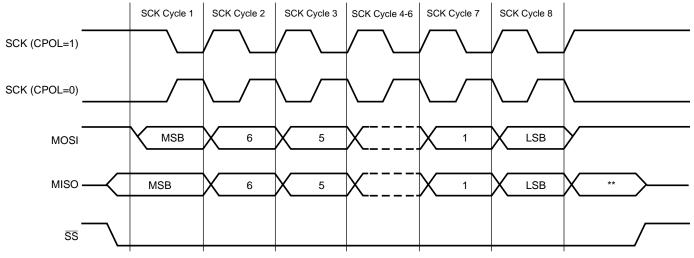

## Serial Peripheral Interface (SPI) Master

| Introduction                            | 63 |

|-----------------------------------------|----|

| SPI Background                          | 63 |

| CoolRunner-II SPI Master Implementation | 66 |

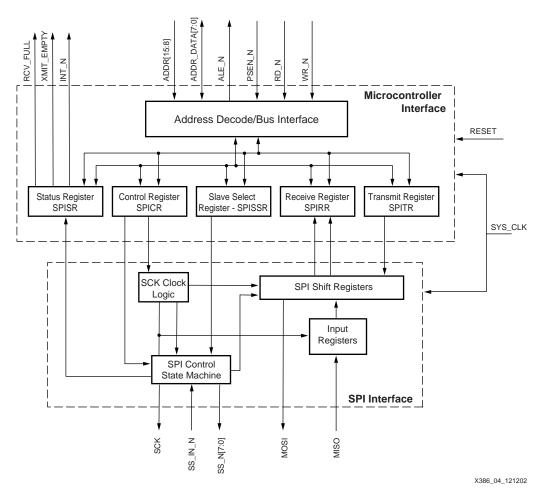

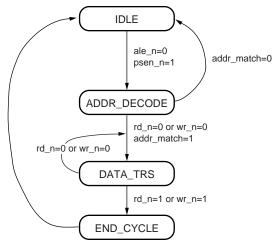

| μC Interface Logic                      | 69 |

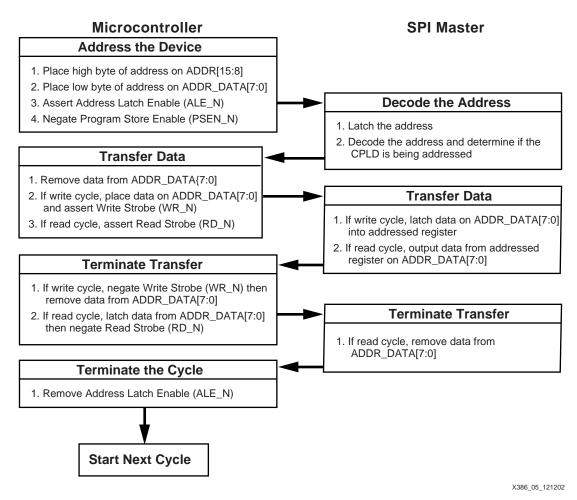

| μC Read/Write Protocol                  | 69 |

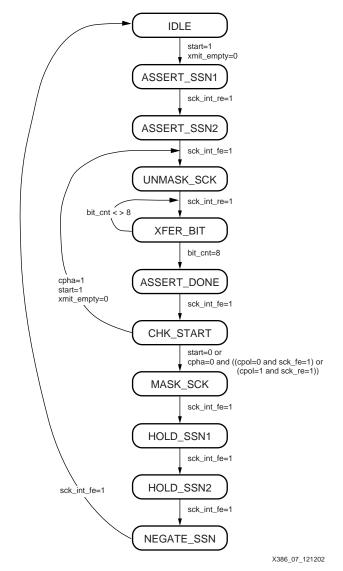

| SPI Interface Logic                     | 74 |

| Operational Flow Diagrams               | 79 |

| CoolRunner-II CPLD Implementation       | 81 |

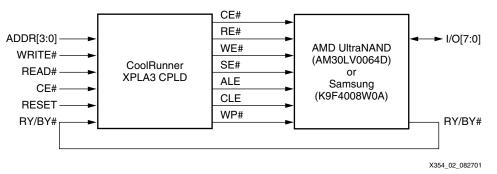

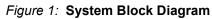

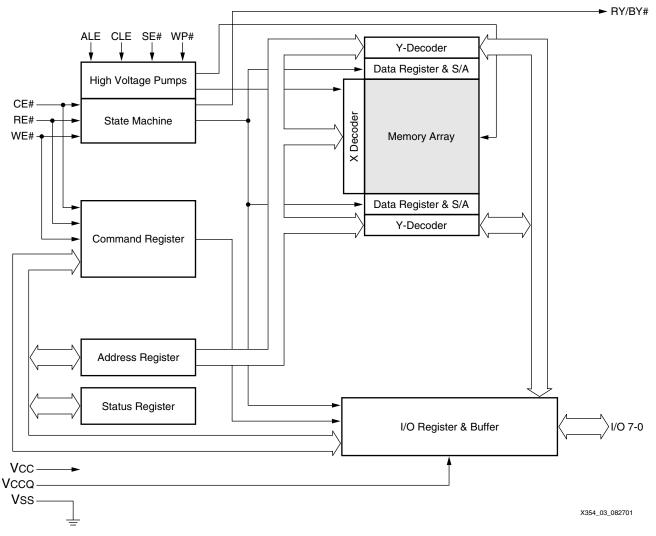

# Interfacing to a NAND Flash Memory Device

| Introduction            | . 83 |

|-------------------------|------|

| NAND Interface          | . 83 |

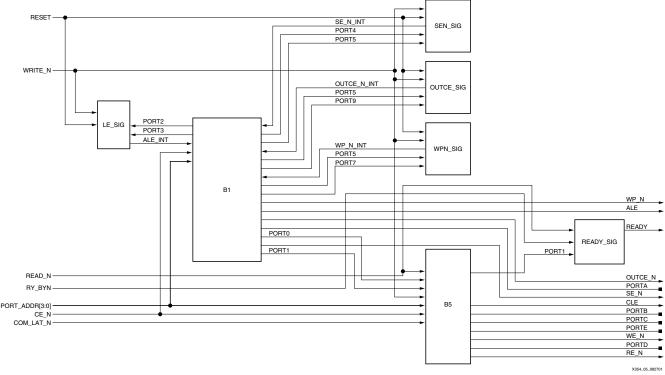

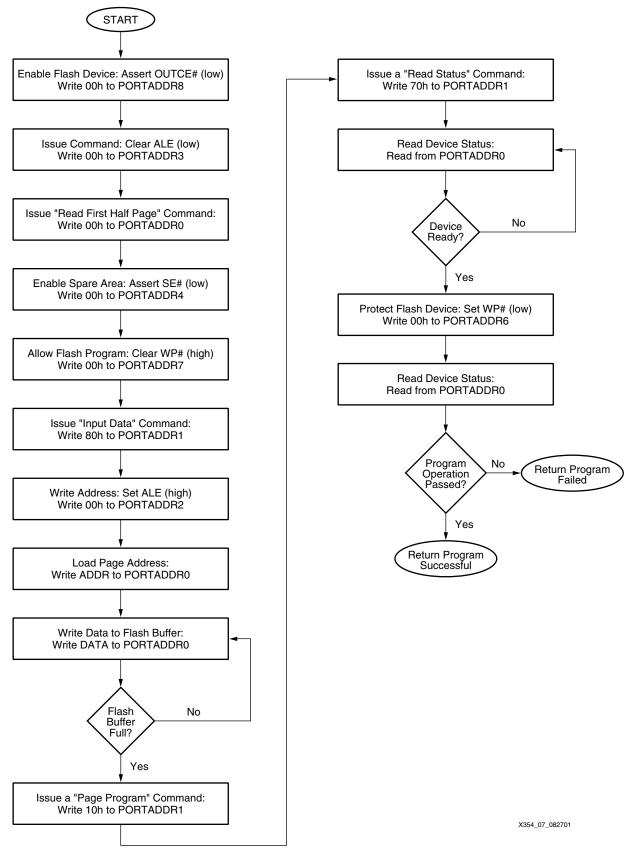

| CPLD Implementation     | . 90 |

| Design Verification     | . 90 |

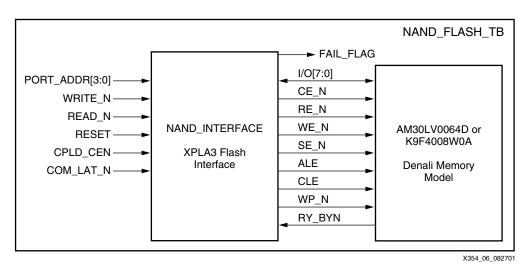

| Test Bench Diagram      | . 90 |

| ModelSim Implementation | . 93 |

# CompactFlash Card Interface

| Introduction           |

|------------------------|

| Electrical Interface   |

| I/O Considerations 100 |

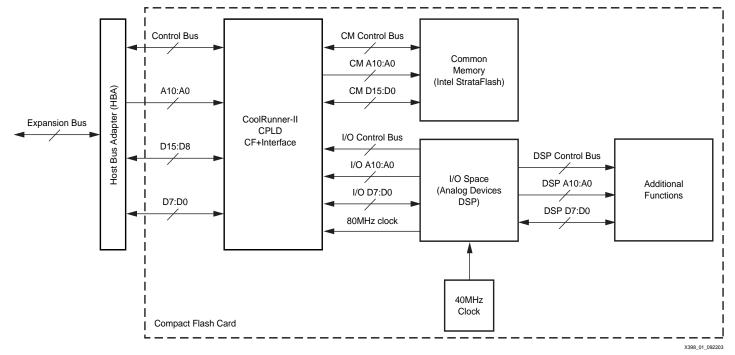

| Block Diagram          |

| Signal Descriptions    |

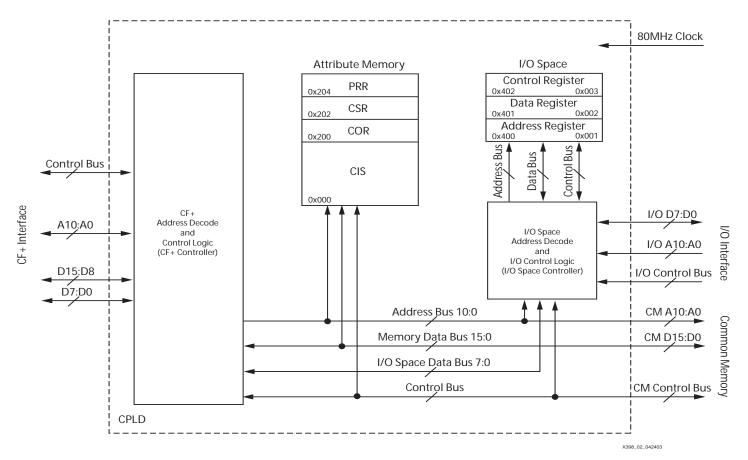

| CF+ Controller         |

| Attribute Memory 110   |

| Common Memory 113      |

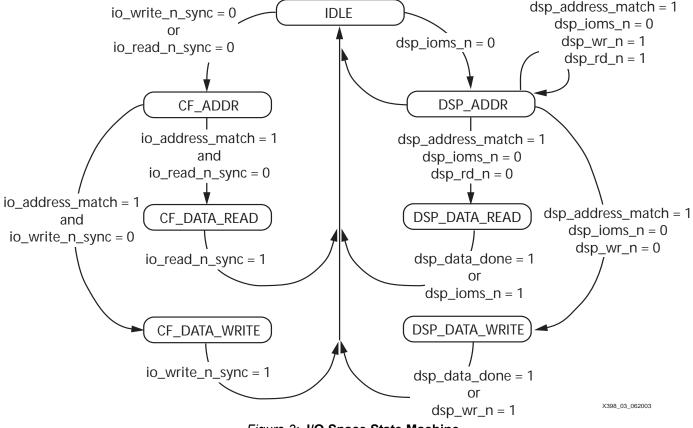

| I/O Space              |

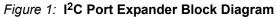

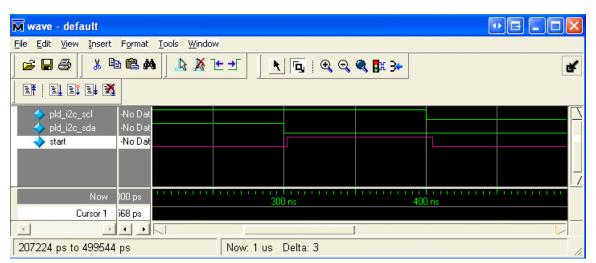

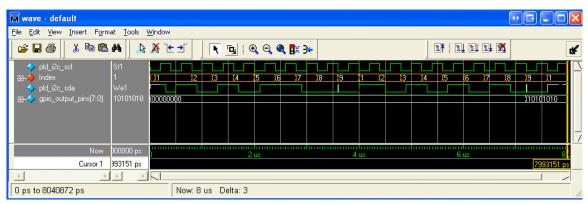

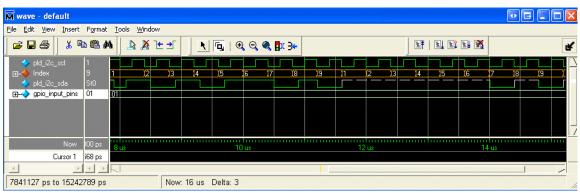

# An SMBus/I<sup>2</sup>C-Compatible Port Expander

| Summary                                                             | 119 |

|---------------------------------------------------------------------|-----|

| CoolRunner-II Advantages                                            | 119 |

| Using the CoolRunner-II SMBus/I <sup>2</sup> C Port Expander Design | 119 |

| Customizing the Design                                              | 123 |

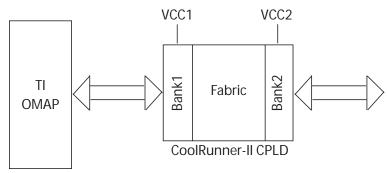

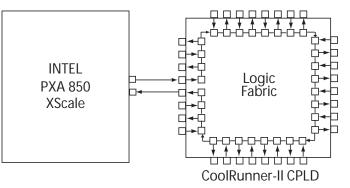

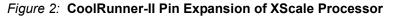

## **OMAP, XScale & Other Chip Sets**

| Introduction        | 125 |

|---------------------|-----|

| Level Translation   | 125 |

| Pin Expansion       | 126 |

| Pin Swizzling       | 126 |

| Power Control       | 126 |

| Power Reduction     | 126 |

| Logic Consolidation | 127 |

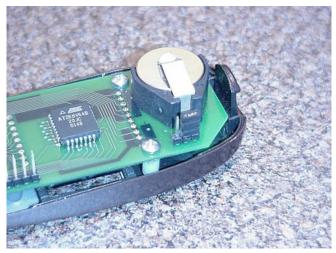

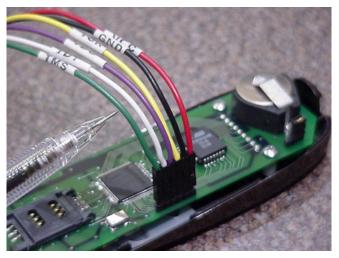

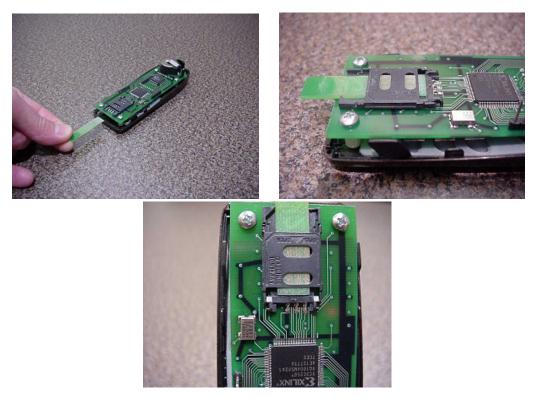

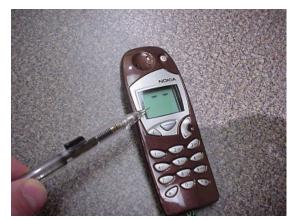

# **Cell Phone Demo Board**

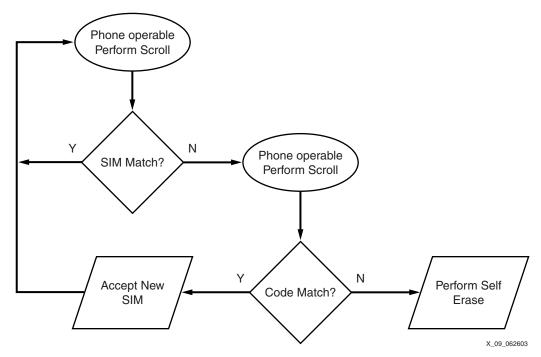

| Introduction           | 129 |

|------------------------|-----|

| Demonstration Overview | 129 |

| Setup                  | 130 |

| Operation              | 133 |

| Design Information     | 134 |

#### Chapter 2: Low Power Design

## Low Power Design

| Introduction 1            | 39 |

|---------------------------|----|

| Power Saving Features 1   | 39 |

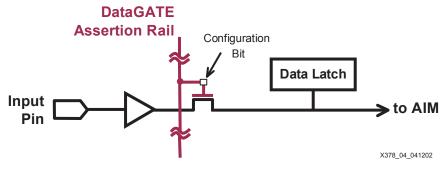

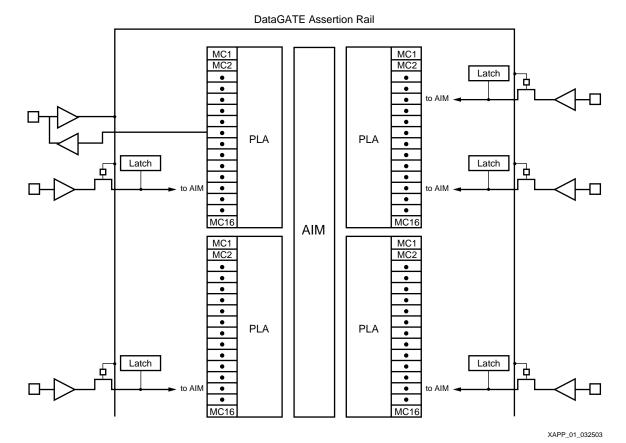

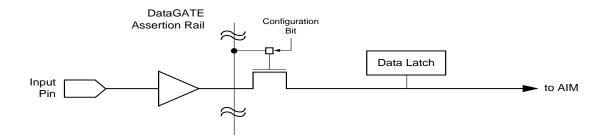

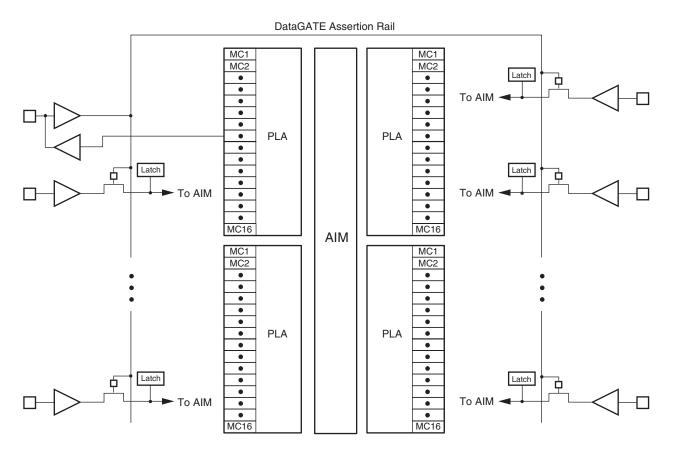

| DataGATE 1                | 40 |

| Schmitt Trigger 1         | 40 |

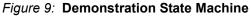

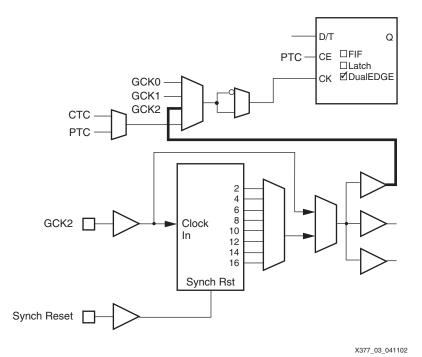

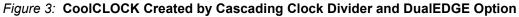

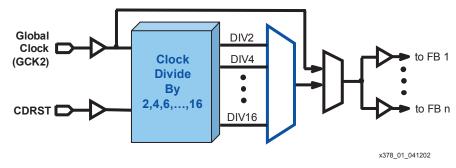

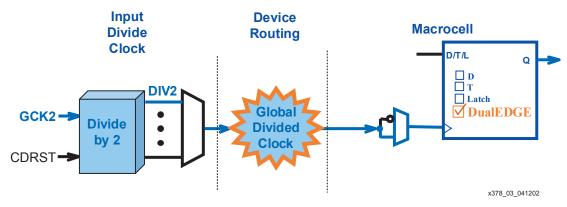

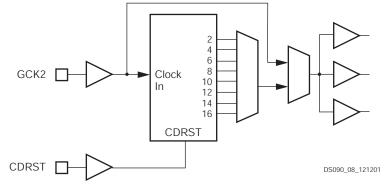

| Clock Divider 1           | 41 |

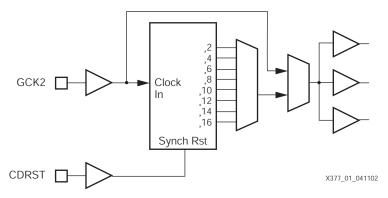

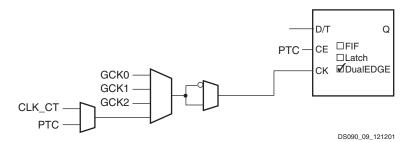

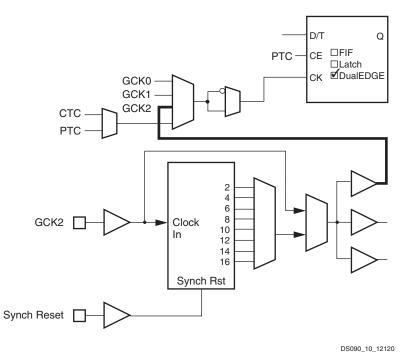

| DualEDGE Registers 1      | 41 |

| CoolCLOCK 1               | 42 |

| Power Saving Techniques 1 | 44 |

## **Advanced Features**

| DualEDGE Registers | 149 |

|--------------------|-----|

| Clock Divider      | 150 |

| CoolCLOCK          | 153 |

| DataGATE           | 154 |

| Schmitt Trigger    | 155 |

| I/O Termination    | 145 |

| I/O Configuration  | 146 |

| Open Drain         | 148 |

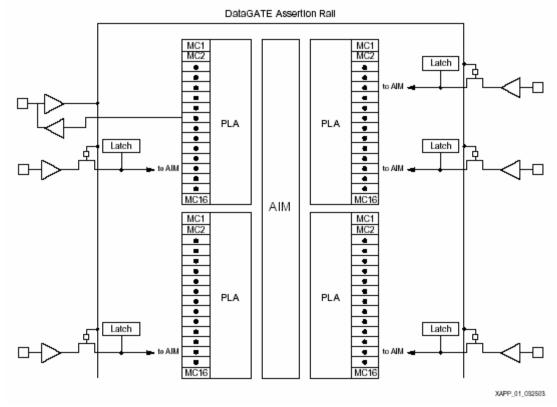

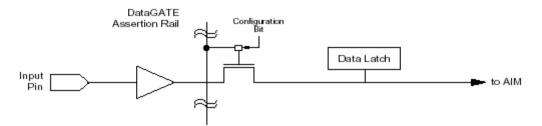

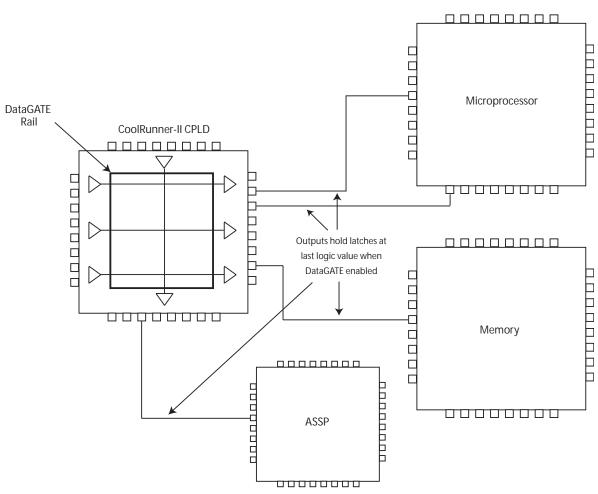

# Using DataGATE

| Introduction                               | 61 |

|--------------------------------------------|----|

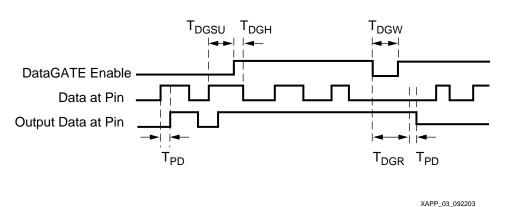

| DataGATE Assertion Rail 10                 | 62 |

| DataGATE Timing Parameters 10              | 62 |

| Applications                               | 63 |

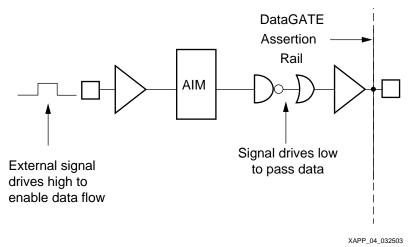

| Simple External DataGATE Control Signal 10 | 63 |

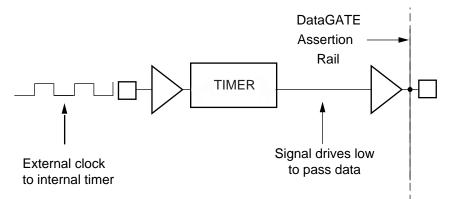

| Timer                                      |    |

| Controller                                 | 64 |

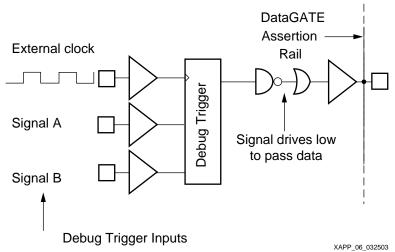

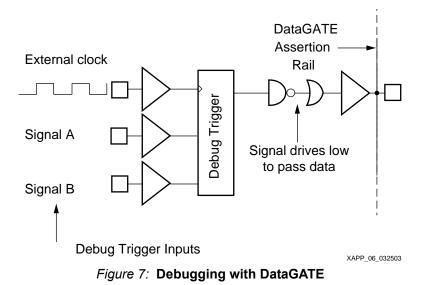

| Debugging with DataGATE 10                 | 65 |

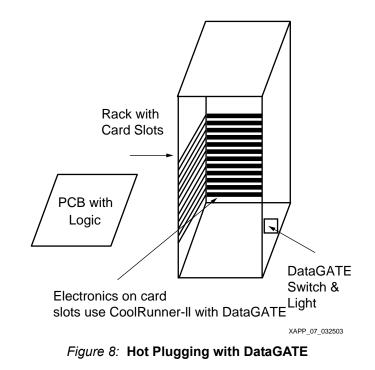

| Hot Plugging with DataGATE 10              | 65 |

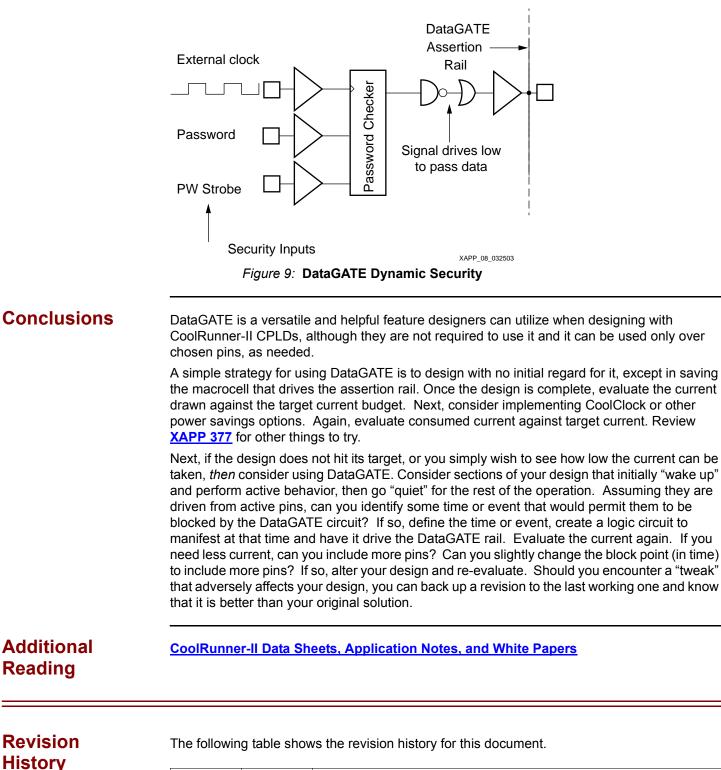

| Security                                   | 66 |

## The Real Value of DataGATE

| Introduction                       | 169 |

|------------------------------------|-----|

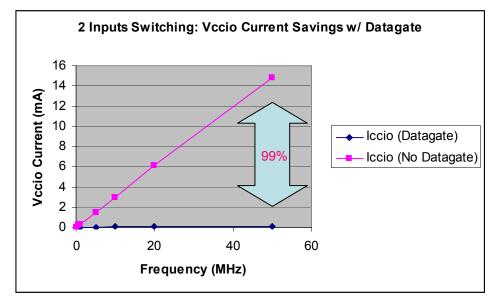

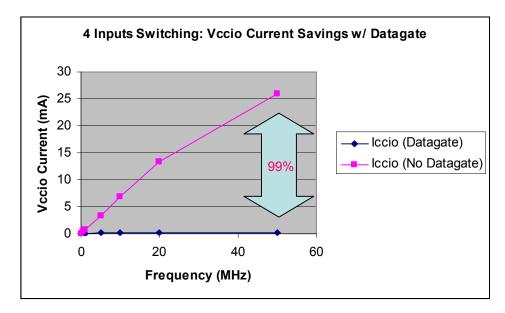

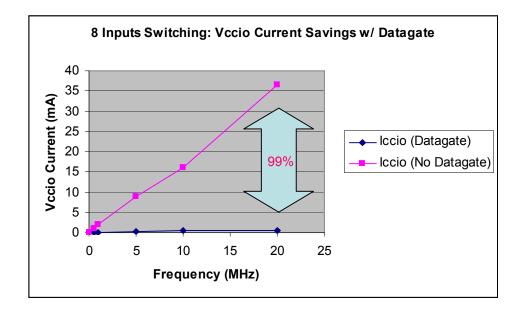

| How Good is DataGATE?              | 170 |

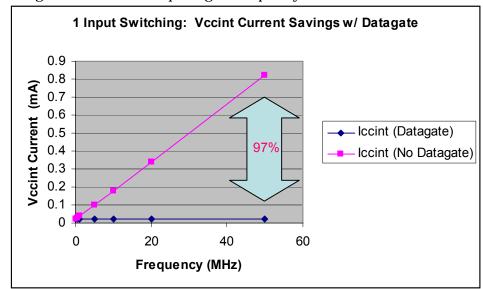

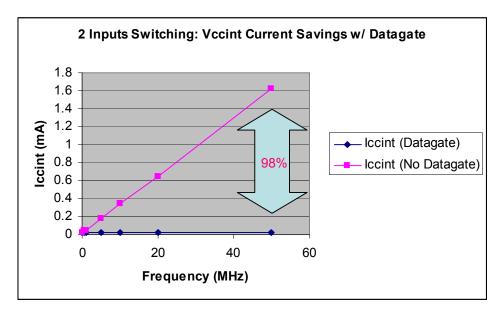

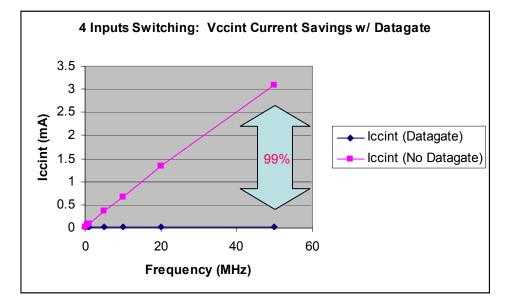

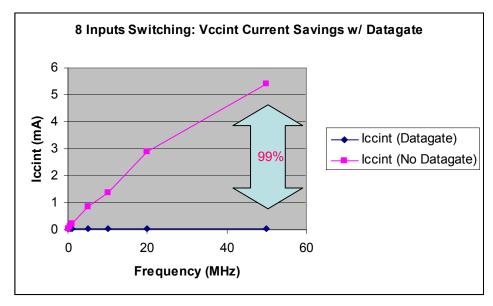

| V <sub>CCINT</sub> Current Savings | 170 |

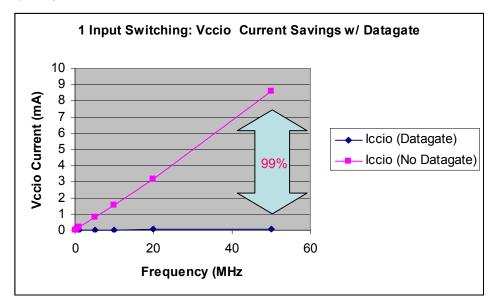

| What about VCCIO Current?          | 172 |

## **Managing Power**

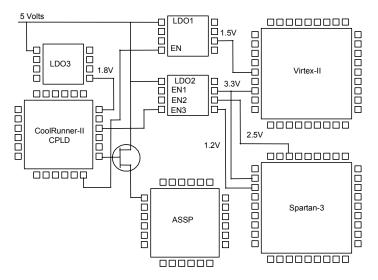

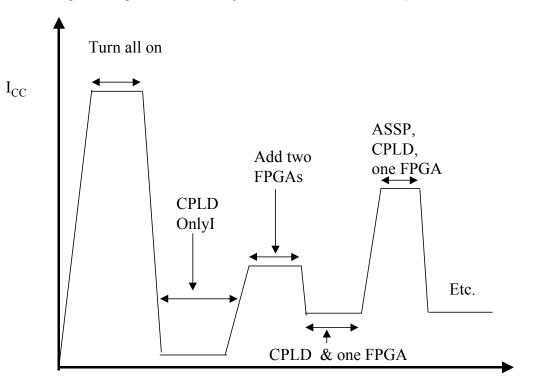

| Introduction                                                      | 177   |

|-------------------------------------------------------------------|-------|

| The Power Equation                                                | 177   |

| The CoolRunner-II Solution.                                       | . 178 |

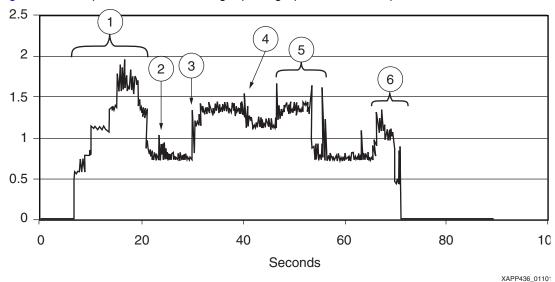

| Power Profile of LG Cell Phone Taking Still Photograph            | . 178 |

| Multiple Chips "Power Managed" by a CoolRunner-II CPLD            | 179   |

| Current Profile of a System with Various Active Devices Over Time | . 181 |

| DataGATE                                                          | 182   |

|                                                                   |       |

## Appendix A: CoolRunner-II Data Sheets

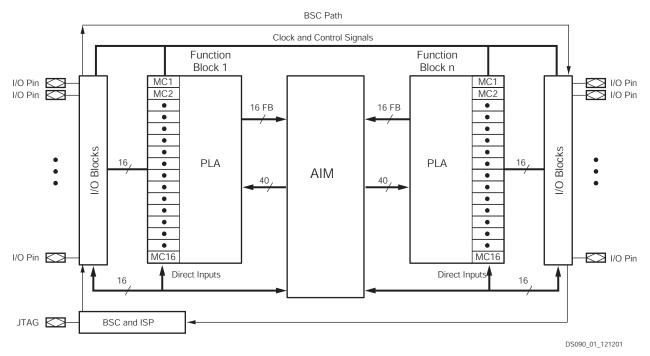

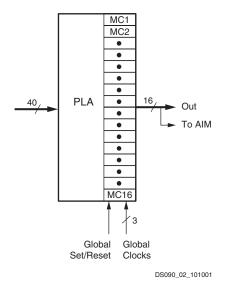

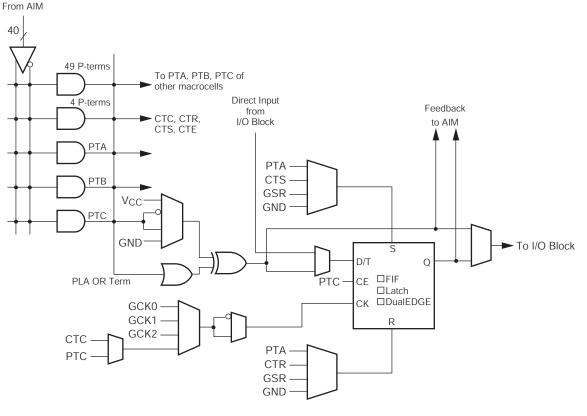

# CoolRunner-II CPLD Family

| Features                                                            |

|---------------------------------------------------------------------|

| Family Overview                                                     |

| CoolRunner-II CPLD Family Parameters 189                            |

| CoolRunner-II CPLD Family Features    191                           |

| Architecture Description                                            |

| Advanced Interconnect Matrix (AIM) 193                              |

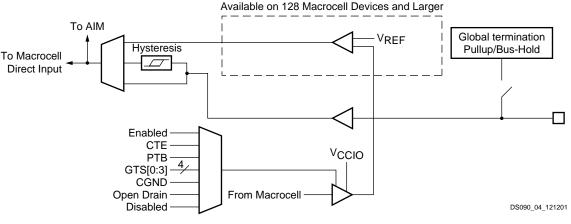

| I/O Block                                                           |

| Output Banking                                                      |

| DataGATE                                                            |

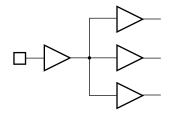

| Global Clocks (GCK), Sets/Resets (GSR) and Output Enables (GTS) 196 |

| Design Security                                                     |

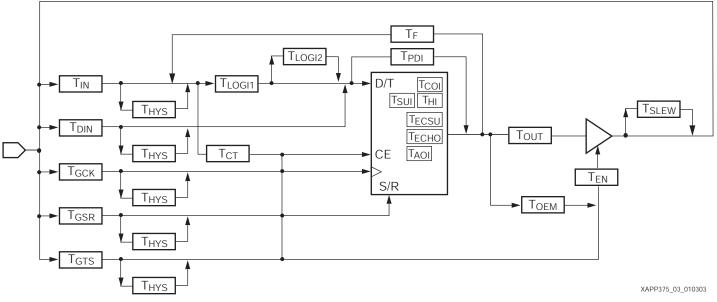

| CoolRunner-II CPLD Timing Model 198                                 |

| Programming                                                         |

| In System Programming 199                                           |

| On-The-Fly Reconfiguration (OTF) 199                                |

| JTAG Instructions                                 | 199 |

|---------------------------------------------------|-----|

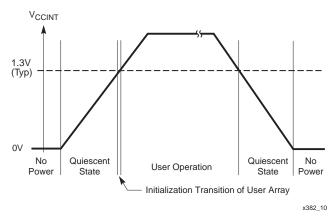

| Power-Up Characteristics                          | 199 |

| Device Behavior During Power Up                   | 199 |

| I/O Banking                                       | 200 |

| Mixed Voltage, Power Sequencing, and Hot Plugging | 200 |

| Development System Support                        | 200 |

| ATE Support                                       | 200 |

| Absolute Maximum Ratings                          | 201 |

| Quality and Reliability Parameters                | 201 |

## XC2C32A CoolRunner-II CPLD

| Features                             |

|--------------------------------------|

| Description                          |

| Supported I/O Standards 204          |

| I/O Standards for XC2C32A 204        |

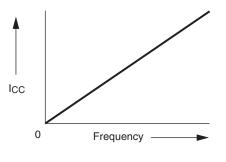

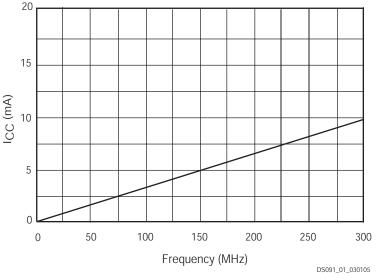

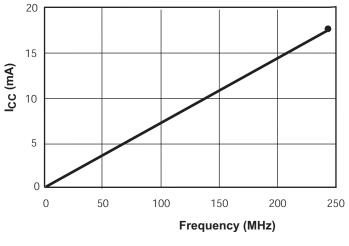

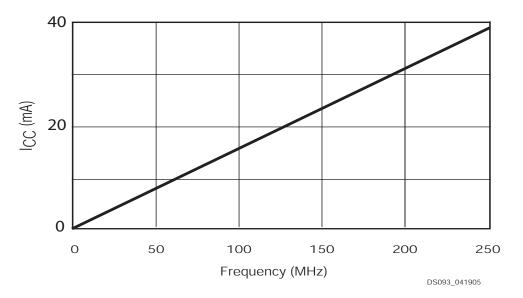

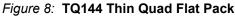

| I <sub>CC</sub> vs Frequency         |

| Recommended Operating Conditions 205 |

| Internal Timing Parameters 208       |

| Switching Characteristics 209        |

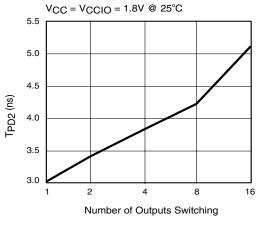

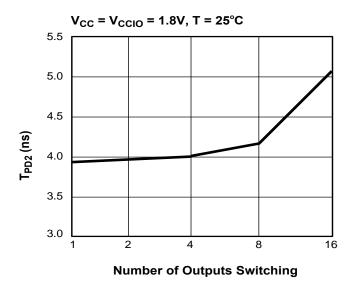

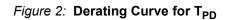

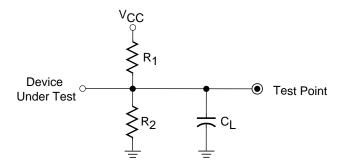

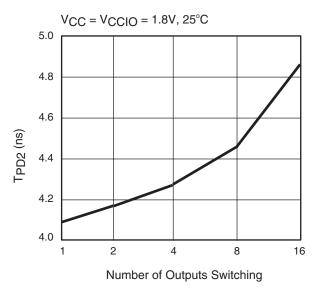

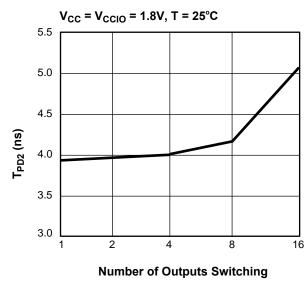

| Derating Curve for TPD 209           |

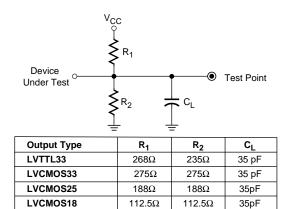

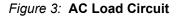

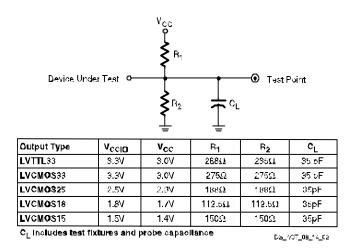

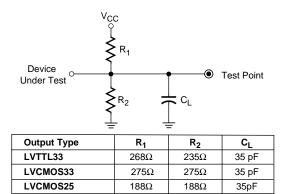

| AC Load Circuit                      |

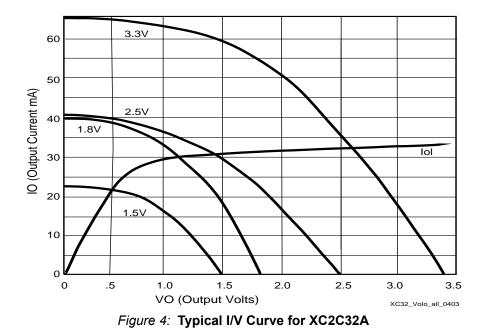

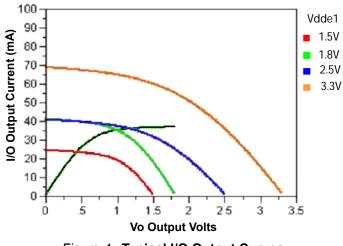

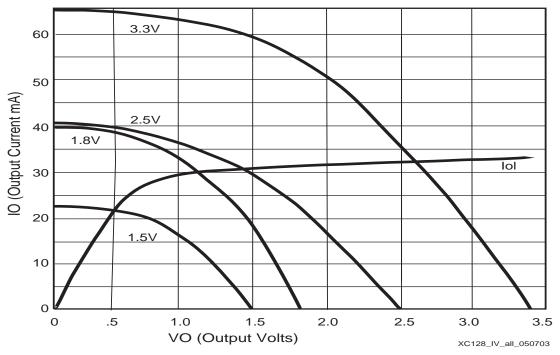

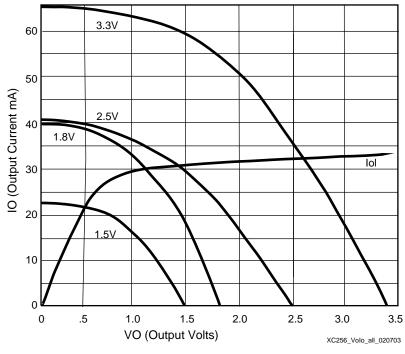

| Typical I/V Curve for XC2C32A 210    |

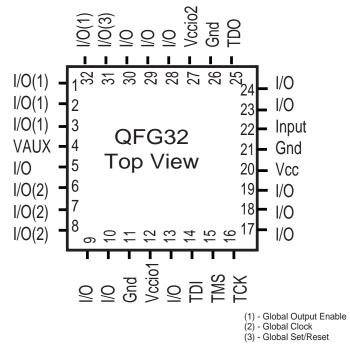

| Pin Descriptions                     |

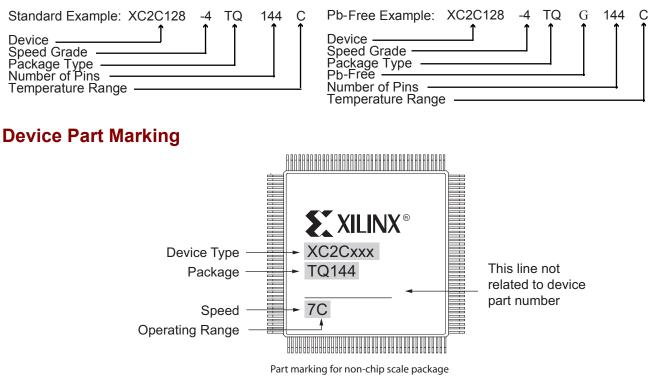

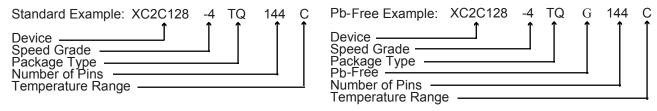

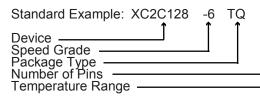

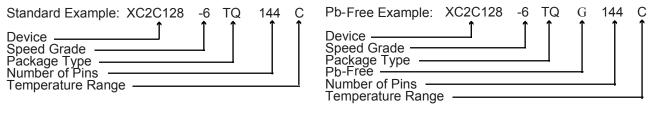

| Ordering Information 212             |

| Packages                             |

|                                      |

# XC2C64A CoolRunner-II CPLD

| Features                         | 217 |

|----------------------------------|-----|

| Description                      | 217 |

| Supported I/O Standards          | 218 |

| I/O Standards for XC2C64A        | 218 |

| $I_{CC}$ vs Frequency            | 218 |

| Recommended Operating Conditions | 219 |

| Internal Timing Parameters       | 223 |

| Switching Characteristics        | 225 |

| Derating Curve for TPD           | 225 |

| AC Test Circuit                  | 225 |

| AC Load Circuit                  | 225 |

| Typical I/O Output Curves        | 225 |

| Pin Descriptions                 | 226 |

| Ordering Information             | 228 |

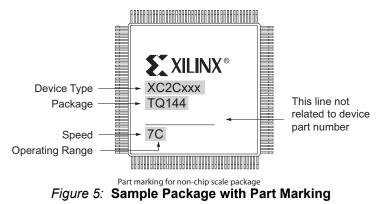

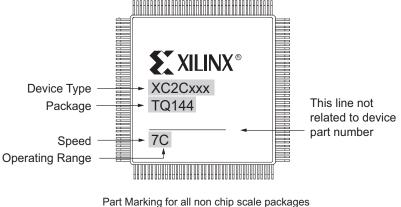

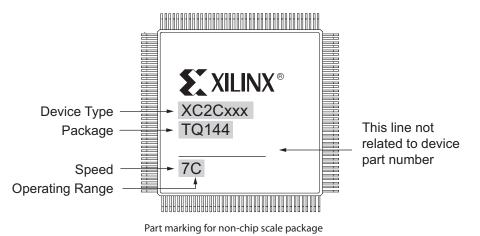

| Sample Package with Part Marking | 229 |

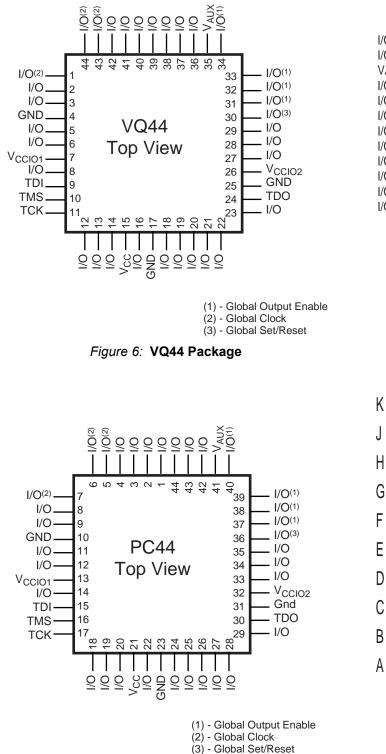

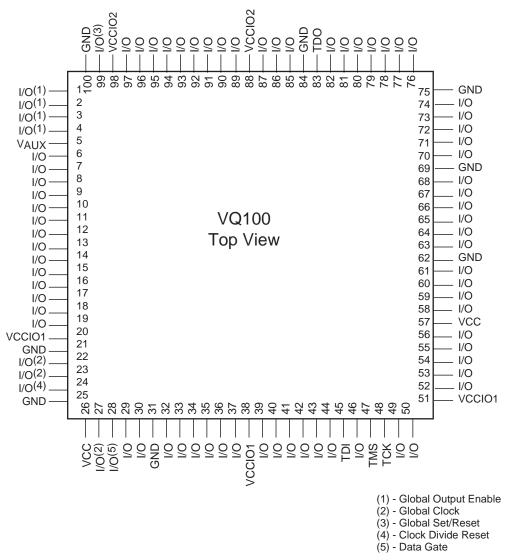

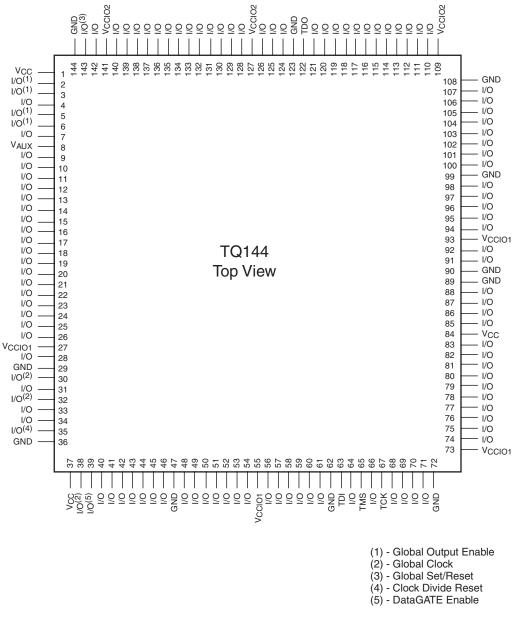

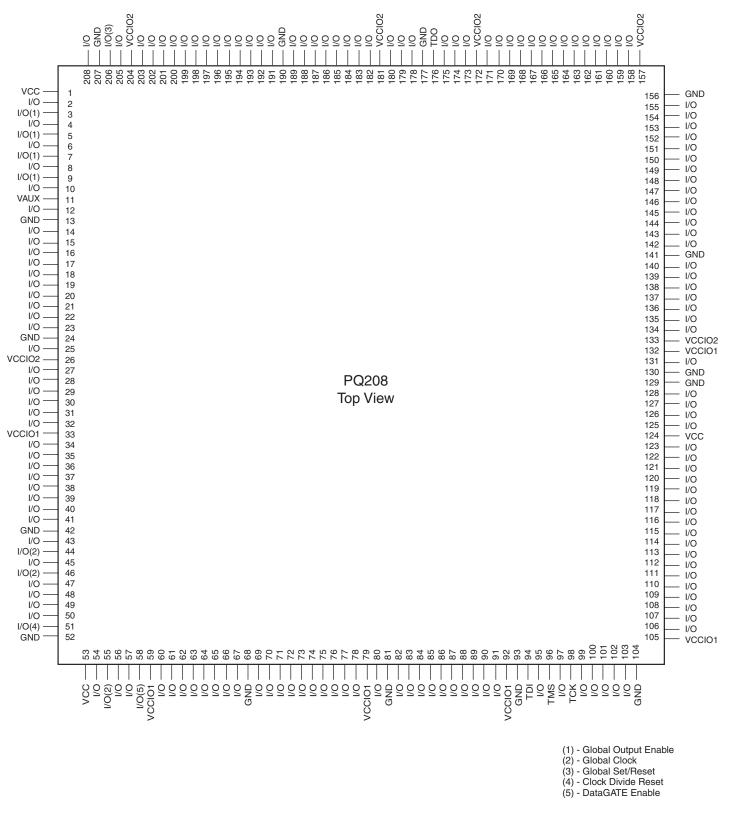

| Package Pinout Diagrams          | 230 |

#### XC2C128 CoolRunner-II CPLD

## XC2C256 CoolRunner-II CPLD

| Features                                                                |

|-------------------------------------------------------------------------|

| Description                                                             |

| Supported I/O Standards 250                                             |

| I <sub>CC</sub> vs Frequency                                            |

| Absolute Maximum Ratings 251                                            |

| Recommended Operating Conditions 251                                    |

| DC Electrical Characteristics 251                                       |

| AC Electrical Characteristics Over Recommended Operating Conditions 255 |

| Internal Timing Parameters 257                                          |

| Switching Characteristics 258                                           |

| Pin Descriptions                                                        |

| Ordering Information                                                    |

# Preface

# **About This Handbook**

We wrote this handbook to share many of the solutions Xilinx has created supporting handset and terminal customers over the last few years. To that end, we have included many of the basic functions that you will find in standard handsets, like keyboard and display interfaces; but, we also include solutions to extend beyond basic handset functionality. For instance, we include a compact flash interface that easily modifies to an IDE disk interface. As more applications like audio and video entertainment are being added into handsets, we also track the requirements for greater local storage.

This handbook consists of a collection of technical documents, including white papers, application notes and data sheets. Given the extremely fast pace of technology development, some content may become outdated over time. To find the latest technical product and application data from Xilinx, simply find the required content on the Xilinx website at www.xilinx.com/support/library.htm.

Two key messages are threaded throughout this handbook. First, Xilinx has become a high volume supplier of products into the portable consumer arena, with worldwide manufacturing, advanced product planning logistics and world class customer support – in local time zones with local languages. We ship tens of millions of CPLDs each quarter, all over the world.

Second, although handsets and terminals are well served by chipset solutions from Texas Instruments, Intel, Freescale, Qualcomm and others, these chipsets take time to develop and get "right". In that time, evolving applications arise making it impossible to deliver to the world wide customer base in real time. Some handset developers have time horizons of nine months to a year, whereas others develop within two to four months. Being able to respond to the latest application requirements can only be done with low power, inexpensive, high speed programmable logic.

Programmable logic gives you fastest time-to-market and flexible product life cycle management available in the silicon world. There is no other equivalent solution for reducing design time, and nothing that gives you this level of flexibility to respond to changing market requirements.

Incidentally, much of the information we provide was "discovered" by ASIC designers needing to fix their gate array solutions with small, low power CPLDs. This occurred so often that they extended the idea into their product development cycle, to account for late arriving, last minute market requirements. You might say: "there's always room for CoolRunner<sup>TM</sup>-II."

Please scan the table of contents to find the applications you need today, or work your way through the handbook following the capabilities of CoolRunner-II CPLDs, delivering low power, inexpensive solutions in tiny packages.

You will find full explanations of CoolRunner-II advanced features like clock dividing and DataGATE. Explanations will show how adding a CoolRunner-II to a design can actually

reduce the power being used on the whole board. The application notes are backed up with full designs you can download and use today. The designs are fully documented, allowing you to expand or collapse functionality as required.

We have included the CoolRunner-II Family data sheet and those of the four most popular parts for handsets and terminals – the XC2C32A, XC2C64A, XC2C128 and the XC2C256 CoolRunner-II CPLDs.

#### Acknowledgements

This book would not have been possible without the efforts and cooperation of several applications engineers, and one FAE. I would like to thank them for their contributions to the ideas, designs, and hard work performed in the creation of application notes and white papers for the handset marketplace. They are:

- Nick Mehta

- Anita Schreiber

- Mark Ng

- Scott Lien

- Frank Wirtz

- John Hubbard

- Jennifer Jenkins

- Mike Gulotta

I would also like to extend my appreciation to the CPLD Marketing team for guidance and the creation of collateral marketing material to support the efforts of the handset initiative. They are:

- Mark Halfman

- Denny Steele

- Tony Grant

- Betsy Thibault

- LaToya Parker

- Roger Seaman

- Sincerely, Jesse Jenkins Author

#### **Additional Resources**

To find the very latest data, see the Xilinx website at:

http://www.xilinx.com/literature/index.htm.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

# Chapter 1

# **Introduction to Handset Design**

This handbook provides information, white papers, data sheets, and application notes useful in the creation of low cost, low power electronic handsets, including cell phones, PDAs and other devices in which elegant design, cost, and battery life are paramount. You can improve your results in all three areas using Xilinx CoolRunner<sup>TM</sup>-II CPLDs and the information provided in this handbook.

The handbook contains topics for the implementation of common handset functions, such as keypad scanners, as well as topics for improvement of low power design. Using this document you can reduce the number of components in your design, expand the features, lower your overall power profile, and save money in both design cost and component inventory.

This Chapter contains white papers and application notes written to assist a handset designer in the creation of new products. The topics listed are among the design applications our CPLDs are fully capable of performing. In most cases, Xilinx provides free reference designs to help speed up your design process. The reference designs can be found at:

#### http://www.xilinx.com/products/silicon\_solutions/cplds/resources/coolvhdlq.htm

This Chapter contains the following topics:

- CPLDs in Cell Phone Handsets/Terminals

- Implementing Keypad Scanners

- Level Translation

- Character LCD Module Interface

- I<sup>2</sup>C Bus Controller

- Interfacing to Mobile SDRAM

- Serial Peripheral Interface (SPI) Master

- Interfacing to a NAND Flash Memory Device

- CompactFlash Card Interface

- An SMBus/I<sup>2</sup>C-Compatible Port Expander

- OMAP, XScale & Other Chip Sets

- Cell Phone Demo Board

# CoolRunner-II CPLDs in Cell Phone Handsets/Terminals

Cell phone handsets (or "terminals," as they're called in Europe) are among the most dynamic products in the electronics market today. From their original analog roots, they have evolved into nearly pure digital devices with as much functionality as complex PDAs. Consumers who once evaluated handsets based on their ability to make high-quality local calls now take call clarity as a given. Their choices instead rest on characteristics ranging from a handset's "skin" color to its ability to support streaming video. Buyers, even those shopping for low-cost handsets, increasingly demand these kinds of features: "extras" are well on their way to becoming standards. This shift puts manufacturers in a bind as they try to balance low cost with the ever-increasing consumer insistence on new features. Should customers pay for these features outright, or should their monthly payments subsidize the handset cost?

Each country has adopted an individual economic model to resolve this question. Common to all of these models, however, is a need to financially cope with increasing numbers of new features. Our goal in this white paper is to show how using CoolRunner<sup>™</sup>-II CPLDs in handsets will make it easier for handset developers to make these future changes—as well as baseline handset capability financially viable.

<sup>© 2005</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

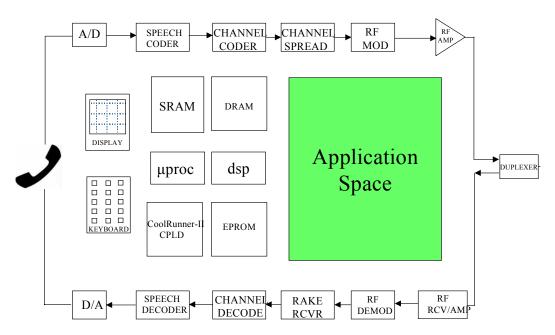

Quick Look at aFigure 1 shows a fairly straightforward block diagram of a digital-type handset.Handset

#### Figure 1: Functional Components of a Digital Handset/Terminal

In this diagram, we don't show specific connections between the microprocessor, the DSP, and the various boxes within the handset. Typically, they are all interconnected. In fact, some functions may be implemented by either processor. This saves board area at the expense of processor bandwidth. Let's assume the microprocessor handles baseline tasks like managing the display and the keyboard, but the DSP does channel coding/decoding and other signal processing tasks in the phone. The microprocessor handles dialing.

Let's simply look at sending and receiving audio. The microphone delivers audio signal to the A/D converter, creating a bit-stream. Fidelity and efficiency require redundancy elimination and compression. This is done in the speech coder (typically adaptive multirate). Forward Error Correction (FEC) occurs in the channel coder (Viterbi today, Turbo tomorrow). Coding adds back redundancy, but dropped bits can be recovered. CDMA channel spreading has been introduced in the U.S. and Korea, but others may use TDMA, SCDMA or WCDMA. The digital signal finally gets to the RF modulator and RF amplifier where it becomes one of several signal types (again, depending on the phone standard). At this point, it is analog. Today, these are in the gigahertz range and focused on octal phase shift keying. The duplexer is inserted to switch between receiving and sending at the antenna.

On the receiving end, the signal hits the antenna, slides through the duplexer and is amplified and demodulated, becoming digital. The Rake Receiver "despreads" the received bits and forwards the signal to the channel decoder, which reconstructs the possibly corrupted digital signal and passes it on to the speech decoder. The speech decoder corrects bit-dropout and should resemble the digital version of the original analog signal. This forwards to the D/A converter, which, when filtered and amplified (not shown), drives the earphone.

If the phone is going to support 3G capability, typically it must handle other standards (2G, 2.5G and GPRS) because different countries are at different levels of deployment. Why pay for a high-end phone and be able to only use it on the high end systems? Would you want to carry multiple phones, or should the manufacturer make sure your super handset just works wherever you are? Given that the latter is the case, your handset is basically three or four phones, depending on what communication link you are connecting to. It's a lot to ask, but 3G isn't about signaling, quality and compatibility, as much as it is about applications.

#### **Applications**

By now, you should have noticed the big box on the right hand side of Figure 1. That is reserved for advanced applications—things that go beyond making a call. Let's revise Figure 1 to set the stage for the kinds of things we will need to add applications. For starters, cell phone standards committees categorize applications according to parameters like guaranteed bit rate, variable/fixed delay, asymmetric/symmetric traffic and whether or not buffering is allowed. In terms of words we can relate to, those categories translate into conversational class, streaming class, interactive class and background class. These designations are based on the properties of those classes of applications. For instance, an ordinary conversation cannot tolerate long delays and echoes, as such things upset users. Lots of image dropout on a video data-stream also upsets users. So, by thinking through the needs of whole classes of applications, developers arrive at important quality factors. Listed below are some of potential cell phone applications; some may cross over more than one of the classes listed above.

- 1. MP3 music

- 2. Distance Learning

- 3. Online Retail

- 4. Travel booking

- 5. E-books

- 6. Distance Learning

- 7. Online Retail

- 8. Travel booking

- 9. M-commerce

- 10. Online trading

- 11. Mobile banking

- 12. Gambling

- 13. Games Interactive toys

- 14. Video movie rental

- 15. Virtual radio station

- 16. Virtual TV station

- 17. Newspapers

- 18. Photo album

- 19. Video Conferencing

- 20. Field service

- 21. Business kiosks

- 22. Secure monitoring

- 23. telemedecine

- 24. Mobile clinics

- 25. Email

- 26. Secure monitoring

- 27. Targeted advertising

- 28. Free trials

- 29. Remote metering

- 30. Remote control

- 31. Mobile speed cameras

- 32. Remote surveillance

- 33. Ticket purchases

- 34. Showtime information

- 35. Vending machines

- 36. Parking meters

- 37. Buying Crossword puzzles

- 38. Navigation

- 39. Finding ATM money machines

- 40. And many more . . .

Each application has its own particular needs, so it might be appropriate to consider a few of them individually. For instance, music via MP3 files could be done entirely in software, the same way that PCs can play files. If the processors are burdened with channel coding/decoding and possibly with decryption, it might be more feasible to include an MP3 decoder chip within the phone, or as an add-on. Video movie rental would probably have the files being downloaded via GPRS and linked through the Internet. Clearly, vendors renting the files would want to assure their MPEG-4 files weren't being delivered to pirates. Vendors would insist on encryption as well as compression. Adding these to the channel decoding exhausts today's processors and drains batteries. There would also be a need for buffering frames, to support dropout in the Internet protocol. Some applications might require JPEG, MPEG-4, MP3, encryption and channel coding. This suggests the need for additional offloading logic. Let's look at a commercial chipset for doing all of this, and then discuss offloading.

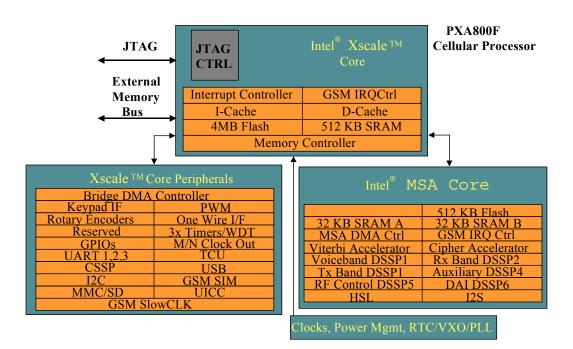

#### Cell Phone Chipsets

Figure 2 shows an Intel PXA 800F block diagram. Note that this multifaceted chipset is designed to integrate all the key functionality for the baseline, base-band operations, with a clear focus on using software to handle a broad range of other applications.

#### Figure 2: Intel PXA 800F Cellular Chipset

Manufacturers such as Motorola, Qualcomm and Texas Instruments offer their versions of chipsets that attempt do deliver the maximum capability in the minimum number of chips. Each is somewhat different in functional partitioning. The thing that is difficult for them to do is add enough flexible functionality to adapt to arbitrary future applications. We frequently see pins referring to keyboard interfaces, or display interfaces, which is great, but they are all different. Some of the European UMTS terminals resemble pocket computers with wide screen displays and full computer keyboards as opposed to 12-16 keys on a simple cell phone. Adaptation logic is needed to use these chipsets with broader applications.

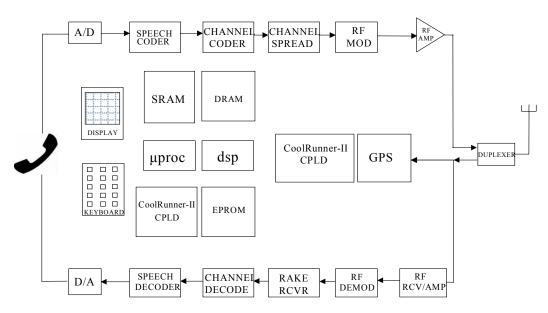

## Picking the Right Mix

Figure 3 shows an application that is not on the list—Global Positioning Satellite (GPS) service. It can use the same antenna as the phone receiver/transmitter, but it will drag the satellite signals into the chip, collect the data and deliver the co-ordinates of your location to the DSP. Emergency police/ambulance calls need this.

Figure 3: GPS Added into a Phone

In this case, it is impossible for the DSP or the microprocessor to "grow another radio chip." As long as the standard RF demodulator is being used, a second will be needed to support the GPS. The GPS will need to be interfaced to the processor buses to get data. The CoolRunner-II CPLD easily creates bus interfaces, interrupts and control operations for the processors, tying peripherals in.

Another example would be a camera. Adding a CMOS imaging chip requires interfacing it to the processor buses, along with additional memory to buffer images. Cameras come with either parallel or serial interfaces. Why be constrained to THEIR choice of peripherals in YOUR product?

For some time to come, applications will consist of adding in special application circuitry and interfacing it into the processor buses. Given that, how can a designer select the right application-specific circuits to add in, so that one ASIC could be built to interface them all? Basically, they can't. Below is an array of application modules that might be added into the phone:

- MP3

- MPEG-4

- Compact Flash +

- Video Camera

- GPS

- MMC/SDI

- More SRAM

- More DRAM

- More EPROM

But what about new applications that are not in this group? There are applications yet to come that we can envision, but whose exact specifications we cannot wholly anticipate. Designing for their arrival is sometimes called "future proofing."

It is true that some applications are better served by microprocessor code dropped into on board EPROM, but that can only happen as long as the processor bandwidth is available for the application. If this cannot be done, either more processors or additional silicon needs to be added. Either way, the application will need to interface into the phone bus network, and that will require programmable logic, very low power programmable logic.

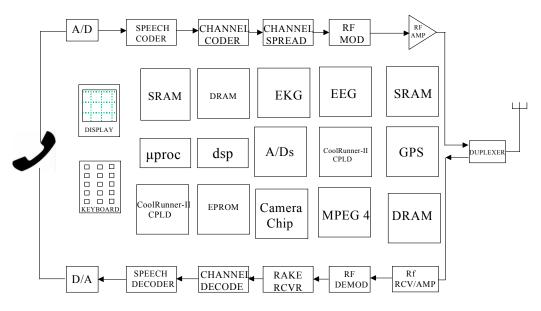

#### MediPhone—A Speculative Example

To drive home some of these ideas, consider an idea for a product that probably does not exist today, but easily could in the near future. It will be marketed under the name "MediPhone" and will target segments of the population that require quick medical support. This would include the growing population of elderly citizens (frequently with enough money to buy these) as well as handicapped people needing close monitoring. See Figure 4 for an "artist" conception of this futuristic phone.

Figure 4: MediPhone Block Diagram

MediPhone works like this:

- 1. A heart attack (or other medical emergency occurs)

- 2. The victim or friend dials Emergency (911 in the U.S.)

- 3. Personnel receiving the call at a medical facility recognize the phone is "MediPhone" equipped and extract the geographic location of the emergency using GPS

- 4. The medic directs the friend to place the cell phone on the victim's face

- 5. A video camera scans the Iris for dilation to determine shock level

- 6. The friend is directed to attach small electrodes to the forehead/ear and chest of the victim, where pulse is taken and EEG/EKG measurements are driven into the Internet. Everything is attached to the phone.

- 7. Temperature is measured by physical contact of the forehead with the victim off the back of the phone

- 8. Microphone gain is adjusted to listen to the victim's breathing

- 9. It is determined that a heart attack has occurred and the friend is directed to elevate the feet and is given directions for CPR from the medic while an ambulance is dispatched

- 10. Ten minutes later, the ambulance team takes over and the MediPhone medic is released. For insurance reasons, all transaction data are encrypted, compressed and stored on CD for future reference.

- 11. The victim is saved and lives happily ever after . . .

In order to do this, MediPhone requires greater application functionality than discussed so far. Adding instrumentation amplifiers, A/Ds, transducers and support circuitry go beyond just having video and GPS as mentioned earlier. CoolRunner-II CPLDs would interface the various items needed to support MediPhone. The associated processor buses and memory interfaces are needed to support the capture of the information taken. Other ideas quickly come to mind (WeatherPhone, ToxicGas Phone, etc.)

#### Power and Packaging are Key!

We have not yet mentioned power in this discussion, but it may be a key element in figuring out a solution, at least at the outset. Power management requires a careful balance of dynamic operations within a cell phone. Do we add in specialty silicon, or do we just use a bigger EPROM and do it in software? As mentioned earlier, some choices are made for us. It would be ideal to just do it in the software, unless the bandwidth requirement on the processor(s) exceeds what could be done with a separate chip interfaced into the phone bus. Nonetheless, adding power consuming chips must be balanced against adding incremental code space, which also increases the power consumption. Whether you are interfacing more EPROM or additional ASSP silicon, CoolRunner-II is the ideal low power interface, with standby currents as low as 14 microamps. For power management, CoolRunner-II CPLDs are frequently used to enable/disable the power delivery to other chips within a system. So, if you are not using your camera or GPS capability, they can be automatically shut down to minimize power draw.

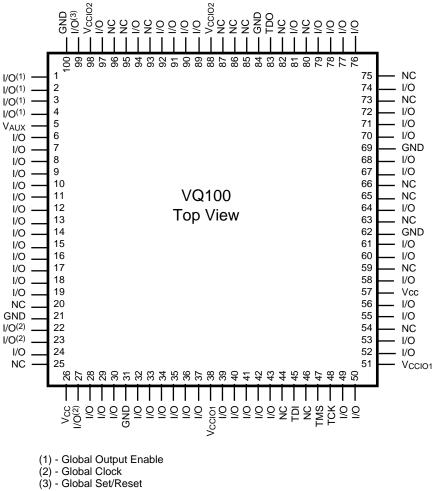

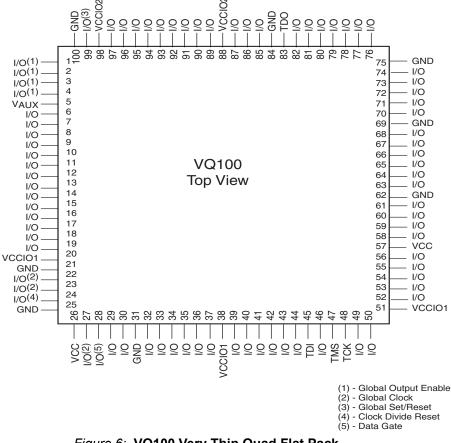

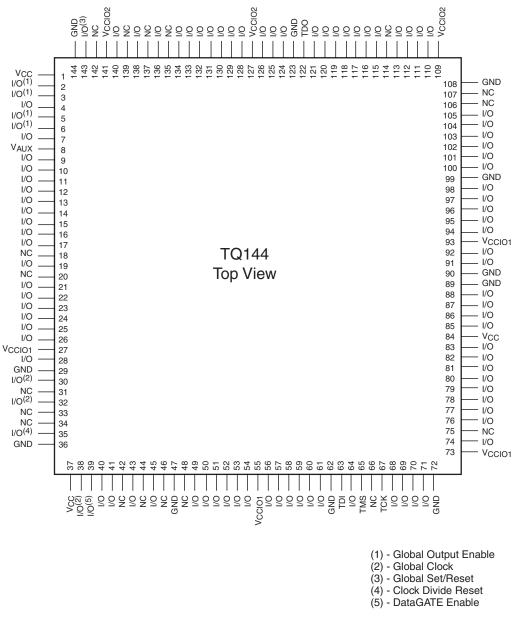

In addition to the unsurpassed power savings at high performance (clocking in the 300+ MHz range) provided by CoolRunner-II RealDigital technology, it is also critical to note that CoolRunner-II devices are offered in a wide range of very small packages. Table 1 shows part densities, available packages and other key features of CoolRunner-II CPLDs.

|                               | XC2C32A | XC2C64A | XC2C128 | XC2C256 | XC2C384 | XC2C512 |

|-------------------------------|---------|---------|---------|---------|---------|---------|

| Macrocells                    | 32      | 64      | 128     | 256     | 384     | 512     |

| Max I/O                       | 33      | 64      | 100     | 184     | 240     | 270     |

| T <sub>PD</sub> (ns)          | 3.8     | 4.6     | 5.7     | 5.7     | 7.1     | 7.1     |

| T <sub>SU</sub> (ns)          | 1.9     | 2.0     | 2.4     | 2.4     | 2.9     | 2.6     |

| T <sub>CO</sub> (ns)          | 3.7     | 3.9     | 4.2     | 4.5     | 5.8     | 5.8     |

| F <sub>SYSTEM1</sub><br>(MHz) | 323     | 263     | 244     | 256     | 217     | 179     |

#### Table 1: CoolRunner-II CPLD Family Parameters

| Looking<br>Forward to 4G | The fourth generation cell phones are already being referred to as Software Defined<br>Radio (SDR), because so many things can be more easily (in theory) changed with<br>software. Processor speeds in the gigahertz range result in swift, agile flexibility.<br>However, as mentioned earlier, software cannot "grow" a camera. Software cannot<br>add in a bus interface to Compact Flash +. Software cannot grow another radio<br>channel. Only hardware can do some things, and when developers know neither<br>when nor what the next new "thing" will be, only programmable logic can solve their<br>development quandary. CoolRunner-II CPLDs provide the future proofing to help<br>drive 4G cell phones. |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Conclusion               | We have focused, at a high level, on requirements of cell phones and on the capabilities of CoolRunner-II CPLDs for meeting those requirements. Given the current trend toward packing as much functionality as possible into handsets without increasing their power consumption, CoolRunner-II is an ideal choice for building phones that need to quickly adapt to new applications still on the horizon.                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                          | Product differentiation will ultimately result in winning designs. If developers want to cinch their winning positions, they must ensure that their designs have distinctive, useful applications that outdo those of their competitors. Using CoolRunner-II CPLDs to plan for future feature changes can contribute enormously to speedy and cost-effective introduction of such applications.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| References               | <ol> <li>UMTS Networks, Architecture, Mobility and Services, H. Kaaranen, A. Ahtiainen, L.<br/>Laitinen, S. Naghian, V. Niemi, 2001, John Wiley &amp; Sons, Ltd.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                          | 2. Services for UMTS (Creating Killer Applications in 3G), T. Ahonen, J. Barrett, editors, 2002, John Wiley & Sons, Ltd.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                          | 3. 3G Wireless Demystified, L. Harte, R. Levine, R. Kikta, 2002, McGraw-Hill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                          | 4. "The Mobile Phone Meets the Internet," M. W. Oliphant, August 1999, <i>I.E.E.E. Spectrum</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                          | <ol> <li>"Evolving Cellular Handset Architectures but a Continuing, Insatiable Desire for<br/>DSP MIPs," M. L. McMahan, March 2000, Texas Instruments Application Report<br/>SPRA650</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Further Reading          | The following links provide information useful for handset and CoolRunner-II design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CoolRunne                | r-II Design Kit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

http://www.xilinx.com/products/cr2/design kit.htm

#### **Application Notes**

Select the link below for a complete list of links to over 75 CoolRunner-II Application Notes. The list includes notes on the PicoBlaze Microcontroller, Keypad Scanners, Level Translation, Bus Controllers, Memory Interfaces, and Handheld Designs.

#### **CoolRunner-II Application Notes**

If you are looking at a printed copy of this document, go to www.xilinx.com and go to the documentation link.

#### **CoolRunner-II Data Sheets**

http://direct.xilinx.com/bvdocs/publications/ds090.pdf (CoolRunner-II Family Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds091.pdf (XC2C32 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds092.pdf (XC2C64 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds093.pdf (XC2C128 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds094.pdf (XC2C256 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds095.pdf (XC2C384 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds095.pdf (XC2C384 Data Sheet) http://direct.xilinx.com/bvdocs/publications/ds095.pdf (XC2C384 Data Sheet)

#### **CoolRunner-II White Papers**

The following link takes you to the CoolRunner-II White Papers. If you are looking at a printed copy of this document, go to www.xilinx.com and go to the documentation link.

**CoolRunner-II White Papers**

#### Revision History

The following table shows the revision history for this document.

| Date     | Version | Revision                             |

|----------|---------|--------------------------------------|

| 06/30/03 | 1.0     | Initial Xilinx release.              |

| 07/04/05 | 1.1     | Update of specifications in Table 1. |

# Implementing Keypad Scanners with CoolRunner-II

#### Summary

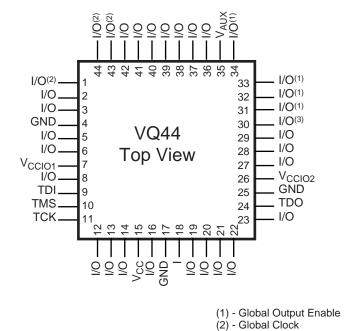

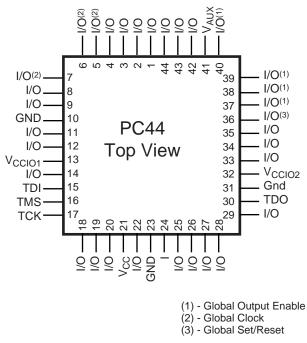

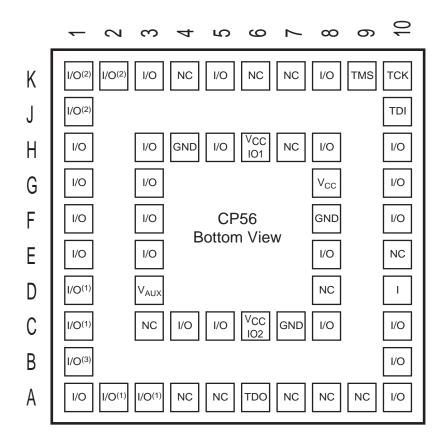

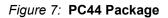

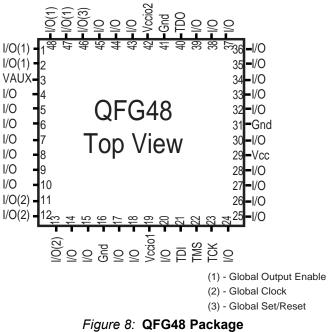

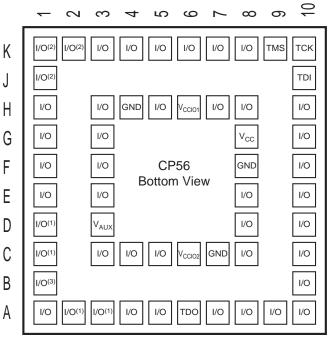

This application note provides a functional description of Verilog source code for a keypad scanner. The code is used to target the lowest density, 32-macrocell CoolRunner<sup>TM</sup>-II XC2C32A CPLD device in a CP56 package (6 mm x 6 mm). The keypad accommodated in this design has 8 rows and 8 columns. The design can easily be scaled to target keypads with more or less rows/columns. For instance, a keypad with 7 rows and 7 columns would allow the design to fit in the smallest QFG32 package (5 mm x 5 mm). To obtain the Verilog source code described in this document, see "Verilog Code," page 26, for instructions.

#### Introduction

As handheld devices such as cell phones pack more and more features into them, they require more effective ways of entering data. Most cell phones, for example, use the standard DTMF style keypad and a multi-tap process to enter alphanumeric data; however, for larger amounts of data multi-tapping becomes cumbersome. More and more high-end phones are therefore employing QWERTY keypads that make entering data easier and quicker.

Going from a DTMF to a QWERTY keypad requires more I/O. For instance, a DTMF keypad might have 4 rows and 3 columns, where a QWERTY keypad might have 8 rows and 8 columns. This can vary depending on the requirements.

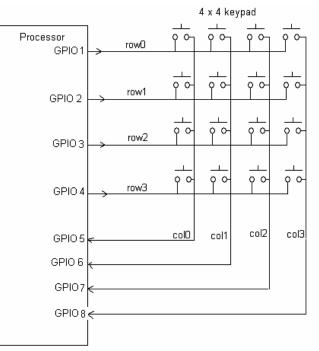

Typically, a processor (or ASIC) is used to interface to the keypad's rows and columns. The processor scans the rows and monitors the columns for a logic change. When a change occurs, it indicates that one of the buttons in that column was pressed. By knowing which row was being scanned, and which column changed state, the processor can deduce which specific button was pushed. Additional functions such as debounce are also typically employed. Figure 1 shows how a simple 4 x 4 keypad uses 8 GPIO of a processor.

© 2005 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

www.xilinx.com

#### Expanding I/O

Designers faced with accommodating a keypad requiring more I/O might find their existing processor (or ASIC) does not have enough GPIO ports. One solution is to use a CPLD as an I/O expander that reduces the I/O requirement of the processor.

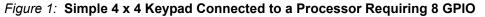

Figure 2 shows a CPLD interfacing to the keypad rows/columns on one side, and the processor's available GPIO on the other. In this example, an 8 x 8 keypad requires the same number of processor GPIO ports as the 4 x 4 keypad (actually one less) when a CPLD is used. Without a CPLD, the processor would require 16 GPIO ports instead of 7.

Figure 2: CPLD Expands I/O and Reduces the Processor's GPIO

#### Scanning and Encoding

Besides reducing the processor's GPIO requirements, the CPLD also scans the rows and monitors the columns for a change in state. When a key is pressed, the CPLD stops scanning and immediately sends an encoded word out to the processor. The encoded word indicates which key was pressed.

In the example shown in Figure 2, there are six bits used to represent the encoded word. Six bits provides 2<sup>6</sup> or 64 different values each representing a different key. However, one value needs to be used to represent the state when no keys are pressed. Therefore, only 63 keys can be represented in this example.

All 64 keys most likely would not be needed in a typical application. If they were, there are many options with a programmable CPLD. For instance, a CPLD could generate an enable signal to the processor that would indicate when a key is being pressed (that is, when the encoded value was valid). This would require one more GPIO on the processor.

The processor is still required to monitor for changes on its GPIO, only it would not have to deduce which key was pressed since this information is encoded in the six bit word. Debounce will also be required. This can be performed in the CPLD or the processor. Performing this in the processor would keep the size of the CPLD to a minimum.

#### CPLD Design Details

**Note:** The following details describe how the available Verilog reference design is implemented. The concept and design are relatively simple. Additional functionality can be added depending on specific design requirements.

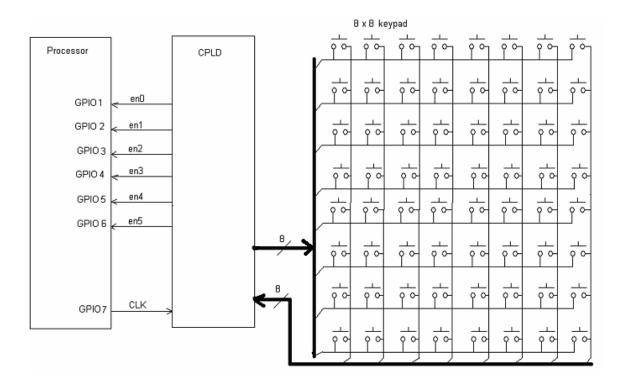

To scan the keypad rows, a barrel shift register is initialized with all ones except for one bit preset to a zero. Each bit of the shift register drives a CPLD output pin that is connected to a row of the keypad. As the shift register is clocked the zero shifts through the barrel shifter and scans the rows by driving them low one at a time.

The columns are inputs to the CPLD. Each input is pulled up with an internal pull up resistor. When no keys are pushed, all column inputs to the CPLD are passively pulled up to a logic high state. All column inputs are AND'd together. A logic one at the output of the AND gate indicates no keys are pressed. The output of the AND is used as an enable to the shift register.

When a key is pressed, a connection between a row and column is made. The column with the key being pressed will be driven low by the row associated with that key. The output of the AND will go low and disable the shift register for how ever long the key is pressed.

At this point the shift register is driving the row of the key being pressed to a low, and the column of that key is also at a low. Two encoders are used, one for the row bits (outputs of the shift register), and another for the column inputs. The outputs of the two encoders are grouped together to form the resulting encoded word that is presented to the processor. Figure 3 shows a block diagram of these functions.

Figure 3: Block Diagram

| Implementation and Verification | including the software, yo                                                                                                                                                                                                                                                                                                                                            | e Verilog sou<br>u can obtair                                                                                                   | implemented in Verilog. A Xilinx ISE <sup>TM</sup> software project is zipped up, urce file, Verilog testbench, and UCF file. If you do not have Xilinx n ISE WebPACK <sup>TM</sup> for free from the Xilinx website. WebPACK will give ed to complete any CPLD project.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                 |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                 | v to initialize the barrel shifter with a pattern of ones and a zero. It also<br>the column inputs with internal pull up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                 | custom Mod                                                                                                                                                                                                                                                                                                                                                            | elSim .do fi                                                                                                                    | voked from within Project Navigator, which will automatically run a ile. The .do file will compile the source code, open a waveform window the simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                 | periodically                                                                                                                                                                                                                                                                                                                                                          | connecting a                                                                                                                    | is a clock for stimulus and also simulates the pressing of buttons by<br>a row with a column. This is done until all possible combinations of rows<br>ted, and then repeats.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Verilog Code                    | CODE AS C<br>REPRESEN<br>FROM ANY<br>DISCLAIMS<br>OTHERWIS<br>MERCHAN<br>THE ADEQU<br>WARRANT<br>CLAIMS OF<br>REFERENC                                                                                                                                                                                                                                                | DNE POSSIE<br>ITATION TH<br>CLAIMS OI<br>ANY WARE<br>E, AND XIL<br>TABILITY, N<br>JACY OF T<br>OR REPR<br>ANY THIRI<br>E DESIGN | HAVE PATENTS ON THE CODE PROVIDED. BY PROVIDING THIS<br>BLE IMPLEMENTATION OF THIS DESIGN, XILINX IS MAKING NO<br>IAT THE PROVIDED IMPLEMENTATION OF THIS DESIGN IS FREE<br>F INFRINGEMENT BY ANY THIRD PARTY. XILINX EXPRESSLY<br>RANTY OR CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR<br>INX SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF<br>ON-INFRINGEMENT, OR FITNESS FOR A PARTICULAR PURPOSE,<br>HE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO ANY<br>ESENTATION THAT THE IMPLEMENTATION IS FREE FROM<br>D PARTY. FURTHERMORE, XILINX IS PROVIDING THIS<br>"AS IS" AS A COURTESY TO YOU.<br>xilinx.com/bvdocs/appnotes/xapp512_verilog.zip |  |  |

| Conclusion                      | Since the CPLD is reprogrammable, adding a control line, changing the mapping of the encoded word, or accommodating different keypads is possible with the same device. Additionally, other "glue" functions can be absorbed into the CPLD, such as voltage translators.                                                                                              |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                 | A specific CPLD device (i.e., part number) can be used to accommodate different keypads and even different applications because it's programmable. This helps boost the volume (lowers cost), and reduces risk since changes can be made even after it's soldered down.                                                                                               |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                 | Coolrunner-II also is designed for low power, making it a good choice for battery powered applications, such as cell phones, PDAs, and other portable devices. They also have additional features that augment its low power. Multiple I/O banks can be used for voltage translation, which is another typical application in devices with a mixture of technologies. |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Additional                      | CoolRunner-II Data Sheets, Application Notes, and White Papers                                                                                                                                                                                                                                                                                                        |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Information                     | Access to all Xilinx Data Sheets, Application Notes, and White Papers<br>Device Packages                                                                                                                                                                                                                                                                              |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                       | <u>Rayes</u>                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Revision<br>History             | The following table shows the revision history for this document.                                                                                                                                                                                                                                                                                                     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| i listoi y                      | Date                                                                                                                                                                                                                                                                                                                                                                  | Version                                                                                                                         | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                 | 04/04/05                                                                                                                                                                                                                                                                                                                                                              | 1.0                                                                                                                             | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

NAND gate references on page 3 changed to AND gates.

1.1

05/06/05

# Level Translation Using Xilinx **CoolRunner-II CPLDs**

#### Summary

As electronic design has advanced over the years, more and more I/O standards have been created. Since the days when the 5V CMOS and TTL standards were the prevalent standards with which to design logic circuits, there have been a lot of changes. Today, there are many voltage standards operating at different voltages with different thresholds. This application note explains how to use a Xilinx CoolRunner<sup>TM</sup>-II CPLD to translate between different voltage levels.

#### Introduction

A typical electronic system will no longer operate at only one voltage. The most popular voltages used to interface between components on a board are 3.3V, 2.5V and 1.8V. However, more frequently, devices need to interface to 'unusual' voltages.

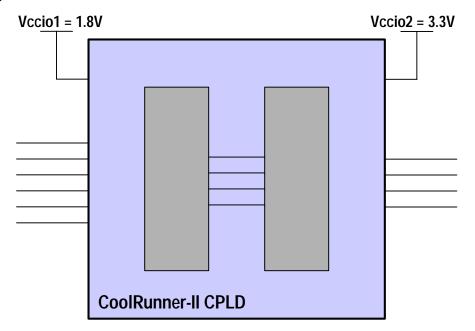

Since the introduction of the CoolRunner-IIA parts (XC2C32A and XC2C64A), all Xilinx CoolRunner-II devices have multiple I/O banks. The XC2C32A, XC2C64A, XC2C128, and XC2C256 have two banks each, and the XC2C384 and XC2C512 have four banks each. This means that the  $V_{CCIO}$  rail (the power supply for the device I/O) is split, enabling I/O in different banks to be powered at different voltage levels. Each I/O bank can support one V<sub>CCIO</sub> voltage at a time. The supported I/O standards for the CoolRunner-II device can be seen in Table 1 below.

| IOSTANDARD<br>Attribute                       | Output V <sub>CCIO</sub> | Input V <sub>CCIO</sub> | Input <sup>(1)</sup><br>V <sub>REF</sub> | Board<br>TerminationVoltage<br>V <sub>TT</sub> |

|-----------------------------------------------|--------------------------|-------------------------|------------------------------------------|------------------------------------------------|

| LVTTL                                         | 3.3                      | 3.3                     | N/A                                      | N/A                                            |

| LVCMOS33                                      | 3.3                      | 3.3                     | N/A                                      | N/A                                            |

| LVCMOS25                                      | 2.5                      | 2.5                     | N/A                                      | N/A                                            |

| LVCMOS18                                      | 1.8                      | 1.8                     | N/A                                      | N/A                                            |

| LVCMOS15 <sup>(2)</sup>                       | 1.5                      | 1.5                     | N/A                                      | N/A                                            |

| HSTL_1 <sup>(3)</sup>                         | 1.5                      | 1.5                     | 0.75                                     | 0.75                                           |

| SSTL2_1 <sup>(3)</sup>                        | 2.5                      | 2.5                     | 1.25                                     | 1.25                                           |

| SSTL3_1 <sup>(3)</sup>                        | 3.3                      | 3.3                     | 1.5                                      | 1.5                                            |

| <ol> <li>For information on assist</li> </ol> | aning Vref pins, see 🗙   | APP399                  | L                                        | 1                                              |

#### Table 1: Supported I/O Standards in CoolRunner-II Family

or information on assigning vier plus, see

2. LVCMOS15 requires use of Schmitt-trigger inputs.

HSTL\_1, SSTL2\_1 and SSTL3\_1 are supported on XC2C128 and larger 3.

The I/O characteristics of each standard can be found in the device specific CoolRunner-II Datasheets, for example XC2C128. More information about each of the I/O standards can be found in XAPP382. For information about interfacing to 5V, see XAPP429.

© 2005 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### Configuring I/O to Use I/O Standards

The designer specifies which I/O standard to use at the time of design entry. I/Os can be configured to operate at different I/O standards in a number of ways.

#### Default

The default I/O Standard can be set in the process properties for the Fit process in the ISE software. The use of the default I/O Standard will set all I/O used in the design to the I/O standard specified. This is useful if all the I/O are powered at the same voltage. However, this application note is discussing interfacing between different voltages, so another I/O standard assignment method is required.

#### PACE

The Xilinx Pinout Area and Constraints Editor (PACE) tool can be used to assign a variety of constraints, including pin locations, slew rate, Schmitt trigger and I/O standard. The package diagram distinguishes between I/O banks by using different colors.

The Design Object List then enables you to assign I/O standards to the I/O pins in the design. If the banking rules are broken, then PACE will issue a message that the I/O standard is not  $V_{CCIO}$  compatible.

#### UCF

The final method of assigning I/O standards in the software is to enter them directly into the User Constraint File (UCF). The syntax for entering I/O standard constraints into the UCF is as follows:

```

NET "user_net" IOSTANDARD = xx ;

```

Where **xx** is one of the permissible values: LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15, LVTTL, and for devices of 128 macrocells and above, HSTL\_1, SSTL2\_1 and SSTL3\_1.

Xilinx recommends the use of the Default assignment in co-operation with PACE to get the optimum results, since PACE has the design rules check that the UCF entry method lacks.

#### Using the CPLD as a Level Shifter

In addition to knowing of how to configure the I/O of the CPLD at different voltages, it is also necessary to have an understanding of how to use the device as a level shifter. It is possible to have this device act as a route-through to simply shift, for example, 1.8V inputs to 3.3V outputs. This would simply require a logical assignment of the input bus to the output bus, and would use one pin per input/output, and one product term and one macrocell per output.

Even in the smallest device in the CoolRunner-II family, the XC2C32A, performing this translation on an 8-bit bus would utilize less than one quarter of the resources. As the input signals must go through the central interconnect switch, they can be assigned to any output pin required by user. This makes the CPLD perfect for performing additional functions such as bit-swapping of the input bus, or changing from little-endian to big-endian format. CoolRunner-II CPLDs have a very fast  $T_{PD}$  (propagation delay), as fast as 3.8 ns in the XC2C32A -4, so very little delay will be incurred by using a CPLD in this situation. It is also important to note that, due to the uniform nature of the architecture, all signals going through a similar path in the device will incur a similar delay and will, therefore, have minimal skew from each other.

While this is a perfectly legitimate use for a CPLD, there are a lot of other resources available that can be used to perform operations on the incoming data.

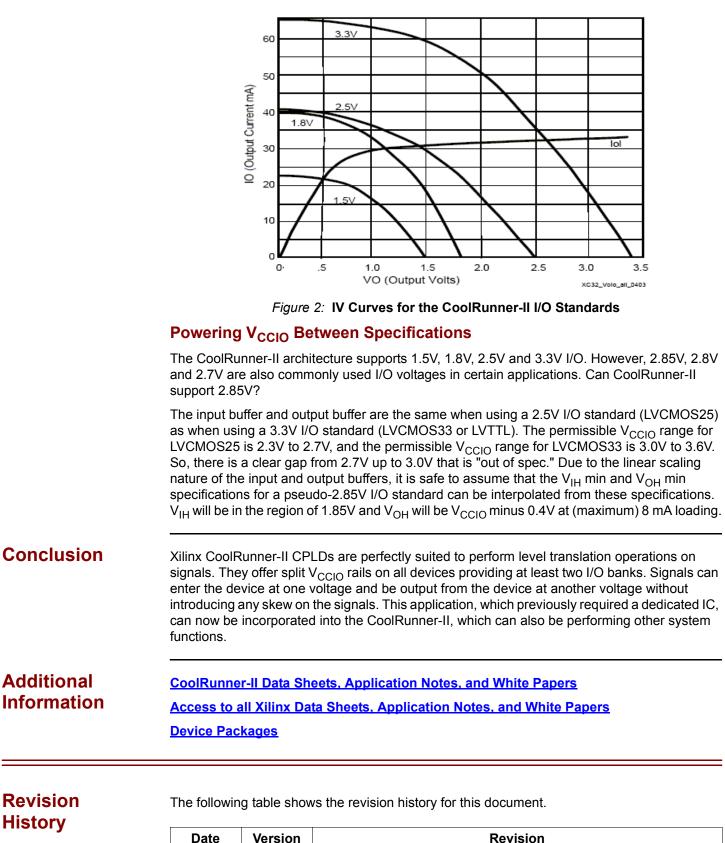

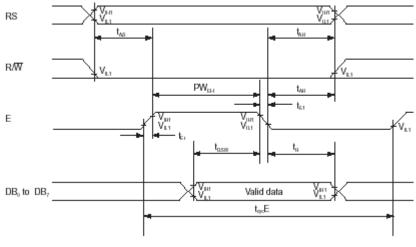

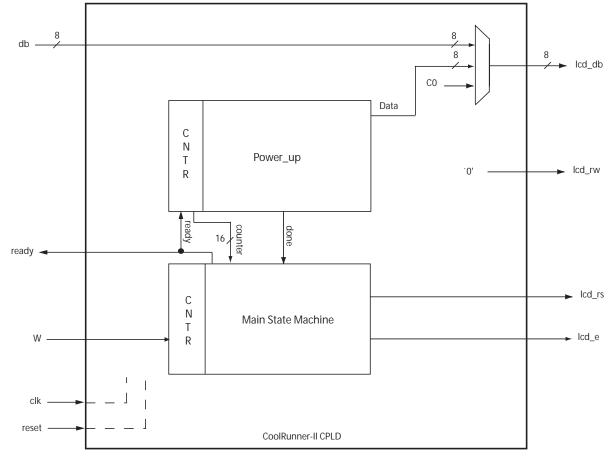

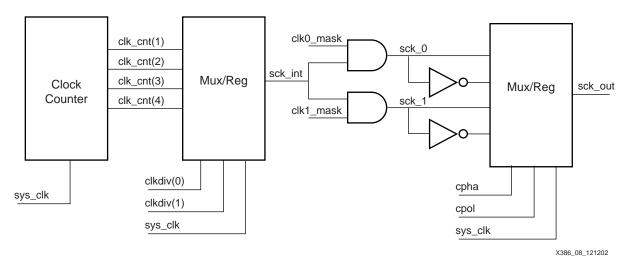

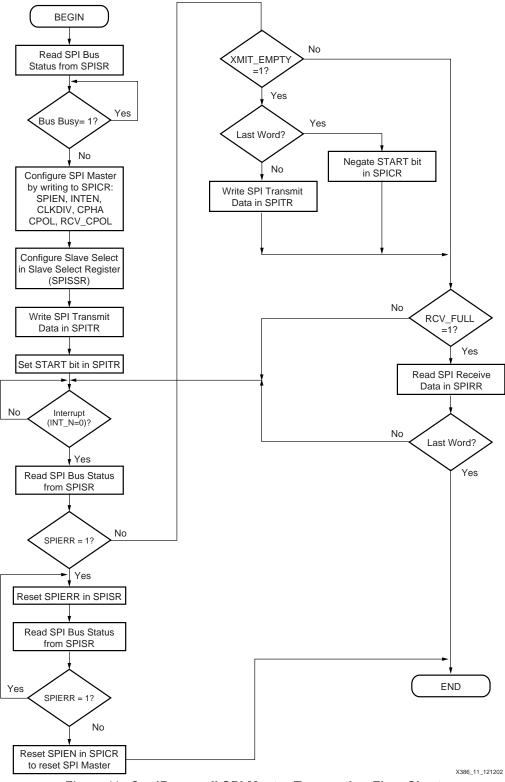

#### Incorporating the Level Shifter into a Common Interface