## Maxim > Design Support > Technical Documents > Application Notes > Power-Supply Circuits > APP 1775

Keywords: MAX1957, VTT, DDR-SDRAM, DDR, termination voltage, dc-dc switching power, double data rate, PWM, buck controller

## APPLICATION NOTE 1775

## Power Supply for DDR-SDRAM Termination Operates From 3V to 5.5V Input

Oct 21, 2002

Abstract: Double data rate (DDR) synchronous dynamic random access memory (SDRAM) has gained popularity recently. The DDR memory needs active termination,  $V_{TT}$ , that tracks the main memory voltage  $V_{DDQ}$ . This application note provides a switching regulator solution to provide a  $\frac{1}{2}$  tracking output for  $V_{TT}$  termination using MAX1957 pulse-width modulation (PWM) buck controller.

Double data rate (DDR) synchronous dynamic random access memory (SDRAM) has gained popularity because it can deliver double the data rate and reduced power consumption, compared to SDRAM at the same clock speed. These advantages come with more complex termination voltage requirements.

The DDR termination supply, V<sub>TT</sub>, must now be capable of sourcing as well as sinking current. V<sub>TT</sub> must track  $\frac{1}{2}V_{DDQ}$ , the output supply voltage (currently  $V_{DDQ}$  is 2.5V, with ±3% accuracy). The input receiver is now a differential stage, requiring a reference bias,  $V_{TTR}$ , which must track the termination voltage  $V_{TT}$  to within ±40mV (refer to JDEC standards JDSD79 and JDSD8-9).

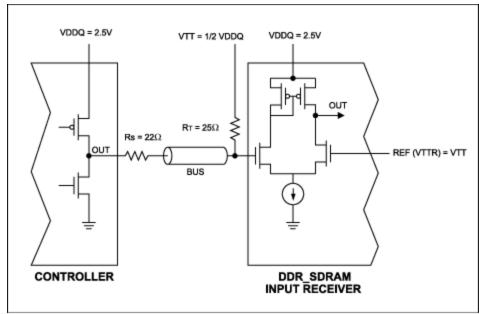

**Figure 1** is a typical output buffer and input receiver stage with series stub termination logic for 2.5V (SSTL-2) in a DDR\_SDRAM single terminated system. For double termination, used in the case of a long bus, two RTs terminate each end of the bus.

Figure 1. Single terminated SSTL-2 DDR\_SDRAM system.

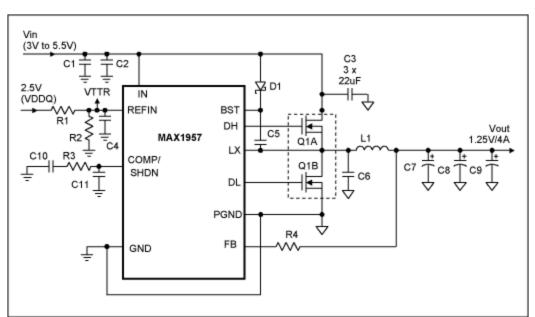

The MAX1957 circuit in **Figure 2** provides V<sub>TT</sub> and V<sub>TTR</sub> for DDR\_SDRAM. The MAX1957 has a reference input (REFIN) that connects to the non-inverting input of the internal error amplifier to regulate the output V<sub>TT</sub> to the same voltage as REFIN. To have V<sub>TT</sub> and V<sub>TTR</sub> track  $\frac{1}{2}$ V<sub>DDQ</sub>, REFIN is developed by a resistor voltage divider (R1 and R2) from V<sub>DDQ</sub>. Capacitor C6 is a decoupling filter. The MAX1957 operates as constant frequency PWM, such that V<sub>TT</sub> can source and sink current as required by the DDR-SDRAM. Components used in Figure 2 provide over 3 Amperes of source and sink capability, which is the maximum requirement for a 128Mb memory system.

Figure 2. MAX1957 typical application circuit for V<sub>TT</sub> and V<sub>TTR</sub>.

## Table 1. Component List for the MAX1957 Typical Application Circuit

| Component  | Quantity | Description                                                  |

|------------|----------|--------------------------------------------------------------|

| C1         | 1        | Cap. 10µF/6.3V X5R Ceramic.<br>Taiyo Yuden: JMK212BJ106MG    |

| C2         | 1        | Cap. 4.7µF/6.3V X5R Ceramic.<br>Taiyo Yuden:JMK212BJ475MG    |

| C3         | 3        | Cap. 22µF/6.3V                                               |

| C4,C5      | 2        | Cap. 0.1µF/50V X7R Ceramic.<br>Taiyo Yuden UMK107BJ104KA     |

| C6         | 1        | Cap. 1500pF/50V X7R Ceramic.<br>Murata GRM89X7R152K50        |

| C7, C8, C9 | 3        | Cap. 270µF/2V SP Capacitor.<br>Panasonic EEFUE0D271R         |

| C10        | 1        | Cap. 470pF/50V X7R Ceramic.<br>Murata: GRM89X7R471K50        |

| C11        | 1        | Cap. 68pF/50V X7R Ceramic.<br>Murata: GRM39COG680J50         |

| D1         | 1        | Diode, Schottky, 30V, 100mA, SOT-<br>23.<br>Central: CMPSH-3 |

| IC         | 1        | IC, Synch Buck controller: MAX1957                           |

| L1         | 1        | Inductor, 2.7µH, 6.6A.<br>Coilcraft: DO3316P-272HC           |

| R1, R2     | 2        | Resistor, 0805, 1K, 1%                                       |

| R3         | 1        | Resistor 51K, 0805, 5%                                       |

| R4         | 1        | Resistor 10K, 0805, 5%                                       |

| Q1/2       | 1        | Transistor, Dual MOSFET<br>Fairchild FDS6890A 20V, 0.018Ω    |

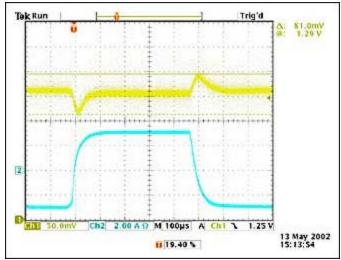

Figure 3 shows V<sub>TT</sub> and V<sub>TTR</sub> when subjected to a -3A to +3A step load at V<sub>TT</sub>. The peak voltage deviation of V<sub>TT</sub> is less than  $\pm$ 40mV.

Figure 3. Top trace: voltage  $V_{TT}$  (AC coupled). Bottom trace: current ITT step from -3A to +3A and from +3A to -3A.

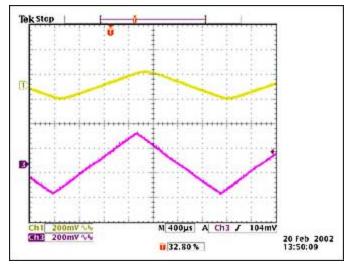

**Figure 4** shows  $V_{DDQ}$ ,  $V_{TT}$  tracks to half of  $V_{DDQ}$  as  $V_{DDQ}$  ramps up and down, showing the change in  $V_{TT}$  is half of the change in  $V_{DDQ}$ .

Figure 4. Top trace: voltage V<sub>TT</sub> (AC coupled). Bottom trace: 2.5V V<sub>DDQ</sub> (AC coupled).

It has been shown that the MAX1957 can be used as the controller for synchronous buck converter to provide termination voltage  $V_{TT}$  for DDR\_SDRAM systems. For applications requiring higher current, the drive circuit of the MAX1957 is capable of driving large external power MOSFETs for output current up to 20A.

| Related Parts |                                                             |              |

|---------------|-------------------------------------------------------------|--------------|

| MAX1957       | Low-Cost, High-Frequency, Current-Mode PWM Buck Controllers | Free Samples |

**More Information** For Technical Support: http://www.maximintegrated.com/support For Samples: http://www.maximintegrated.com/samples Other Questions and Comments: http://www.maximintegrated.com/contact

Application Note 1775: http://www.maximintegrated.com/an1775 APPLICATION NOTE 1775, AN1775, AN 1775, APP1775, Appnote1775, Appnote 1775 Copyright © by Maxim Integrated Products Additional Legal Notices: http://www.maximintegrated.com/legal