Maxim > Design Support > Technical Documents > Application Notes > 1-Wire<sup>®</sup> Devices > APP 5507 Maxim > Design Support > Technical Documents > Application Notes > iButton<sup>®</sup> > APP 5507

Keywords: 1-Wire, bus master, VHDL, verilog, ASIC, FPGA

**APPLICATION NOTE 5507**

# Understanding the DS1WM Synthesizable 1-Wire Bus Master

By: Bernhard Linke, Principal Member Technical Staff Oct 17, 2012

Abstract: Communication with 1-Wire<sup>®</sup> slave devices requires a 1-Wire master. There are numerous ways to build a 1-Wire master (see reference design 4206, "Choosing the Right 1-Wire Master for Embedded Applications"). This document describes the DS1WM, a synthesizable 1-Wire master that can be implemented in an application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA). The free DS1WM IP is available by request.

## Introduction

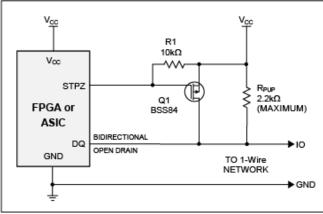

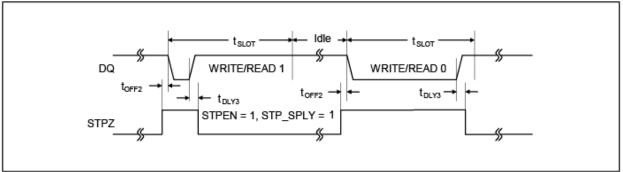

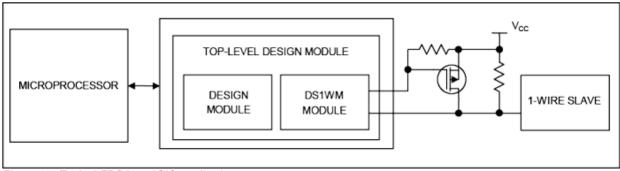

With the growing popularity and diversity of 1-Wire devices, more engineers are facing the task of how to integrate a 1-Wire master into their systems. Reference design 4206, "Choosing the Right 1-Wire Master for Embedded Applications," describes various options. This document focuses on the DS1WM synthesizable 1-Wire bus master that can be implemented as a function block of an application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA). The DS1WM core uses little chip area (~3470 gates plus two bond pads). It also generates the entire 1-Wire timing by hardware, reducing the initial software development time and cost. Thus the entire application software can be written in high-level language. Besides the 1-Wire communication signal DQ, the DS1WM also provides a control signal STPZ, which assists in meeting the power requirements of certain 1-Wire slaves and allows for large networks with many slaves or extensive cabling. **Figure 1** shows the typical DS1WM application circuit. The DS1WM is available for free in both Verilog and VHDL formats.

Figure 1. The DS1WM typical application circuit.

# Description

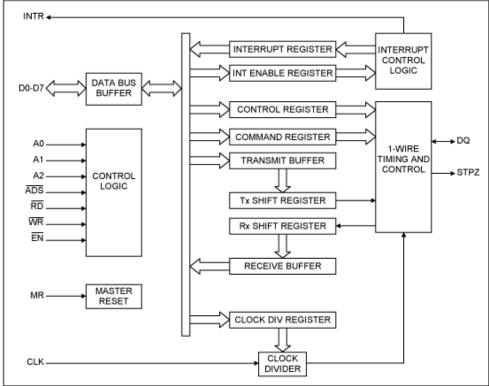

Similar to a memory device, the DS1WM connects to the user's system through an 8-bit data bus, using 3 address

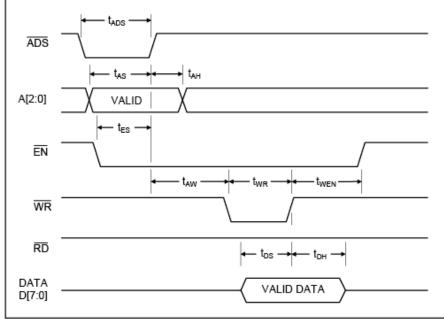

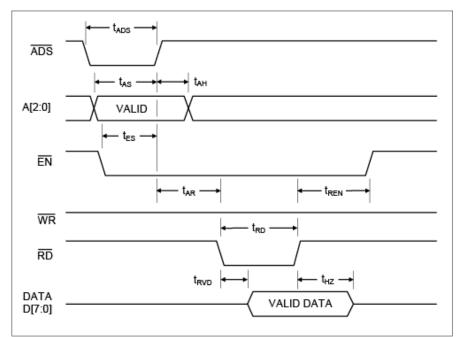

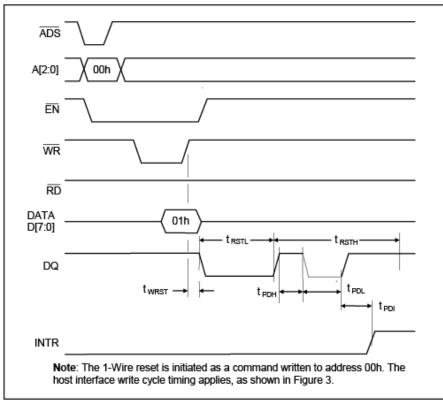

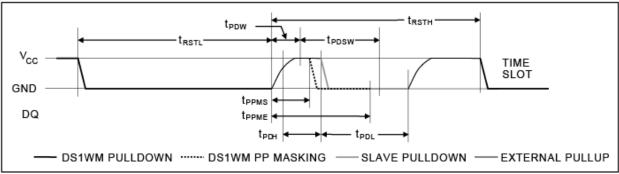

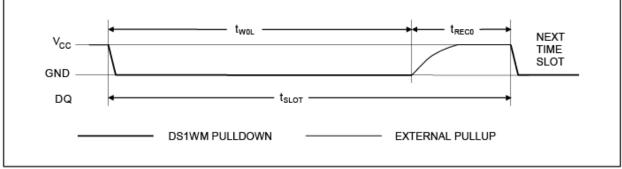

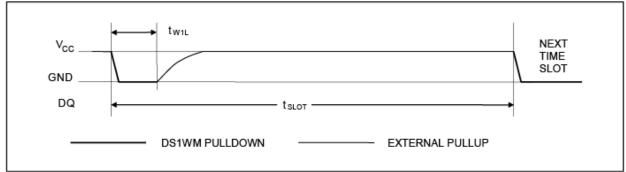

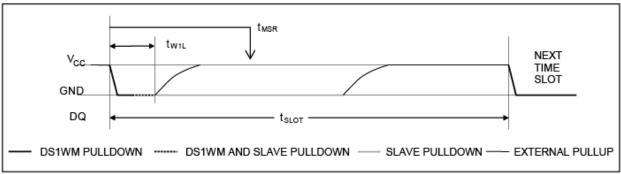

lines and the usual control signals (**Figure 2**). An internal divider chain converts any suitable system clock to a 1MHz signal, which in turn controls the 1-Wire timing. The DS1WM supports standard and overdrive 1-Wire communication in single-bit or byte mode, as well as modified timing for long line applications. The host interface and 1-Wire port signals are described in **Table 1**. **Figures 3** to **5** and **Table 2** specify the host interface waveforms and timing.

Figure 2. The DS1WM block diagram.

| Table 1. Sig       | Table 1. Signal Descriptions |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name               | Туре                         | Function                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| MR                 | I                            | Master reset. Causes the DS1WM to perform an internal reset with the same result as a power-on reset. MR is not gated by active-low EN. The signal is recognized as active by any rising edge on the pin (no minimum duration requirement).                                                                                                                                               |  |  |  |  |  |

| CLK                | I                            | System clock signal. The clock-divider block converts this signal into a ~1.0MHz clock, which in turn controls the 1-Wire timing. The duty cycle should be approximately 50%. See the Clock Divisor Register description for the logically permissible CLK frequencies. The physically permissible upper limit depends on the characteristics of the ASIC/FPGA chosen for implementation. |  |  |  |  |  |

| A[2:0]             | I                            | Address lines of the host interface to access the various memory-mapped device registers. See the Memory Map for register addresses.                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Active-<br>Low ADS | I                            | Active-low address strobe of the host interface. The state of the address lines A[2:0] is copied to an internal latch on the rising edge of the address strobe. See the Host Interface Timing diagrams (Figures 3, 4, and 5) for details.                                                                                                                                                 |  |  |  |  |  |

| Active-<br>Low EN  | I                            | Active-low general enable signal of the host interface. See the Host Interface Timing diagrams (Figures 3, 4, and 5) for details.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| D[7:0]             | I/O                          | Bidirectional data bus of the host interface, three-stated. The DS1WM drives these signals during the host read cycle (Figure 3). At all other times, these signals are in a                                                                                                                                                                                                              |  |  |  |  |  |

|                   |     | high impedance state, allowing the host to communicate with other devices on the data bus.                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active-<br>Low WR | I   | Active-low write enable signal of the host interface. The state of the data bus D[7:0] is copied to the addressed register on the rising edge of the active-low WR signal. active-low WR should be inactive (high) unless the host wants to write to the DS1WM. See the Host Interface Timing diagrams (Figures 3 and 5) for details. If both active-low RD and active-low WR are active at the same time, active-low WR dominates.                                     |

| Active-<br>Low RD | I   | Active-low read enable signal of the host interface. When active, the DS1WM puts the contents of the selected register on the data bus for the host to read. Active-low RD should be inactive (high) unless the host wants to read from the DS1WM. See the Host Interface Timing diagram (Figure 4) for details. If both active-low RD and active-low WR are active at the same time, active-low WR dominates.                                                          |

| DQ                | I/O | IO driver for the 1-Wire bus. This is an open-drain bidirectional port, which requires a pullup resistor to $V_{CC}$ . For the permissible pullup resistor range, refer to the data sheet of the 1-Wire slaves in the application. The minimum value also depends on the drive characteristics and logic thresholds of the ASIC/FPGA chosen for implementation.                                                                                                         |

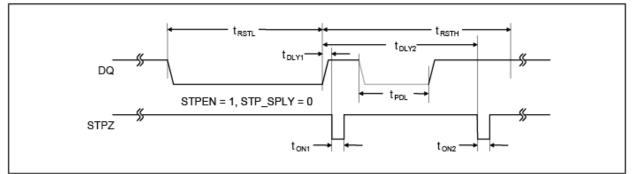

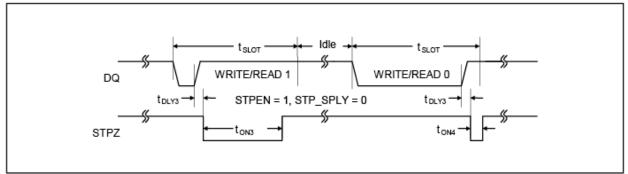

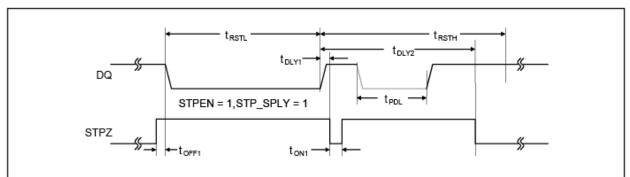

| STPZ              | 0   | Active-low control signal for an external P-channel transistor to bypass the pullup resistor at certain times. See the Control Register description, bits STPEN and STP_SPLY, and the STPZ timing diagrams (Figures 10 to 13) for details.                                                                                                                                                                                                                              |

| INTR              | 0   | Interrupt signal of the host interface. The power-on default polarity is active low, but can<br>be changed to active high through the IAS bit in the Interrupt Enable Register. The<br>INTR signal is inactive unless interrupts are enabled through the Interrupt Enable<br>Register and a qualifying interrupt condition exists. For details see the Interrupt Register<br>description. Reading the Interrupt Register changes the INTR signal to its inactive state. |

Figure 3. Host interface write cycle.

Figure 4. Host interface read cycle.

Figure 5. Host interface timing, issuing a 1-Wire Reset.

| Table 2. Host Interface Timing Specifications |           |            |     |     |       |

|-----------------------------------------------|-----------|------------|-----|-----|-------|

| Symbol                                        | Parameter | Conditions | Min | Max | Units |

| t <sub>ADS</sub> | Address strobe width      | Notes 1, 2 | 60  |     | ns |

|------------------|---------------------------|------------|-----|-----|----|

| t <sub>AH</sub>  | Address hold time         | Notes 1, 2 | 0   |     | ns |

| t <sub>AR</sub>  | Address latch to read     | Notes 1, 2 | 60  |     | ns |

| t <sub>AS</sub>  | Address setup time        | Notes 1, 2 | 60  |     | ns |

| tAW              | Address latch to write    | Notes 1, 2 | 60  |     | ns |

| t <sub>DH</sub>  | Data hold time            | Note 1     | 30  |     | ns |

| t <sub>DS</sub>  | Data setup time           | Note 1     | 30  |     | ns |

| t <sub>ES</sub>  | Enable setup time         | Note 1     | 60  |     | ns |

| t <sub>HZ</sub>  | RD to floating data delay | Note 1     | 0   | 100 | ns |

| t <sub>PDI</sub> | Presence detect to INTR   | Note 1     | 0   | 100 | ns |

| t <sub>RD</sub>  | RD strobe width           | Note 1     | 125 |     | ns |

| t <sub>REN</sub> | Enable hold time from RD  | Note 1     | 20  |     | ns |

| t <sub>RVD</sub> | Delay from RD to data     | Note 1     |     | 60  | ns |

| t <sub>WEN</sub> | Enable hold time from WR  | Note 1     | 20  |     | ns |

| t <sub>WR</sub>  | WR strobe width           | Note 1     | 100 |     | ns |

| tWRST            | WR high to reset          | Note 1     | 0   | 100 | ns |

Note 1: These values depend on the process used to realize the DS1WM. Values shown are for example purposes only.

Note 2: If active-low ADS is tied low,  $t_{AR}$  and  $t_{AW}$  are measured from  $t_{ES}$ . In this case, the falling edge of active-low RD or active-low WR must occur at least  $t_{ES} + t_{AR}$  or  $t_{ES} + t_{AW}$  after the falling edge of active-low EN.

The host processor communicates with the DS1WM through 6 registers, which are accessed through 3 address lines A[2:0]. **Table 3** shows the memory map.

| Table 3. Memory Map |    |    |    |            |                           |  |  |

|---------------------|----|----|----|------------|---------------------------|--|--|

| Address             | A2 | A1 | A0 | Access     | Description               |  |  |

| 00h                 | 0  | 0  | 0  | Write/read | Command Register          |  |  |

| 01h                 | 0  | 0  | 1  | Write/read | Transmit/Receive Buffer   |  |  |

| 02h                 | 0  | 1  | 0  | Read       | Interrupt Register        |  |  |

| 03h                 | 0  | 1  | 1  | Write/read | Interrupt Enable Register |  |  |

| 04h                 | 1  | 0  | 0  | Write/read | Clock Divisor Register    |  |  |

| 05h                 | 1  | 0  | 1  | Write/read | Control Register          |  |  |

# **Register Descriptions**

### **Command Register**

This register is accessed to generate a 1-Wire reset/presence-detect cycle and to activate or deactivate the Search ROM accelerator. In addition to these two functions, the Command Register contains 2 bits to control the DQ pin

directly.

| Command Register Bitmap |    |    |    |    |       |     |     |     |

|-------------------------|----|----|----|----|-------|-----|-----|-----|

| ADDR                    | b7 | b6 | b5 | b4 | b3    | b2  | b1  | b0  |

| 00h                     | Х  | Х  | Х  | Х  | OW_IN | FOW | SRA | 1WR |

This register is read/write. The power-on default is 08h (OW\_IN = 1). Bits 4 to 7 have no function; they always read 0 and cannot be set to 1.

| Bit<br>Description                        | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>OW_IN</b> : DQ<br>Input (Read<br>only) | Purpose:       Reading the logic state of the DQ pin. Sampling takes place on every falling edge of the CLK signal.         Code:       1: The voltage at DQ is above V <sub>IHMIN</sub> (default).         0: The voltage at DQ is below V <sub>ILMAX</sub> .         Conditions:       This function is always enabled. OW_IN changes to 1 upon power-on reset or a master reset (MR pin).         Usage:       In conjunction with FOW to perform 1-Wire communication beyond the 1-Wire Reset and 1-Wire Read/Write functions.                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>FOW</b> : Force<br>1-Wire              | <ul> <li>Purpose: Directly driving the DQ pin under host timing control.</li> <li>Code: 1: Activates DQ pulldown         <ul> <li>Ends DQ pulldown (default)</li> </ul> </li> <li>Conditions: This function must be enabled by first writing the EN_FOW bit in the Control Register (address 05h) to 1. Otherwise, FOW has no effect. If both EN_FOW and FOW are 1, the 1-Wire Reset and the 1-Wire Transmit/Receive function (address 01h) have no effect. FOW returns to 0 upon power-on reset or master reset (MR pin). Changing EN_FLOW to 0 has the same effect as writing FOW to 0.</li> <li>Usage: Generating DQ signaling beyond the 1-Wire Reset and 1-Wire Read/Write functions. To read from the 1-Wire bus, change FOW to 0, then wait as needed and read the OW_IN bit. As a safety precaution, if FOW is written to 1 while the STPZ signal is active (low), the STPZ signal immediately changes to inactive (high).</li> </ul> |

| SRA:<br>Search<br>ROM<br>Accelerator      | Purpose:       Activating the search ROM accelerator.         Code:       1: The search ROM accelerator is activated.         0: The search ROM accelerator is not activated (default).         Conditions:       This function is always enabled. SRA returns to 0 upon a power-on reset, a master reset (MR pin), or when written to 0.         Usage:       The search ROM accelerator saves time when executing the 1-Wire Search algorithm. See the Search Accelerator Operation section for more information.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>1WR</b> : 1-<br>Wire Reset             | Purpose:       Generating a reset/presence detect sequence on the 1-Wire bus.         Code:       1: A reset/presence detect cycle is in progress.<br>0: The reset/presence detect cycle is completed (default).         Conditions:       This function is always enabled. 1WR returns to 0 upon a power-on reset, a master reset (MR pin) or the completion of the 1-Wire reset/presence detect cycle. A 1-Wire reset/presence-detect cycle can be aborted by writing this bit to 0.         Usage:       Writing this bit to 1 starts a 1-Wire reset/presence detect cycle and affects the PD and PDR bits in the Interrupt Register (address 02h).                                                                                                                                                                                                                                                                                        |

### Transmit/Receive Buffer

This is the location to which the host processor writes a data byte to be transmitted on the 1-Wire bus. If the 1-Wire slave is in a state to respond with data, the host writes a byte FFh to this register and then, after the byte is transmitted, reads this register again to retrieve that data sent by the 1-Wire slave.

| Transmit | Transmit/Receive Buffer Bitmap |       |       |       |       |       |       |       |

|----------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|

| ADDR     | b7                             | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

| 01h      | Data7                          | Data6 | Data5 | Data4 | Data3 | Data2 | Data1 | Data0 |

This register is read/write. The power-on default is 00h.

| Bit Description                        | Definition  |                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | Purpose:    | Providing data for transmission on the 1-Wire bus; accessing data received from 1-Wire bus.                                                                                                                                                                                                       |

|                                        | Code:       | N/A                                                                                                                                                                                                                                                                                               |

| Data[7:0]:<br>Transmit/Receive<br>Data | Conditions: | 1-Wire communication can be performed in bit mode or in byte mode<br>(default). In bit mode, only Data0 is relevant. Bit mode is selected by writing<br>the BIT_CTL bit in the Control Register (address 05h) to 1. Data[7:0] returns<br>to 00h upon a power-on reset or a master reset (MR pin). |

|                                        | Usage:      | General 1-Wire communication except for 1-Wire reset. The 1-Wire speed is selected by the OD bit in the Control Register (address 05h).                                                                                                                                                           |

### Interrupt Register

This register provides access to flags from current status, transmit, receive, and 1-Wire reset operations. All of these flags can generate an interrupt on the INTR pin if the corresponding enable bit is set in the Interrupt Enable Register. To clear the INTR signal, the Interrupt Register must be read. Reading the Interrupt Register always sets the INTR pin inactive even if not all flags are cleared.

| Interrupt | Interrupt Register Bitmap |          |      |     |      |     |     |    |

|-----------|---------------------------|----------|------|-----|------|-----|-----|----|

| ADDR      | b7                        | b6       | b5   | b4  | b3   | b2  | b1  | b0 |

| 02h       | OW_LOW                    | OW_SHORT | RSRF | RBF | TEMT | TBE | PDR | PD |

This register is read only. The power-on default is 0Eh (TEMT, TBE, PDR = 1, PD = 0).

| Bit<br>Description      | Definition  |                                                                                                                                                                        |

|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Purpose:    | Signaling the arrival of a slave on the 1-Wire bus.                                                                                                                    |

|                         | Code:       | 1: A slave has arrived.                                                                                                                                                |

|                         |             | 0: No slave arrival since the last reading of the Interrupt Register (default).                                                                                        |

| OW_LOW:<br>1-Wire Event | Conditions: | This function is always enabled. OW_LOW returns to 0 upon reading the Interrupt Register, a power-on reset or a master reset (MR pin).                                 |

|                         | Usage:      | A slave arriving on the idle bus (= no communication) generates a spontaneous presence pulse, which sets this bit. A short circuit on the idle bus also sets this bit. |

|                         | Purpose:    | Signaling a short circuit on the 1-Wire bus.                                                                                                                           |

|                         | Code:       | 1: The 1-Wire bus is shorted.                                                                                                                                          |

| OW SHORT:               |             | 0: The 1-Wire bus is in normal operating conditions (default).                                                                                                         |

| 1-Wire<br>Shorted       | Conditions: | This function is always enabled. OW_SHORT returns to 0 upon reading the Interrupt Register, a power-on reset or a master reset (MR pin).                               |

|                                                 | Usage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Prior to generating a 1-Wire reset or time slot, the DS1WM checks whether the 1-Wire bus is idle high. If the bus is low at that time, no communication can take place. This situation is signaled as a short circuit.                                                                                                        |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                 | Purpose:<br>Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Signaling the status of the Receive Shift Register.<br>1: The Receive Shift Register is full.<br>0: The Receive Shift Register is empty or receiving data (default).                                                                                                                                                          |  |  |  |  |

| <b>RSRF</b> :<br>Receive Shift<br>Register Full | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This function is always enabled. RSRF returns to 0 when the Receive Shift<br>Register content is transferred to the Receive Buffer (address 01h) for the host<br>to read, upon power-on reset, or a master reset (MR pin).                                                                                                    |  |  |  |  |

|                                                 | Usage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | When the RSRF gets set and the RBF is not set (i.e., meaning the Receive Shift Register is full and the Receive Buffer flag is clear), the transfer takes place on the rising edge of the internal 1MHz clock.                                                                                                                |  |  |  |  |

|                                                 | Purpose:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signaling the status of the Receive Buffer.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                 | Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1: There is new data in the Receive Buffer.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0: There is no new data in the Receive Buffer (default).                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                 | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This function is always enabled. RBF returns to 0 upon reading the Receive<br>Buffer (address 01h), a power-on reset, or a master reset (MR pin). Reading the<br>Interrupt Register without first having read the Receive Buffer triggers another<br>interrupt if ERBF = 1 & RBF = 1.                                         |  |  |  |  |

|                                                 | Usage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Normal communication with 1-Wire slaves. If not using interrupts, poll the Interrupt Register to detect events. If using the RBF interrupt (ERBF = 1), read the Receive Buffer prior to reading the Interrupt Register.                                                                                                       |  |  |  |  |

| RBF:<br>Receive<br>Buffer Full                  | <ol> <li>Write Fl</li> <li>Wait for</li> <li>When th</li> <li>Clear E</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>The process to use the RBF flag looks like this:</li><li>1. Write FF to the TX buffer and enable the TBE flag.</li><li>2. Wait for the interrupt pin to trigger.</li><li>3. When the interrupt occurs, read the interrupt register and confirm TBE set.</li><li>4. Clear ETBE bit and now set the ETMT bit.</li></ul> |  |  |  |  |

|                                                 | <ol> <li>When the first of the first of</li></ol> | the interrupt pin to trigger.<br>ne interrupt occurs, read the interrupt register and confirm ETMT set.<br>ne ETMT bit and now set the ERBF bit.<br>the interrupt pin to trigger.                                                                                                                                             |  |  |  |  |

|                                                 | 9. When the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ne interrupt occurs, read the interrupt register and confirm RBF set.                                                                                                                                                                                                                                                         |  |  |  |  |

|                                                 | <ol> <li>Read the RX Buffer.</li> <li>Clear the ERBF after reading the RX Buffer.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                                 | Purpose:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signaling the status of the Transmit Shift Register.                                                                                                                                                                                                                                                                          |  |  |  |  |

| TENAT                                           | Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1: The Transmit Shift Register is empty, ready for new data (default).                                                                                                                                                                                                                                                        |  |  |  |  |

| <b>TEMT</b> :<br>Transmit                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0: The Transmit Shift Register is busy sending data.                                                                                                                                                                                                                                                                          |  |  |  |  |

| Shift Register<br>Empty                         | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This function is always enabled. TEMT returns to 0 when the Transmit Buffer content (address 01h) is transferred to the Transmit Shift Register. TEMT changes to 1 upon power-on reset or a master reset (MR pin).                                                                                                            |  |  |  |  |

|                                                 | Usage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The transfer takes place on the internal 1MHz clock as soon as the TBE is set.                                                                                                                                                                                                                                                |  |  |  |  |

|                                                 | Purpose:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signaling the status of the Transmit Buffer.                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                                 | Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1: The Transmit Buffer is empty, ready for new data (default).                                                                                                                                                                                                                                                                |  |  |  |  |

| <b>TBE</b> :<br>Transmit                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0: The Transmit Buffer is waiting for the Transmit Shift Register to finish sending data.                                                                                                                                                                                                                                     |  |  |  |  |