### NJU77580/NJU77582

# 20MHz, Low noise, Excellent EMI Immunity, Rail-to-rail I/O, Operational Amplifiers

#### **FEATURES**

$(V^+ = 5V, Typical value)$

Wide Gain Bandwidth

20MHz

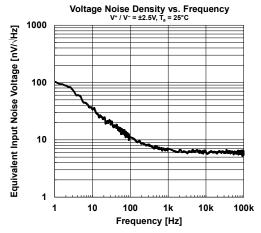

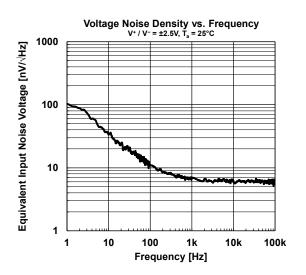

• Low Noise  $6nV/\sqrt{Hz}$  (f = 10kHz)

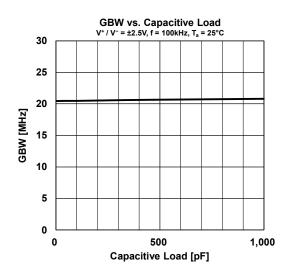

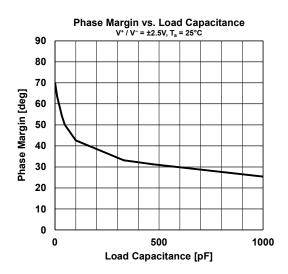

■ Enhanced C-Drive TM

- 1000pF High Capacitive Load Drive

- Maintains GBW 20MHz under High Capacitive

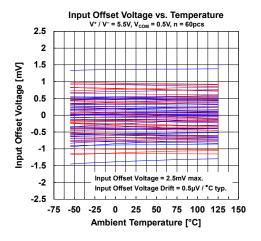

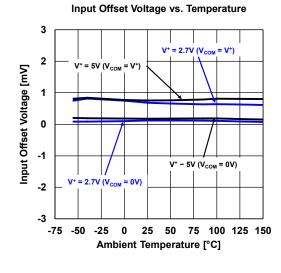

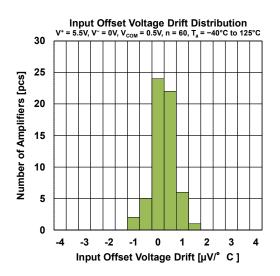

Input Offset Voltage Drift 0.5µV/°C

Integrated EMI filter EMIRR = 64dB (f = 1.8GHz)

Input Tolerant

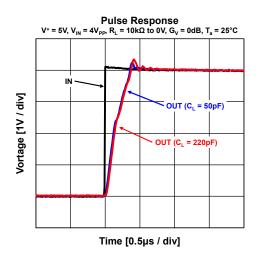

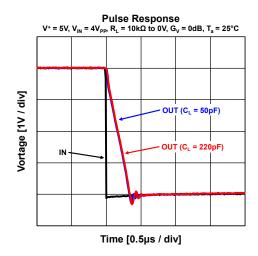

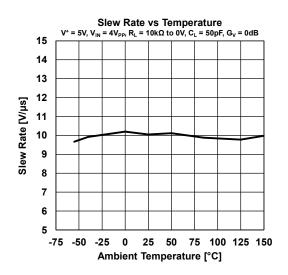

High Slew Rate 10V/µs

Rail-to-Rail Input and Output

Unity-Gain stable

Supply Voltage

2.7V to 5.5V

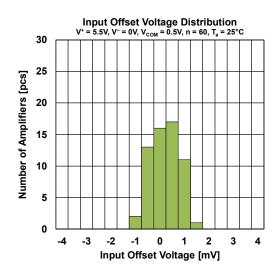

■ Input Offset Voltage 2.5mV max.

Supply Current

2.3mA / ch

Packages SOT-23-5 SOP8, MSOP8 (VSP8)

SOP8, MSOP8 (VSP8) DFN8-U1 (ESON8-U1)

#### **APPLICATIONS**

- Sensor Signal Conditioning

- High-Speed Cable Drivers

- Multi-Pole Active Filters

- Security

- Scanners

- Photodiode Amplifier

- ADC front ends

#### DESCRIPTION

The NJU77580/NJU77582 are single and dual rail-to-rail input and output single supply OpAmp featuring wide bandwidth and low noise. The combination of very low noise ( $6nV\sqrt{Hz}$  at 10kHz), high-gain bandwidth (20MHz), and fast slew rate ( $10V/\mu s$ ) make the devices ideal for a wide variety of applications, including signal conditioning and sensor amplification requiring high gains.

Low input bias current, low noise and low offset voltage drift of  $0.5\mu V/^{\circ}C$  performances are also excellent for filters, integrators, photodiode amplifiers, and high impedance sensors. The ability of rail-to-rail input and output enables the designers to buffer ADC, DAC, and other wide output swing devices in single-supply systems.

The Enhanced C-Drive TM of NJU77580/NJU77582 can directly drive a 1000pF capacitive load, and can output an AC signal with little distortion even with a large capacitive load by suppressing the decrease in GBW. This feature is ideal for high-speed signal cable drivers and high-speed active filter circuits that are sensitive to wiring capacitance.

NJU77580/NJU77582 includes integrated EMI filter to reduce malfunctions caused by  $R_{\textrm{F}}$  noises from mobile phones and other wireless devices. And the input tolerant that allows the input voltage (Recommended: V'+5.5V) that exceed positive supply voltage is ideal for design for robust industrial applications.

NJU77580/NJU77582 operates from supply range of 2.7V to 5.5V over the -55°C to 125°C extended industrial temperature range. The NJU77580 is available in 5-pin SOT-23-5 package. The NJU77582 is available in 8-pin SOP8, MSOP (VSP): meet JEDEC MO-187-DA type package, and DFN that is thin and 2mm square small package.

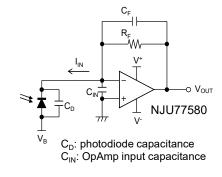

#### **■ TYPICAL APPLICATION**

Transimpedance amplifier

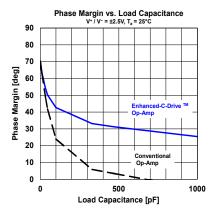

#### 1000pF Capacitive Load Drive

#### **■ PRODUCT NAME INFORMATION**

NJU7758X aaa (bbb)

#### Description of configuration

| Suffix | Parameter    | Description                                            |

|--------|--------------|--------------------------------------------------------|

| aaa    | Package code | Indicates the package. Refer to the order information. |

| bbb    | Packing      | Refer to the packing specifications.                   |

#### ■ ORDER INFORMATION

| Product Name      | Package               | RoHS | Halogen-<br>Free | Terminal<br>Finish | Marking | Weight (mg) | MOQ<br>(pcs) |

|-------------------|-----------------------|------|------------------|--------------------|---------|-------------|--------------|

| NJU77580F (TE1)   | SOT-23-5              | Yes  | Yes              | Sn2Bi              | N/A     | 15          | 3000         |

| NJU77582G (TE2)   | SOP8                  | Yes  | Yes              | Pure Sn            | 77582   | 88          | 2500         |

| NJU77582R (TE1)   | MSOP8 (VSP8)          | Yes  | Yes              | Sn2Bi              | 77582   | 21          | 2000         |

| NJU77582KU1 (TE3) | DFN8-U1<br>(ESON8-U1) | Yes  | Yes              | Sn2Bi              | 77582   | 5.3         | 3000         |

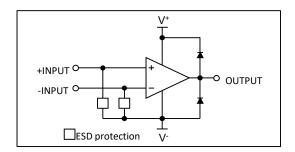

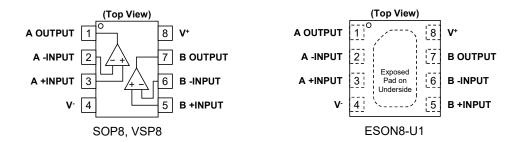

#### **■ BLOCK DIAGRAM**

- 3 -

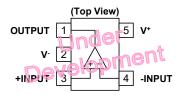

#### ■ PIN DESCRIPTIONS (5 Pin)

| Pin No.<br>SOT-23-5 | SYMBOL   | I/O | DESCRIPTION                               |

|---------------------|----------|-----|-------------------------------------------|

| Under               | A OUTPUT | 0   | Output channel                            |

| Development         | A -NPUT  | I   | Inverting input channel                   |

| 2                   | A +NPUT  |     | Non-inverting input channel               |

| 5                   | V+       | ı   | Positive supply                           |

| 2                   | V-       | -   | Negative supply or Ground (single supply) |

#### ■ PIN DESCRIPTIONS (8 Pin)

|      | Pin No. |          | SYMBOL I/O |     | DESCRIPTION                               |  |

|------|---------|----------|------------|-----|-------------------------------------------|--|

| SOP8 | VSP8    | ESON8-U1 | STIVIDUL   | 1/0 |                                           |  |

| 1    | 1       | 1        | A OUTPUT   | 0   | Output channel A                          |  |

| 2    | 2       | 2        | A -NPUT    | I   | Inverting input channel A                 |  |

| 3    | 3       | 3        | A +NPUT    | I   | Non-inverting input channel A             |  |

| 7    | 7       | 7        | BOUTPUT    | 0   | Output channel B                          |  |

| 6    | 6       | 6        | B -INPUT   | I   | Inverting input channel B                 |  |

| 5    | 5       | 5        | B +INPUT   | I   | Non-inverting input channel B             |  |

| 8    | 8       | 8        | V+         | -   | Positive supply                           |  |

| 4    | 4       | 4        | V-         | -   | Negative supply or Ground (single supply) |  |

<sup>\*</sup>Connect to exposed pad to V-

Ver.1.2

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                        | Symbol           | Rating                                       | Unit |

|----------------------------------|------------------|----------------------------------------------|------|

| Supply Voltage                   | V+ - V-          | 7                                            | V    |

| Input Voltage *1                 | Vin              | V <sup>-</sup> - 0.3 to V <sup>-</sup> + 7   | V    |

| Input Current *1                 | I <sub>IN</sub>  | -10                                          | mA   |

| Output Terminal Input Voltage *2 | Vo               | V <sup>-</sup> - 0.3 to V <sup>+</sup> + 0.3 | V    |

| Differential Input Voltage *3    | V <sub>ID</sub>  | ±7                                           | V    |

| Output Short-Circuit Duration *4 |                  | Continuous                                   |      |

| Storage Temperature              | T <sub>stg</sub> | −65 to 150                                   | °C   |

| Junction Temperature *5          | Tj               | 150                                          | °C   |

<sup>\*</sup>¹ Input voltages outside the supply voltage will be clamped by ESD protection diodes. If the input voltage exceeds the supply voltage, the current must be limited 10mA or less by μsing a restriction resistance. Input current outflow is negative.

Please refer to "Thermal characteristics" for the thermal resistance under our measurement board conditions.

#### **ABSOLUTE MAXIMUM RATINGS**

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the lifetime and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings is not assured.

#### **■ THERMAL CHARACTERISTICS**

| Dookogo                                                            | Measurement Result       |                                          |      |  |

|--------------------------------------------------------------------|--------------------------|------------------------------------------|------|--|

| Package                                                            | Thermal Resistance (Θja) | Thermal Characterization Parameter (ψjt) | Unit |  |

| SOT-23-5 *1<br>SOP8 *1<br>MSOP8 (VSP8) *1<br>DFN8-U1 (ESON8-U1) *2 | 192<br>125<br>189<br>104 | 58<br>43<br>53<br>25                     | °C/W |  |

qja:Junction-to-Ambient Thermal Resistance

ψjt:Junction-to-Top Thermal Characterization Parameter

(Applying 99.5 mm × 99.5 mm inner Cu area and a thermal via hole to a board based on JEDEC standard JESD51-5.)

<sup>\*2</sup> The output terminal input voltage is limited at 7V.

<sup>\*3</sup> Differential voltage is the voltage difference between +INPUT and -INPUT.

<sup>\*4</sup> Short-circuit can cause excessive heating and destructive dissipation.

<sup>\*&</sup>lt;sup>5</sup> Calculate the power consumption of the IC from the operating conditions, and calculate the junction temperature with the thermal resistance.

<sup>\*1</sup> Mounted on glass epoxy board (76.2 mm × 114.3 mm × 1.6 mm: based on EIA/JEDEC standard, 4-layer FR-4), internal Cu area: 74.2 mm × 74.2 mm.

<sup>\*2</sup> Mounted on glass epoxy board (101.5 mm × 114.5 mm × 1.6 mm: based on EIA/JEDEC standard, 4-layer FR-4) with exposed pad

#### ■ ELECTROSTATIC DISCHARGE (ESD) PROTECTION VOLTAGE

| Parameter | Conditions             | Protection Voltage |

|-----------|------------------------|--------------------|

| НВМ       | C = 100 pF, R = 1.5 kΩ | ±1000 V            |

| CDM       | Direct CDM             | ±1000 V            |

#### **ELECTROSTATIC DISCHARGE RATINGS**

The electrostatic discharge test is done based on JEITA ED-4701.

In the HBM method, ESD is applied using the power supply pin and GND pin as reference pins.

#### **■ RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol  | Conditions  | Rating                                       | Unit |

|-----------------------|---------|-------------|----------------------------------------------|------|

| Supply Voltage        | V+ - V- |             | 2.7 to 5.5                                   | V    |

| Input Voltage         | VIN     | Closed-loop | V <sup>-</sup> - 0.3 to V <sup>-</sup> + 5.5 | V    |

| Operating Temperature | Ta      |             | -55 to 125                                   | °C   |

#### RECOMMENDED OPERATING CONDITIONS

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if when they are used over such conditions by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

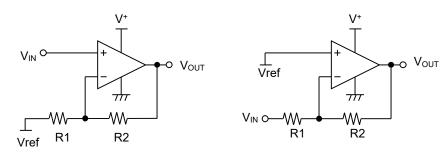

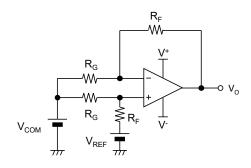

#### **■ TYPICAL APPLICATION CIRCUIT**

Non-inverting amplifier

Inverting amplifier

#### **■ ELECTRICAL CHARACTERISTICS**

$V^+ = 2.7V$  to 5.5V,  $V^- = 0V$ ,  $R_L = 10k\Omega$  to  $V^+/2$ ,  $T_a = 25$ °C, unless otherwise specified.

| Parameter                         | Symbol                   | t/2, T <sub>a</sub> = 25°C, unless otherwise spe-                               | Min                  | Тур                    | Max                    | Unit             |

|-----------------------------------|--------------------------|---------------------------------------------------------------------------------|----------------------|------------------------|------------------------|------------------|

| INPUT CHARACTERISTICS *1          |                          |                                                                                 |                      | 71                     |                        |                  |

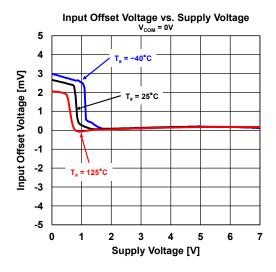

| Input Offset Voltage              | Vio                      | V <sub>COM</sub> = V <sup>-</sup>                                               | _                    | 0.5                    | 2.5                    | mV               |

| Input Bias Current                | I <sub>B</sub>           |                                                                                 | -                    | 1                      | -                      | pА               |

| Input Offset Current              | lio                      |                                                                                 | -                    | 1                      | -                      | pА               |

| Input Offset Voltage Drift        | ΔV <sub>IO</sub> /Δ<br>Τ | V <sub>COM</sub> = 0V                                                           | -                    | 0.5                    | -                      | μV/°C            |

| Input Resistance                  | R <sub>IC</sub>          |                                                                                 | -                    | 70                     | -                      | GΩ               |

| Input Capacitance                 | Cin                      |                                                                                 | -                    | 5                      | -                      | pF               |

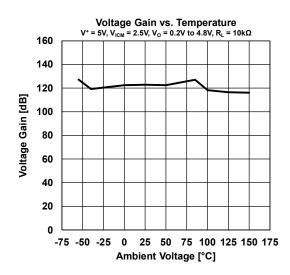

| Open-Loop Voltage Gain            | Av                       | $V^{+} = 5.5V$ , $R_{L} = 10k\Omega$ , $V_{O} = V^{-} - 0.3V$ to $V^{+} - 0.3V$ | 80                   | 100                    | -                      | dB               |

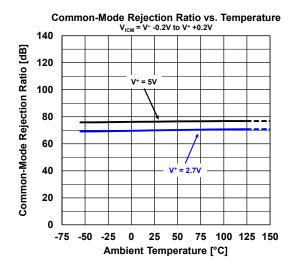

| Common-Mode Rejection Ratio       | CMR                      | $V^{+} = 5.5V,$<br>$V_{COM} = V^{-} - 0.2V$ to $V^{+} - 2V$                     | 70                   | 90                     | -                      | dB               |

| ·                                 |                          | $V^+ = 5.5V$ ,<br>$V_{COM} = V^ 0.2V$ to $V^+ + 0.2V^{*2}$                      | 60                   | 80                     | -                      | dB               |

| Common-Mode Input Voltage Range   | V <sub>ICM</sub>         | Guaranteed by CMR                                                               | V <sup>-</sup> - 0.2 | -                      | V <sup>+</sup> + 0.2   | V                |

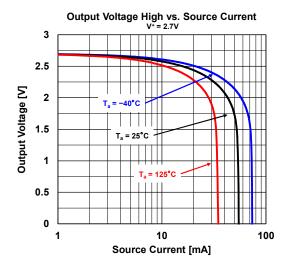

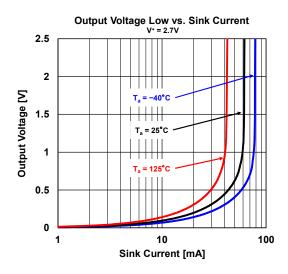

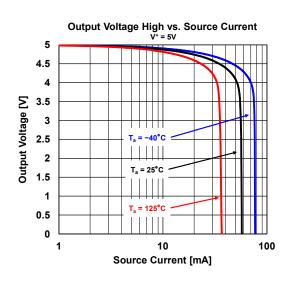

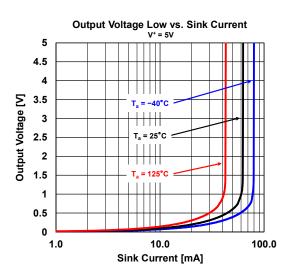

| OUTPUT CHARACTERISTICS            |                          |                                                                                 |                      |                        |                        |                  |

| High-level Output Voltage         | Van                      | $V^{+} = 5.5V$ , $R_{L} = 10k\Omega$ to $V^{+} / 2$                             | -                    | V <sup>+</sup> - 0.005 | V <sup>+</sup> - 0.050 | V                |

| High-level Output Voltage         | Vон                      | $V^{+} = 2.7V$ , $R_{L} = 10k\Omega$ to $V^{+} / 2$                             | -                    | V <sup>+</sup> - 0.002 | V <sup>+</sup> - 0.050 | V                |

| Low-level Output Voltage          | Vol                      | $V^{+} = 5.5V$ , $R_{L} = 10k\Omega$ to $V^{+} / 2$                             | -                    | 7                      | 50                     | mV               |

| Low-level Output Voltage          | VOL                      | $V^{+} = 2.7V$ , $R_{L} = 10k\Omega$ to $V^{+} / 2$                             | -                    | 2                      | 50                     | mV               |

| Capacitive Load Drive             | CL                       | Ф <sub>м</sub> = 45deg                                                          | -                    | 50                     | -                      | pF               |

| Output Impedance                  | Zo                       | V <sup>+</sup> = 5V, f = 1MHz                                                   | -                    | 90                     | -                      | Ω                |

| Output Short-Circuit Current      | Isc                      | V <sup>+</sup> = 5V, Source / Sink                                              | -                    | 50 / 50                | -                      | mA               |

| POWER SUPPLY                      |                          |                                                                                 |                      |                        |                        |                  |

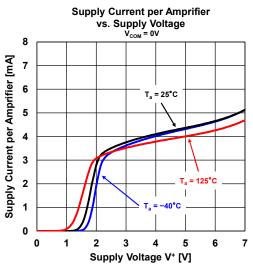

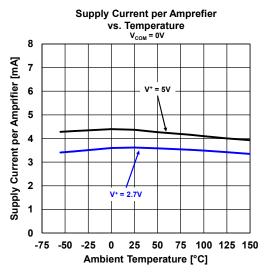

| Supply Current per Amplifier      | ISUPPLY                  | $V^{+} = 5V, V_{COM} = 0V, V^{+}$                                               | -                    | 2.3                    | 3.8                    | mA               |

|                                   | ISUPPLY                  | $V^{+} = 2.7V, V_{COM} = 0V, V^{+}$                                             | -                    | 2.0                    | 3.5                    | mA               |

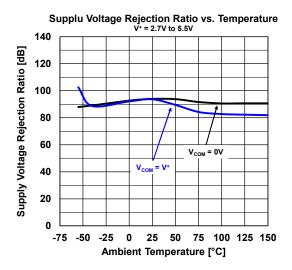

| Supply Voltage Rejection Ratio    | SVR                      | $V^+ = 2.7 \text{ to } 5.5 \text{V}, V_{\text{COM}} = 0 \text{V}, V^+$          | 70                   | 90                     | -                      | dB               |

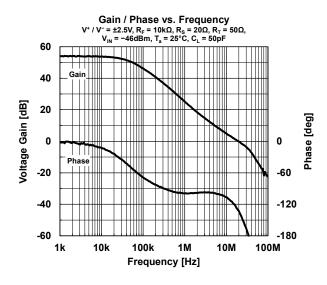

| AC CHARACTERISTICS (V+ = 5V)      | V <sub>COM</sub> = V     | ( / 2)                                                                          | 1                    | 1                      | 1                      | T                |

| Slew Rate                         | SR                       | C <sub>L</sub> = 50pF, V <sub>IN</sub> = 4V <sub>PP</sub> , Gain = 1            | -                    | 10                     | -                      | V/µs             |

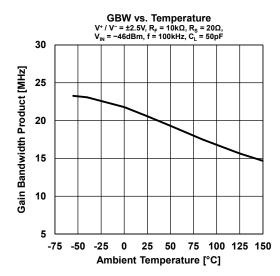

| Gain Bandwidth Product            | GBW                      | C <sub>L</sub> = 50pF                                                           | -                    | 20                     | -                      | MHz              |

| Settling Time 0.1%                | ts                       | $C_L = 50 pF, V_{IN} = 4 V_{PP}, Gain = 1$                                      | -                    | 0.7                    | -                      | μs               |

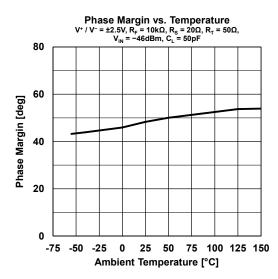

| Phase Margin                      | Фм                       | C <sub>L</sub> = 10pF                                                           | -                    | 60                     | -                      | Deg              |

| - Hade Margin                     | ∓ IVI                    | C <sub>L</sub> = 50pF                                                           | -                    | 45                     | -                      | Deg              |

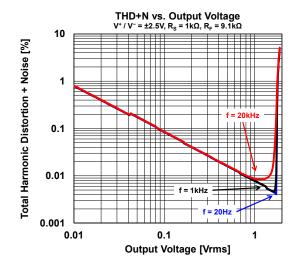

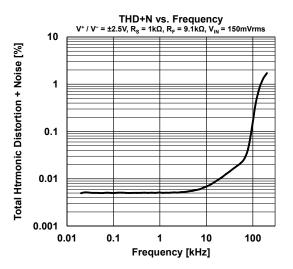

| Total Harmonic Distortion + Noise | THD+N                    | f = 1kHz, V <sub>0</sub> = 1.5Vrms                                              | -                    | 0.005                  | -                      | %                |

|                                   | V <sub>NI</sub>          | f = 0.1Hz to 10Hz                                                               | -                    | 1.4                    | -                      | μV <sub>PP</sub> |

| Equivalent Input Noise Voltage    | en                       | f = 1kHz                                                                        | -                    | 7                      | -                      | nV/√Hz           |

|                                   |                          | f = 10kHz                                                                       | -                    | 6                      | -                      | nV/√Hz           |

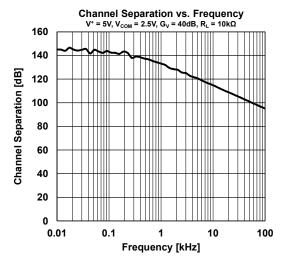

| Channel Separation                | CS                       | NJU77582, f = 1kHz                                                              | -                    | 120                    | -                      | dB               |

<sup>&</sup>lt;sup>\*1</sup> Input offset voltage and drift, Input bias and offset current are positive or negative, its absolute values are listed in electrical characteristics.

$<sup>^{*2}</sup>$  V<sup>+</sup> + 0.2V value is limited at 5.5V.

#### **Single and Dual Supply Voltage Operation**

The NJU7758x series works with both single supply and dual supply when the voltage supplied is between V<sup>+</sup> and V<sup>-</sup>. These amplifiers operate from single 2.7V to 5.5V supply and dual  $\pm 1.35V$  to  $\pm 2.75V$  supply. The power supply pin should have bypass capacitor (i.e.  $0.1\mu F$ ).

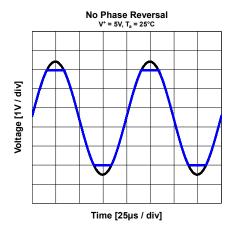

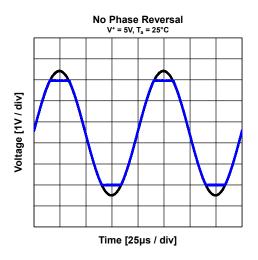

#### No Phase Reversal

The NJU7758x series are designed to prevent phase reversal at the input voltage above the supply voltage. Figure1 shows no phase reversal characteristics with the input voltage exceeding the supply voltage.

Figure 1. No phase reversal

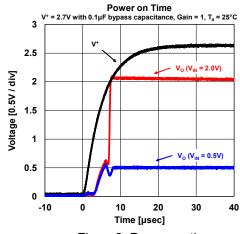

#### Power-on Time

The NJU7758x series typically require a power-on time of 10µs (Figure 2). Power-on time depends on the supply voltage, bypass capacitor, impedance of supply source and impedance other devices. While settling time, IC is unstable, such as output voltage.

Figure 2. Power on time

#### Rail-to-Rail Input

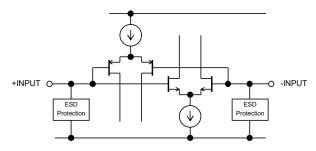

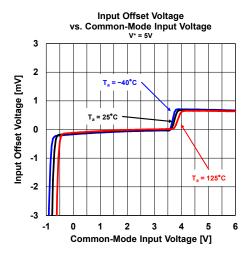

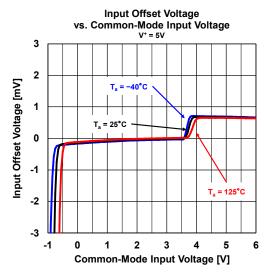

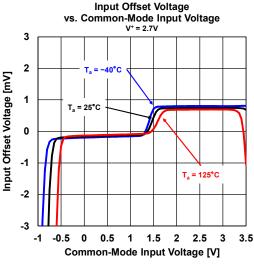

The input stage of NJU7758x series has two input differential pairs, PMOS and NMOS (Figure3). When the common- mode input voltage is from 200mV below the negative supply voltage to the typically (V<sup>+</sup>) – 1.3V, the PMOS pair is active. When the common-mode input voltage close to the positive supply, typically (V<sup>+</sup>) – 1.3V to 200mV above positive supply, the NMOS pair is active. In the transition region, the performance of offset voltage, as shown in figure4, offset voltage drift, CMR, SVR and THD is slightly degraded.

Figure 3. Simplified Schematic of Input Stage

Figure 4. Offset Voltage change with common-mode input voltage.

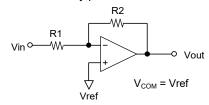

For the best performance design is inverting amplifier shown in Figure 5. Inverting amplifier has a constant common-mode voltage equal to Vref. If Vref voltage is constant and is chosen to avoid transition region, output will be best linearity performance.

Figure 5. Inverting Amplifier

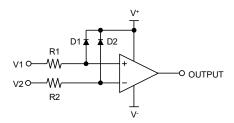

#### **Input Tolerant**

In general, common Op-Amp is protected by internal ESD diode that is connected from input pin to both the positive and negative power supply. In a buffer configuration, when input exceeds either supply voltage, ESD diode will be forward biased and current. If the current is high enough, even when input current over long periods of time or even short periods of time, can shift the electrical characteristics beyond the data sheet's guaranteed limits, or cause a permanent failure of the op amp.

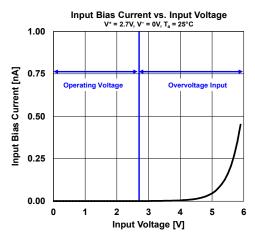

The input of the NJU7758x series has an ESD protection as shown in Figure 3. The input bias current is minimized in the input voltage even in operating voltage range and exceeding the V $^+$  supply, and the Op-Amp is protected from overvoltage current (Figure6). The maximum input voltage is absolute maximum rating of V $^-$  + 7V, but usually recommend design so that the input voltage is up to V $^-$  + 5.5V.

Figure 6. Input bias current vs. input voltage

NJU7758x series protects the input pin from overvoltage by shunting the overvoltage current to the V $^-$  supply rail. When the input voltage for V $^-$  – 0.3V to V $^-$  + 7V, the ESD protection is not activate and minimize the input bias current (Figure6).

For the input voltage 300mV below the negative supply voltage, the ESD protection operates to protect the input terminal. At this moment, the current flowing in protection element is allowed up to 10 mA. Momentary voltages above V<sup>-</sup> + 7V, the ESD protection also activate, and clamp inputs, but cannot protect against overvoltage excepting ESD.

In some applications, it may be necessary to prevent excessive overvoltage. Figure6 is example to protect input transistors. The external resistors R1, R2 limit the current through external diodes D1, D2.

$$(R1, R2) > \frac{V^{-}(V1, V2)}{10 \text{ mA}}$$

$(R1, R2) > \frac{(V1, V2) - V^{+}}{I_{D}}$

I<sub>F</sub>:Forward current of external diode.

Figure 7. Example of input protection

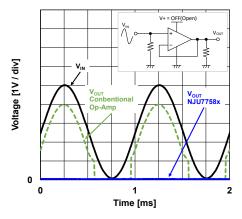

## Power Supply Protection for Overvoltage Condition

In general, many power supplies cannot sink current. If nothing within the circuit can sink the overvoltage current, if the overvoltage occurs with the supplies powered on, in the ESD diode protection Op-Amp, the supply voltage can exceed the intended operating voltage of the system.

Figure8 compares the output voltage of a conventional Op-Amp and NJU7758x series, when a signal is applied to the input terminal when the power supply voltage is OFF. In conventional Op-Amp, the output voltage is generated according to the input voltage. This output voltage will input an unexpected signal to the device connected to the subsequent stage of Op-Amp, which may cause malfunction or damage. Since NJU7758x series prevents the positive overvoltage current flowing through to power supply terminal and rising power supply voltage and keep the output voltage at 0V.

Figure8. Example of input protection

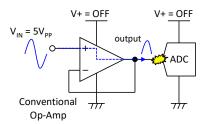

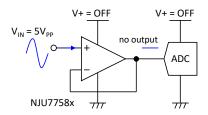

## Power Supply Protection for Overvoltage Condition (Continues)

The input tolerant function of the NJU7758x series prevents unexpected signal input to subsequent devices such as AD converters, or prevents applied voltage that can damage subsequent devices (Figure9a, Figure9b).

Figure9a. Conventional Op-Amp

Output voltage is generated when voltage is applied to the input terminal when the power is OFF. In some cases, subsequent devices will be damaged.

Figure9b. NJU7758x Series

The output voltage is 0V when the voltage is applied to the input terminal when the power is OFF. Input tolerant function protects subsequent devices.

#### Enhanced C-Drive ™

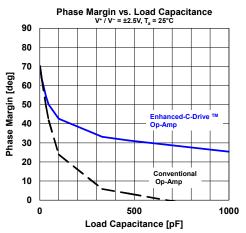

A typical high-speed Op-Amp causes a phase lag and a decrease in gain bandwidth product (GBW) when the capacitive load increases due to pattern wiring or cable routing. The phase lag causes ringing and overshoot in the step response, and the decrease in GBW results in a decrease in the amplification factor at AC output signals.

The NJU7758x series uses *Enhanced C-Drive* ™ technology to minimize performance degradation under such capacitive loads.

Figure 10 shows a comparison of the phase margins of a typical Op-Amp and an *Enhanced C-Drive* TM Op-Amp due to a capacitive load. A typical Op-Amp has a phase margin of less than 30 degree with a capacitive load of 100pF, whereas an *Enhanced C-Drive* TM Op-Amp has a similar phase margin at 1000pF.

Figure 10. Suppresses the decrease in phase margin due to capacitive load

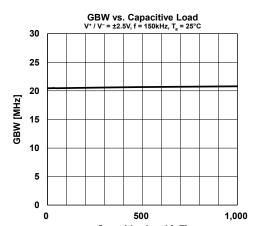

Some conventional Op-Amps have a reduced GBW as increasing capacitive load, causes a decrease in amplitude and distortion of the AC output signals. As shown in Figure11, the *Enhanced C-Drive* <sup>TM</sup> Op-Amp can output an AC signal with little distortion even with a large capacitive load by suppressing the decrease in GBW

The NJU7758x series eliminates the necessary to consider pattern wiring and cable capacity when designing sets that requires high-speed response, making it possible to reduce the mounting area and design period.

Figure 11. Supplestives the Gerease of GBW due to capacitive load

#### Capacitive Load

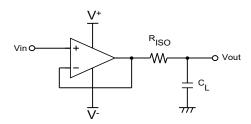

The NJU7758x series can use at unity gain follower. The unity gain follower is the most sensitive configuration to capacitive load, but Enhanced C-Drive TM technology minimizes performance degradation under capacitive loads.

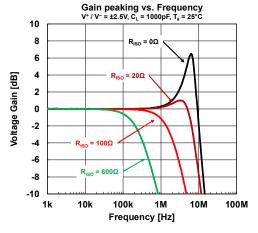

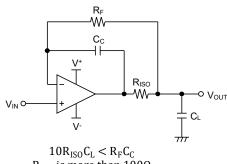

The NJU7758x series is unity gain stable for capacitive loads of 1000pF. To drive heavier capacitive loads, an isolation resistor, R<sub>ISO</sub> as shown Figure 12, should be used. RISO improves the feedback loop's phase margin by making the output load resistive at higher frequencies. The larger the value of R<sub>ISO</sub>, the more stable the output voltage will be. However, larger values of R<sub>ISO</sub> result in reduced output swing, reduced output current drive and reduced frequency bandwidth (Figure 13).

Figure 12. Isolating capacitive load

Figure 13. Gain peaking with RISO

Figure 14 shows the isolation circuit with R<sub>ISO</sub>, R<sub>F</sub> and Cc. Minimize the effect of voltage drop due to Riso and output current.

$R_{ISO}$  is more than  $100\Omega$

Figure 14. Isolating capacitive load with R<sub>ISO</sub>, R<sub>F</sub> and  $C_{C}$

#### Low noise voltage and input offset voltage drift

The NJU7758x series features very low noise performance (Figure 15). The equivalent input noise voltage at 10kHz is 6nV / √Hz, and the Peak-to-Peak noise of 0.1Hz to 20MHz is only  $260\mu V_{PP}$ . In addition, the change in input offset voltage due to temperature change becomes ultra-low frequency noise of 0.1Hz or less, and appears as fluctuation of output voltage. The temperature change of the input offset voltage of the NJU7758x is 0.5uV/°C (typ.) (Figure 16), which means an ultra-low frequency noise of 90uV at a temperature change of -55 °C to 125 °C. The sum of these two noise voltages is 350uV for the NJU7758x series, which is equivalent to 1 / 2 LSB of a 12bit ADC. The NJU7758x series is also compatible with highprecision, high-speed AD converters.

Figure 15. Equivalent input noise voltage

#### **■ APPLICATION NOTE**

## Low noise voltage and offset voltage drift (Continues)

Figure 16. Input offset voltage drift vs. temperature

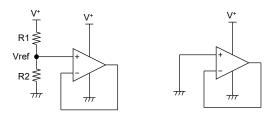

#### **Terminating unused Op-Amps**

Figure 17 shows examples of common method of terminating uncommitted operational amplifiers with using dual or quad. Improper termination can be result increase supply current, heating and noise in Op-Amps.

Figure 17. Terminating unused Op-Amps

#### **Differential Amplifier**

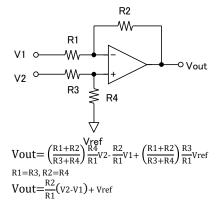

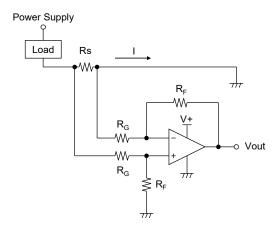

Figure 18 shows a one Op-Amp differential amplifier that consists of the single Op-Amp and four external resistors. Differential amplifier amplifies the difference between its two input pins, and rejects the commonmode input voltage at both input pins. This is used in variety of applications including current sensing, differential to single-end converter, isolation amplifier to remove common-mode noise.

Figure 18. Differential Amplifier

The differential amplifier's common-mode rejection ratio (CMR) is primarily determined by resistor mismatches, not by the Op-Amp's CMR. Ideally, the resistors are chosen such that R2/R1 = R4/R3. The CMR due to the resistors in differential amplifier can be calculated using the below formula:

$$\begin{array}{ll} \text{CMR}_{R\_error} & \approx & 20log \bigg( \frac{_{1} + \frac{R2}{R1}}{_{4}R_{error}} \bigg) \\ \text{CMR}_{R\_error} = \text{CMR} \ due \ only \ to \ the \ resistors} \\ R_{error} = Resistor's \ tolerance \end{array}$$

#### Example:

R2 / R1 = 1 and  $R_{error} = 0.1\%$ , then CMR = 54dB R2 / R1 = 1 and  $R_{error} = 1\%$ , then CMR = 34dB If using resistors with 1% tolerance and gain = 1, the CMR will only be 34dB.

#### **Instrumentation Amplifier**

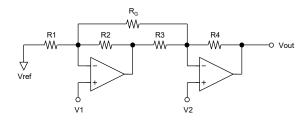

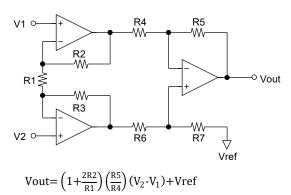

The instrumentation amplifier is suitable for requiring high input impedance and high common mode noise rejection at high gains. Figure19 and Figure20 is instrumentation amplifier using two or three Op-Amp. Supply the reference voltage (Vref) with a low impedance source to keep accuracy.

$$\begin{split} &Vout {=} \left(1 {+} \frac{R4}{R3} {+} \frac{2R4}{R_G} \right) (V2 {-} V1) {+} Vref \\ &R1 {=} R4, R2 {=} R3 \\ &CMR_{R\_error} \approx 20log \left( \frac{1 {+} \frac{R4}{R3} {+} \frac{2R4}{R_G}}{4R_{error}} \right) \end{split}$$

Figure 19. Instrumentation Amplifier with two Op-Amp

R2=R3, R4=R6, R5=R7

$$CMR_{R\_error} \approx 20log \left(\frac{R1+2R2}{R1} \times \frac{1+\frac{R5}{R4}}{4R_{error}}\right)$$

Figure 20. Instrumentation Amplifier with three Op-Amp

#### **Current Sensing**

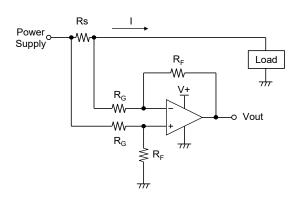

Current sensing applications are one such application in a wide range of electronic applications and mostly used for feedback control systems, including power metering battery life indicators and chargers, over- current protection and supervising circuit, automotive, and medical equipment. In such applications, it is desirable to use a shunt with very low resistance to minimize the series voltage drop and minimizes wasted power, and allows the measurement of high current. The NJU7758x series is ideal for these current sensing applications. Figure21 shows a high-side current sensing circuit, and Figure22 shows a low-side current sensing circuit. The NJU7758x series has rail-to-rail input and output characteristics, thus allows the both of high-side and low-side current sensing circuit.

The differential amplifier's common-mode rejection ratio (CMR) is primarily determined by resistor mismatches. For details, refer to differential amplifiers in the application note.

Figure 21. High-Side Current Sensing

Figure 22. Low-Side Current Sensing

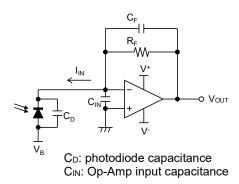

#### **Transimpedance Amplifier**

The features high input impedance with CMOS input and low power can be used for transimpedance amplifier applications shown in Figure23. The output voltage of amplifier is given by the equation  $V_{OUT} = I_{IN} \cdot R_F$ . Since the output voltage swing of amplifier is limited,  $R_F$  should be selected such that all possible values of  $I_{IN}$  can be detected.

Figure 23. Transimpedance amplifier

The  $C_D$ ,  $C_{IN}$  and  $R_F$  generate a phase lag which causes gain-peaking and can destabilized circuit. The essential component for obtaining a maximally flat response is a feedback capacitor  $C_F$ .  $C_F$  is usually added in parallel with  $R_F$  to maintain circuit stability and to control the frequency response. To maximally flat, 2nd order response,  $R_F$  and  $C_F$  should be chosen by using below equation.

$$C_{F} = \sqrt{\frac{C_{IN} + C_{D}}{GBW \times 2\pi \times R_{F}}}$$

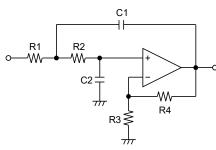

#### Sallen-Key 2nd-Order Active Low-Pass Filter

The Sallen-Key 2nd-order active low-pass filter is shown in Figure24. It can be used for a multiple pole filter required high attenuation.

$$\begin{array}{l} R\!=\!R1\!=\!R2 \ , \ C\!=\!C1\!=\!C2 \\ Q : Quality factor \ , \ G_{DC} : DC \ Gain \\ f_{\text{-}3dB}\!=\!\frac{1}{2\pi RC} \ , \ Q\!=\!\frac{1}{3\text{-}G_{DC}} \ , \ G_{DC}\!=\!1\!+\!\frac{R^4}{R^3}\!=\!3\!-\!\frac{1}{Q} \end{array}$$

Figure 24. Sallen-Key 2nd-Order Low-Pass Filter

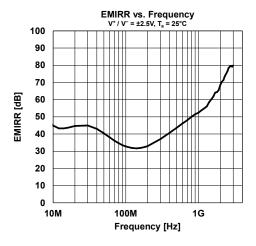

#### **EMIRR (EMI Rejection Ratio) Definition**

EMIRR is a parameter indicating the EMI robustness of an Op-Amp. The definition of EMIRR is given by the following equation1.

$$EMIRR = 20 \cdot log \left( \frac{V_{RF\_PEAK}}{|\Delta V_{IO}|} \right) --- eq.1$$

$V_{RF\_PEAK}$ : RF Signal Amplitude [V<sub>P</sub>]  $\Delta V_{IO}$ : Input offset voltage shift quantity [V]

The tolerance of the RF signal can be grasped by measuring an RF signal and offset voltage shift quantity. Offset voltage shift is small so that a value of EMIRR is big. And it understands that the tolerance for the RF signal is high. In addition, about the input offset voltage shift with the RF signal, there is the thinking that influence applied to the input terminal is dominant. Therefore, generally the EMIRR becomes value that applied an RF signal to +INPUT terminal.

\*For details, refer to "Application Note for EMI Immunity" in our HP: http://www.njr.com/

#### **■ TYPICAL CHARACTERISTICS**

#### **■ TEST CIRCUITS**

• Isupply, Vio, CMR, SVR  $R_G = 50\Omega$ ,  $R_F = 50k\Omega$

$$V_{IO} = \frac{R_G}{(R_G + R_F)} \times (V_O - V_{REF})$$

$$CMR = 20log \frac{\Delta V_{COM} \left(1 + \frac{R_F}{R_G}\right)}{\Delta V_{O}}$$

$$\begin{aligned} &SVR = 20log \frac{\Delta V_S \left(1 + \frac{R_F}{R_G}\right)}{\Delta V_O} \\ &V_S = V^+ - V^- \\ &V_{REF} = V_S \slash 2 \end{aligned}$$

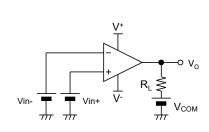

• Voh, Vol

$$\begin{split} &V_S = \left(V^+ - V^-\right) / \ 2 \\ &V_{OH}; \ Vin+ = 1 V, \ Vin- = 0 V, \ V_{COM} = V_S \ / \ 2 \\ &V_{OL}; \ Vin+ = 0 V, \ Vin- = 1 V, \ V_{COM} = V_S \ / \ 2, \ V- \\ \end{split}$$

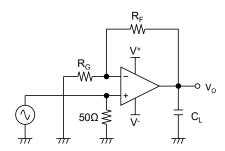

• GBW

$$R_G = 1k\Omega$$

,  $R_F = 100k\Omega$

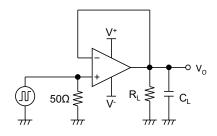

• SR

$$R_L = 100k\Omega$$

Vo

$$\frac{90\%}{\Delta V} \Delta V = \frac{90\%}{\Delta t}$$

$$SR = \frac{\Delta V}{\Delta t}$$

#### **■ REVISION HISTORY**

| Date           | Revision | Changes                                                                   |

|----------------|----------|---------------------------------------------------------------------------|

| May 30, 2019   | Ver.1.0  | Initial release                                                           |

| March 30, 2020 | Ver.1.1  | Collected condition of input voltage in RECOMMENDED OPERATING CONDITIONS. |

| May 24, 2022   | Ver.1.2  | Updated Data sheet format.                                                |

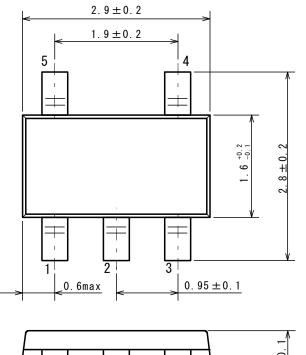

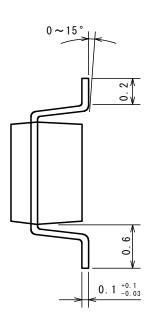

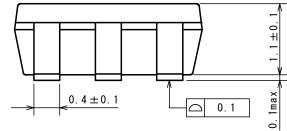

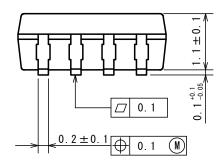

SOT-23-5

#### **■ PACKAGE DIMENSIONS**

SOT-23-5

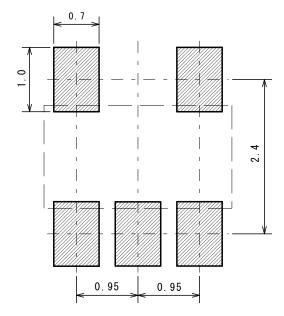

#### ■ EXAMPLE OF SOLDER PADS DIMENSIONS

UNIT: mm

SOT-23-5

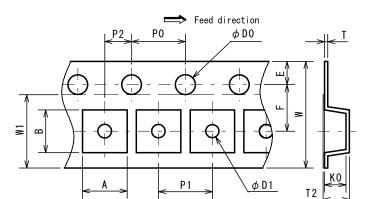

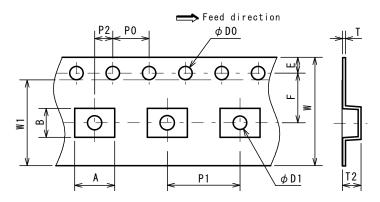

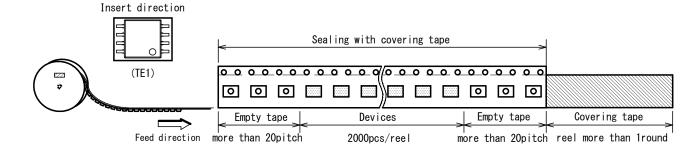

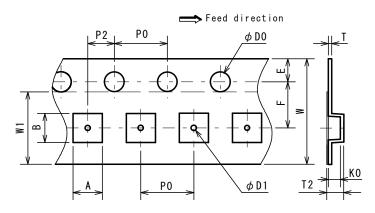

#### **■ PACKING SPEC**

#### **TAPING DIMENSIONS**

| SYMBOL | DIMENSION       | REMARKS           |

|--------|-----------------|-------------------|

| A      | 3.3±0.1         | BOTTOM DIMENSION  |

| В      | 3.2±0.1         | BOTTOM DIMENSION  |

| D0     | 1. 55           |                   |

| D1     | 1. 05           |                   |

| E      | 1.75±0.1        |                   |

| F      | $3.5 \pm 0.05$  |                   |

| P0     | 4.0±0.1         |                   |

| P1     | 4.0±0.1         |                   |

| P2     | $2.0 \pm 0.05$  |                   |

| T      | $0.25 \pm 0.05$ |                   |

| T2     | 1.82            |                   |

| K0     | 1.5±0.1         |                   |

| W      | 8.0±0.3         |                   |

| W1     | 5. 5            | THICKNESS 0. 1MAX |

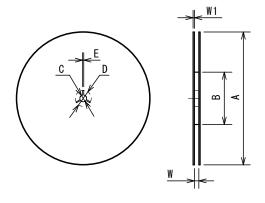

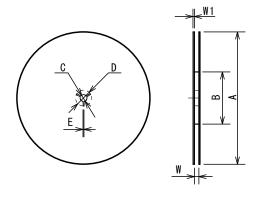

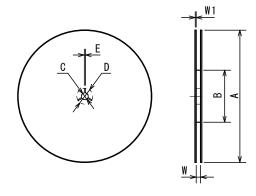

#### **REEL DIMENSIONS**

| SYMBOL | DIMENSION      |

|--------|----------------|

| Α      | $\phi$ 180 ± 1 |

| В      | φ 60±1         |

| С      | φ 13±0.2       |

| D      | $\phi$ 21±0.8  |

| Е      | 2±0.5          |

| W      | 9±0.5          |

| W1     | 1.2±0.2        |

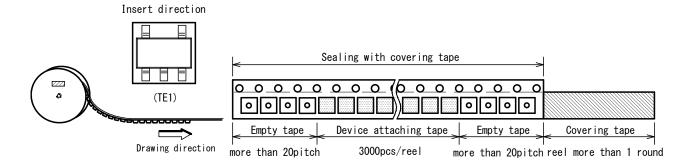

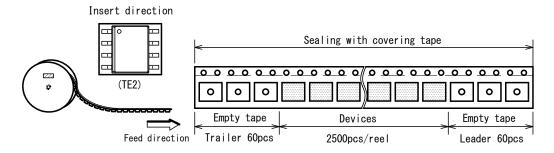

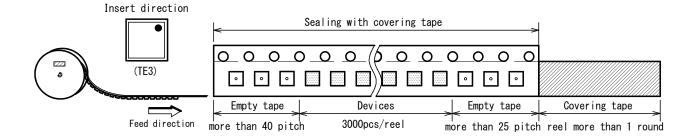

#### **TAPING STATE**

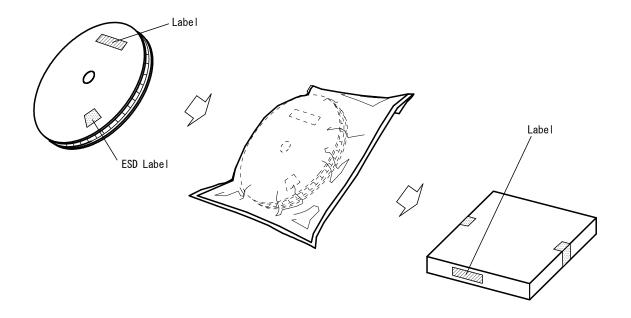

#### **PACKING STATE**

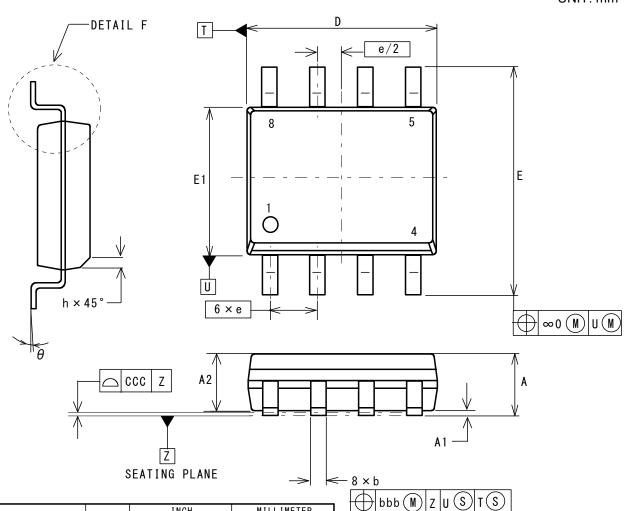

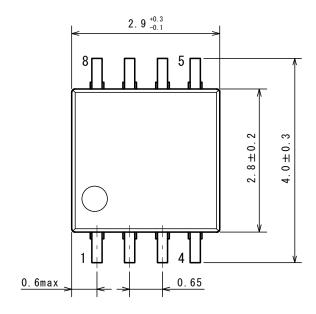

SOP8 PI-SOP8-E-A

#### ■ PACKAGE DIMENSIONS

|                  | SYMBOL         | INCH  |        | MILLIMETER |      |         |      |

|------------------|----------------|-------|--------|------------|------|---------|------|

| DESCRIPTION      |                | MIN   | NCM    | MAX        | MIN  | NCM     | MAX  |

| TOTAL THICKNESS  | Α              | . 053 |        | . 069      | 1.35 |         | 1.75 |

| STAND OFF        | <b>A</b> 1     | . 004 |        | . 010      | 0.10 |         | 0.25 |

| MOLD THICKNESS   | <b>A</b> 2     | . 049 |        | -          | 1.25 |         | -    |

| LEAD WIDTH       | b              | . 014 |        | . 019      | 0.35 |         | 0.49 |

| L/F THICKNESS    | С              | . 007 |        | . 010      | 0.19 |         | 0.25 |

| BODY SIZE        | D              | . 189 |        | . 197      | 4.80 |         | 5.00 |

|                  | E <sub>1</sub> | . 150 |        | . 157      | 3.80 |         | 4.00 |

| LEAD PITCH       | Е              | . 228 |        | . 244      | 5.80 |         | 6.20 |

|                  | е              |       | 050 BS | C          | 1    | . 27 BS | С    |

|                  | L              | . 015 |        | . 049      | 0.40 |         | 1.25 |

|                  | h              | . 010 |        | . 020      | 0.25 |         | 0.50 |

|                  | θ              | 0°    |        | 8°         | 0°   |         | 7°   |

|                  | <i>θ</i> 1     | 5°    |        | 15°        | 5°   |         | 15°  |

|                  | θ 2            | 2 °   | 7°     | 12°        | 2°   | 7°      | 12°  |

| LEAD EDGE OFFSET | ∞0             |       | . 010  |            |      | 0.25    | -    |

| LEAD OFFSET      | bbb            |       | . 010  |            |      | 0.25    |      |

| COPLANARITY      | CCC            |       | . 004  |            |      | 0.10    | ·    |

SOP8 PI-SOP8-E-A

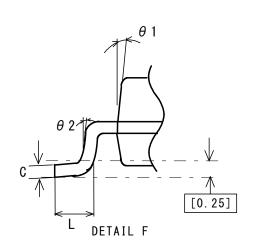

#### ■ EXAMPLE OF SOLDER PADS DIMENSIONS

SOP8 PI-SOP8-E-A

#### **■ PACKING SPEC**

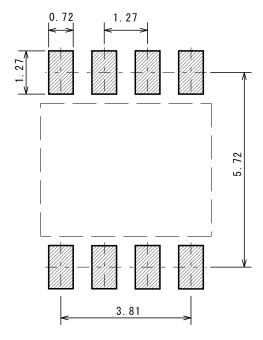

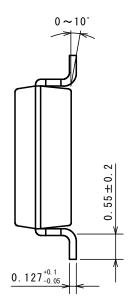

#### **REEL DIMENSIONS / TAPING DIMENSIONS**

UNIT: mm

#### **TAPING STATE**

#### **PACKING STATE**

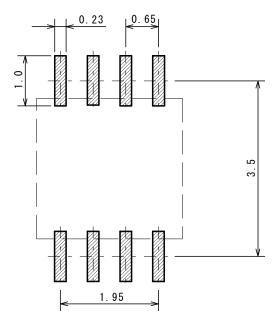

## MSOP8 MEET JEDEC MO-187-DA (VSP8)

PI-MSOP8-E-A

#### **■ PACKAGE DIMENSIONS**

## MSOP8 MEET JEDEC MO-187-DA (VSP8)

PI-MSOP8-E-A

#### ■ EXAMPLE OF SOLDER PADS DIMENSIONS

## MSOP8 MEET JEDEC MO-187-DA (VSP8)

PI-MSOP8-E-A

UNIT: mm

#### **■ PACKING SPEC**

#### **TAPING DIMENSIONS**

| SYMBOL | DIMENSION  | REMARKS          |

|--------|------------|------------------|

| A      | 4. 4       | BOTTOM DIMENSION |

| В      | 3. 2       | BOTTOM DIMENSION |

| D0     | 1. 5 +0.1  |                  |

| D1     | 1.5 +0.1   |                  |

| E      | 1.75±0.1   |                  |

| F      | 5.5±0.05   |                  |

| P0     | 4.0±0.1    |                  |

| P1     | 8.0±0.1    |                  |

| P2     | 2.0±0.05   |                  |

| T      | 0.30±0.05  |                  |

| T2     | 2.0 (MAX.) |                  |

| W      | 12.0±0.3   |                  |

| W1     | 9. 5       | THICKNESS 0.1max |

#### **REEL DIMENSIONS**

| SYMBOL | DIMENSION        |  |

|--------|------------------|--|

| Α      | $\phi 254 \pm 2$ |  |

| В      | φ100±1           |  |

| С      | φ 13±0.2         |  |

| D      | φ 21±0.8         |  |

| E      | 2±0.5            |  |

| W      | 13.5±0.5         |  |

| W1     | 2.0±0.2          |  |

#### **TAPING STATE**

#### **PACKING STATE**

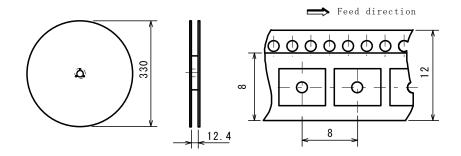

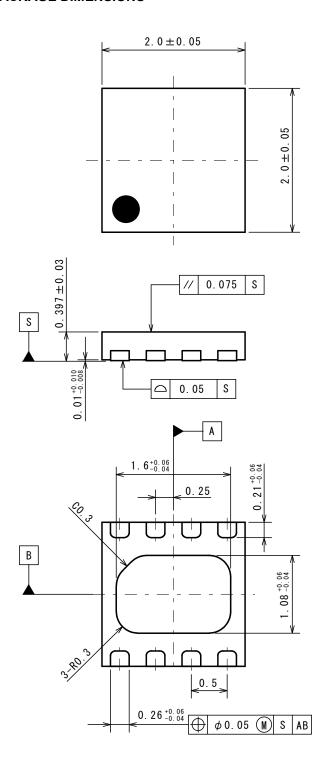

## DFN8-U1 (ESON8-U1)

PI-DFN8-U1-E-A

#### ■ PACKAGE DIMENSIONS

## DFN8-U1 (ESON8-U1)

PI-DFN8-U1-E-A

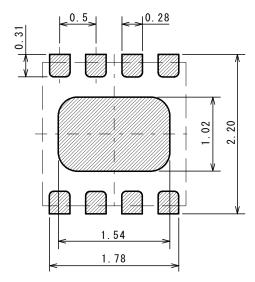

#### ■ EXAMPLE OF SOLDER PADS DIMENSIONS

## DFN8-U1 (ESON8-U1)

PI-DFN8-U1-E-A

UNIT: mm

#### **■ PACKING SPEC**

#### **TAPING DIMENSIONS**

| SYMBOL | DIMENSION             | REMARKS          |

|--------|-----------------------|------------------|

| A      | 2.25±0.05             | BOTTOM DIMENSION |

| В      | 2. 25±0. 05           | BOTTOM DIMENSION |

| D0     | 1. 5 <sup>+0. 1</sup> |                  |

| D1     | 0.5±0.1               |                  |

| E      | 1.75±0.1              |                  |

| F      | 3.5±0.05              |                  |

| P0     | 4.0±0.1               |                  |

| P1     | 4.0±0.1               |                  |

| P2     | 2.0±0.05              |                  |

| T      | $0.25\pm0.05$         |                  |

| T2     | 1.00±0.07             |                  |

| K0     | $0.65 \pm 0.05$       |                  |

| W      | 8.0±0.2               |                  |

| W1     | 5. 5                  | THICKNESS 0.1max |

#### **REEL DIMENSIONS**

| SYMBOL | DIMENSION                |

|--------|--------------------------|

| Α      | $\phi$ 180 $^{0}_{-1.5}$ |

| В      | $\phi$ 60 $^{+1}_{0}$    |

| С      | φ 13±0.2                 |

| D      | φ 21±0.8                 |

| Е      | 2±0.5                    |

| W      | 9 +0.3                   |

| W1     | 1. 2                     |

#### **TAPING STATE**

#### **PACKING STATE**

- 1. The products and the product specifications described in this document are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to our sales representatives for the latest information thereon

- 2. The materials in this document may not be copied or otherwise reproduced in whole or in part without the prior written consent of us.

- 3. This product and any technical information relating thereto are subject to complementary export controls (so-called KNOW controls) under the Foreign Exchange and Foreign Trade Law, and related politics ministerial ordinance of the law. (Note that the complementary export controls are inapplicable to any application-specific products, except rockets and pilotless aircraft, that are insusceptible to design or program changes.) Accordingly, when exporting or carrying abroad this product, follow the Foreign Exchange and Foreign Trade Control Law and its related regulations with respect to the complementary export controls.

- 4. The technical information described in this document shows typical characteristics and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under our or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, telecommunication equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death should first contact us.

- Aerospace Equipment

- Equipment Used in the Deep Sea

- · Power Generator Control Equipment (nuclear, steam, hydraulic, etc.)

- · Life Maintenance Medical Equipment

- · Fire Alarms / Intruder Detectors

- Vehicle Control Equipment (automotive, airplane, railroad, ship, etc.)

- Various Safety Devices

- Traffic control system

- Combustion equipment

In case your company desires to use this product for any applications other than general electronic equipment mentioned above, make sure to contact our company in advance. Note that the important requirements mentioned in this section are not applicable to cases where operation requirements such as application conditions are confirmed by our company in writing after consultation with your company.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order to prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. The products have been designed and tested to function within controlled environmental conditions. Do not use products under conditions that deviate from methods or applications specified in this datasheet. Failure to employ the products in the proper applications can lead to deterioration, destruction or failure of the products. We shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of the products.

- 8. Quality Warranty

- 8-1. Quality Warranty Period

- In the case of a product purchased through an authorized distributor or directly from us, the warranty period for this product shall be one (1) year after delivery to your company. For defective products that occurred during this period, we will take the quality warranty measures described in section 8-2. However, if there is an agreement on the warranty period in the basic transaction agreement, quality assurance agreement, delivery specifications, etc., it shall be followed.

- 8-2. Quality Warranty Remedies

- When it has been proved defective due to manufacturing factors as a result of defect analysis by us, we will either deliver a substitute for the defective product or refund the purchase price of the defective product.

- Note that such delivery or refund is sole and exclusive remedies to your company for the defective product.

- 8-3. Remedies after Quality Warranty Period

- With respect to any defect of this product found after the quality warranty period, the defect will be analyzed by us. On the basis of the defect analysis results, the scope and amounts of damage shall be determined by mutual agreement of both parties. Then we will deal with upper limit in Section 8-2. This provision is not intended to limit any legal rights of your company.

- 9. Anti-radiation design is not implemented in the products described in this document.

- 10. The X-ray exposure can influence functions and characteristics of the products. Confirm the product functions and characteristics in the evaluation stage.

- 11. WLCSP products should be used in light shielded environments. The light exposure can influence functions and characteristics of the products under operation or storage.

- 12. Warning for handling Gallium and Arsenic (GaAs) products (Applying to GaAs MMIC, Photo Reflector). These products use Gallium (Ga) and Arsenic (As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed of, please follow the related regulation and do not mix this with general industrial waste or household waste.

- 13. Please contact our sales representatives should you have any questions or comments concerning the products or the technical information.

Official website

https://www.nisshinbo-microdevices.co.jp/en/

**Purchase information**

https://www.nisshinbo-microdevices.co.jp/en/buy/