# PD69210/PD69220

## **PoE PSE Controller Datasheet**

#### Introduction

The Microchip Generation 6 family of PSE controllers include the PD69210 and PD69220 devices. The PD69210 and PD69220 have an identical feature set and differ only in physical pinout. The PD69210 and PD69220 are based on the Microchip SAM D21 family. The PD69210 or PD69220 are recommended for all new designs.

The PD69210 or PD69220 controllers when paired with the Microchip PD69208T4, PD69204T4, or PD69208M managers are part of a Power over Ethernet Power Supplying Equipment (PSE) system. This system enables designers to integrate enhanced mode PoE capabilities, as specified in IEEE 802.3af, IEEE 802.3at, IEEE 802.3bt, and PoH standards, into an Ethernet switch. The PD69210 and PD69220 will support up to 48 4-pair or 2-pair logical ports.

Both controllers are available in a 32-pin, 5 mm × 5 mm QFN package.

### **Typical PoE Application**

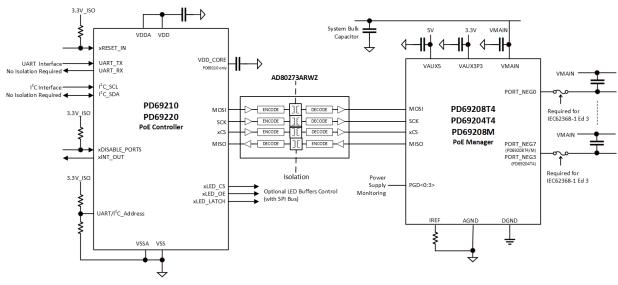

The following figure shows the typical PoE application of Microchip Generation 6 devices.

Figure 1. Typical PoE Application

Consult Microchip AN3361 Designing an IEEE 802.3af/802.3at/802.3bt-Compliant PD69208 48-Port PoE System.

# **Features Matrix**

| Feature                                | Description                                                                                                                                                      | PD69210                  | PD69220                  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|

| Support IEEE 802.3af/at                |                                                                                                                                                                  | Y                        | Y                        |

| Support IEEE 802.3bt                   |                                                                                                                                                                  | Υ                        | Υ                        |

| Support HDBaseT (POH)                  |                                                                                                                                                                  | Y                        | Y                        |

| Port control matrix                    | Port matrix control enables to ascribe each physical port in the system to a logical port.                                                                       | 2p/4p                    | 2p/4p                    |

| Logical ports                          | A logical port can be built from 2×physical ports or 1×physical port.                                                                                            | 48                       | 48                       |

| Max 2-pair power                       |                                                                                                                                                                  | 45 W                     | 45 W                     |

| Power management                       | The system supports three power management modes: Class (LLDP), Dynamic, and Static.                                                                             | Per port                 | Per port                 |

| Power good                             | Used to select the system power bank to be applied to the specific PoE manager.                                                                                  | Y                        | Y                        |

| Port power limit                       | Configurable port power limit; when a port exceeds the limit, it is automatically disconnected.                                                                  | Y                        | Y                        |

| Interrupt pin                          | Interrupt out from PoE controller indicating events such as port on, port off, port fault, PoE device fault, voltage out of range, and more.                     | Y                        | Y                        |

| Disable port pin                       | Shuts down all of the PoE ports in the system.                                                                                                                   | Y                        | Y                        |

| System OK indication                   | System validity indication. Provides a digital output signal to the host or to control an LED to indicate system status. When the system is OK pin state is low. | Y                        | Y                        |

| Legacy (reduced capacitance) detection | Enables detection and powering of pre-standard devices (PDs).                                                                                                    | Per port                 | Per port                 |

| LED stream                             | A direct SPI interface to an external LED stream.                                                                                                                | Y                        | Υ                        |

| Fast PoE                               | Ability of a system to quickly boot and power up ports without waiting for the host setting.                                                                     | Y                        | Y                        |

| Perpetual PoE                          | Ability of a PoE system to maintain PoE power while upgrading host firmware or host is in reset.                                                                 | Y                        | Y                        |

| Communication                          | Communication interface with host.                                                                                                                               | I <sup>2</sup> C or UART | I <sup>2</sup> C or UART |

| Communications protocol                | Compatible with previous generations controllers.                                                                                                                | Y                        | Υ                        |

| Pin-compatible with PD69200            | Able to use on a PCB that was designed for the PD69200.                                                                                                          | N                        | Y                        |

|                                        | For I <sup>2</sup> C and UART programming information, see section UART or I <sup>2</sup> C Address Selection.                                                   |                          |                          |

| MSL1 and RoHS                          |                                                                                                                                                                  | Y                        | Y                        |

# **Table of Contents**

| Intr | oduction | on                                         | 1  |

|------|----------|--------------------------------------------|----|

|      | Typic    | al PoE Application                         | 1  |

|      | Featu    | ıres Matrix                                | 2  |

|      |          |                                            |    |

| 1.   | Archi    | tecture                                    |    |

|      | 1.1.     | Firmware                                   | 4  |

|      | 1.2.     | Communication                              | 4  |

|      | 1.3.     | GUI                                        | 4  |

|      | 1.4.     | Software Library                           | 5  |

|      | 1.5.     | SPI Communication                          | 5  |

|      | 1.6.     | UART                                       | 5  |

|      | 1.7.     | I <sup>2</sup> C                           | 5  |

|      | 1.8.     | UART or I <sup>2</sup> C Address Selection | 6  |

| 2.   | Elect    | rical Specifications                       | 7  |

|      | 2.1.     | Electrical Characteristics                 | 7  |

|      | 2.2.     | Immunity                                   | 7  |

|      | 2.3.     | Absolute Maximum Ratings                   | 7  |

| 3.   | Pins.    |                                            | 8  |

|      | 3.1.     | Pin Diagrams                               |    |

|      | 3.2.     | Pin Descriptions                           |    |

|      | 0.2.     | 7 #1 B0001 pt.010                          |    |

| 4.   | Pack     | age Information                            | 11 |

|      | 4.1.     | PD69210 Package Outline Drawing            | 11 |

|      | 4.2.     | PD69220 Package Outline Drawing            | 12 |

|      | 4.3.     | Thermal Specifications                     | 13 |

|      | 4.4.     | Recommended PCB Layout                     | 14 |

|      | 4.5.     | Recommended Solder Reflow Information      | 15 |

|      | 4.6.     | Reference Documents                        | 16 |

| 5.   | Orde     | ring Information                           | 17 |

| 6.   | Revis    | sion History                               | 18 |

|      |          |                                            |    |

| The  | e Micro  | ochip Website                              | 19 |

| Pro  | duct C   | Change Notification Service                | 19 |

| Cu   | stomer   | Support                                    | 19 |

| Mic  | rochip   | Devices Code Protection Feature            | 19 |

| Leç  | gal Not  | ice                                        | 19 |

| Tra  | demar    | ks                                         | 20 |

|      |          | anagement Systemanagement System           |    |

|      |          | e Sales and Service                        |    |

| VVC  | iiuwide  | 5 Jaies and Jenvice                        | ∠1 |

#### 1. Architecture

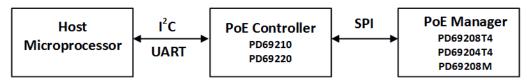

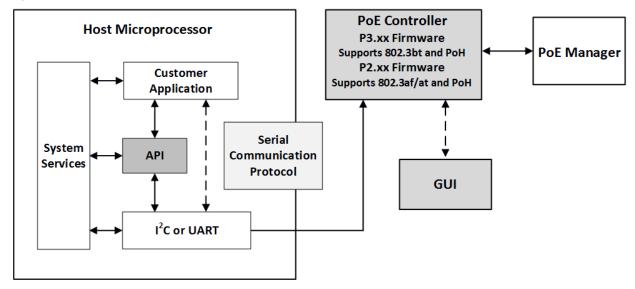

The following figures show the simplified hardware architecture and firmware architecture of the PoE system based on the PD69210 and PD69220 controllers and PD69208T4, PD69204T4, and PD69208M managers.

Figure 1-1. Simplified Hardware Architecture

Figure 1-2. Simplified Firmware Architecture

- · Dark grey boxes indicate Microchip-supplied firmware.

- Light grey boxes indicate Microchip-provided documentation.

- · White boxes are user-supplied.

#### 1.1 Firmware

- Firmware is pre-programmed in PD69210 and PD69220. Firmware version is identifiable via the IC Ordering Part Number.

- · Firmware is vendor-agnostic with regards to choice of the host controller.

- May be operated standalone or with I<sup>2</sup>C or UART communication to host.

- Default profiles are coded into the firmware. Microchip offers a Configuration Tool for profile modification.

- Firmware is field-upgradeable via the I<sup>2</sup>C or UART link.

#### 1.2 Communication

Communication between the host application and the controller's firmware may be done via a 15-byte protocol. Customers may use a Microchip-provided API. Microchip provides a Serial Communication Protocol Guide.

#### 1.3 GUI

This is a diagnostic tool for control of the Microchip PSE emulating or bypassing the host processor.

#### 1.4 Software Library

Firmware (without the boot section), GUI, and API are available on Microchip's Software Library.

#### 1.5 SPI Communication

PD69208T4, PD69204T4, and PD69208M managers use SPI communication in SPI slave mode to communicate with the various controllers. Each manager has an address determined by ADDR0–ADDR3 pins. Each controller can support up to 12 ICs at addresses 0–11. The actual frequency between PD692x0 ICs is 1 MHz.

The following table lists the SPI communication packet structure.

Table 1-1. SPI Communication—Packet Structure

| Control Byte Selects PD69208T4 According to Address | R/W Bit   |        | (Read Access Only) | Data Written to IC<br>(Write Access Only)<br>Read from IC (Read<br>Access Only) |

|-----------------------------------------------------|-----------|--------|--------------------|---------------------------------------------------------------------------------|

| 8 bits                                              | R(0)/W(1) | 8 bits | 8 bits             | 16 bits                                                                         |

For more information about the SPI interface, see the PD69208T4, PD69204T4, and PD69208M Manager Datasheet.

#### **1.6 UART**

A pull-up resistor is required on the UART communication line. For more information, see AN3361 Designing an IEEE 802.3af/at/bt PoE System Based on PD692x0/PD69208.

UART communications configuration:

• Bits per second: 19,200 bps

· Data bits: 8

Parity: None Stop bits: 1Flow control: None

#### 1.7 I<sup>2</sup>C

The PD692x0 requires the host to support I<sup>2</sup>C clock stretch.

I<sup>2</sup>C communication configuration:

· Address: 7 bits

Clock stretch: Host should support

· Transaction: 15 bytes or 1 byte

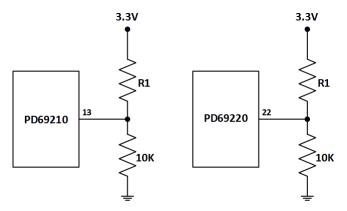

#### 1.8 UART or I<sup>2</sup>C Address Selection

The choice of UART or I<sup>2</sup>C interface between the host CPU is made by applying a specific voltage level to pin #13 (I2C\_ADDR\_MEAS) on the PD69210, or by applying a specific voltage level to pin #22 (I2C\_ADDR\_MEAS) on the PD69220. Additionally, the specific I<sup>2</sup>C address is also set by this voltage level. In all cases, the voltage is set via an external resistor divider as shown in the following figure.

Figure 1-3. I<sup>2</sup>C Address Selection

The specific Value of R to choose UART or  $I^2C$  and to set the address is given in the following tables for PD69210 and PD69220.

Table 1-2. I<sup>2</sup>C Address Selection

| I2C Address (Hexadecimal) | R1- ΚΩ (1%) |

|---------------------------|-------------|

| UART                      | N.C.        |

| 0x4                       | 147         |

| 0x8                       | 86.6        |

| 0xC                       | 57.6        |

| 0x10                      | 43.2        |

| 0x14                      | 34          |

| 0x18                      | 26.7        |

| 0x1C                      | 22.1        |

| 0x20                      | 18.2        |

| 0x24                      | 15.4        |

| 0x28                      | 13          |

| 0x2C                      | 11          |

| 0x30                      | 9.31        |

| 0x34                      | 7.87        |

| 0x38                      | 6.49        |

| 0x3C                      | 5.49        |

## 2. Electrical Specifications

The following sections describe the electrical specifications for the PD69210 and PD69220 devices.

#### 2.1 Electrical Characteristics

For a complete list of electrical characteristics, see Microchip SAM21 Family Datasheet.

Table 2-1. General Operating Conditions

| Symbol         | Parameter            | Conditions | Min | Тур | Max  | Units |

|----------------|----------------------|------------|-----|-----|------|-------|

| $V_{DD}$       | Power supply voltage |            | 3.0 | 3.3 | 3.63 | V     |

| $V_{DDA}$      | Power supply voltage |            | 3.0 | 3.3 | 3.63 | V     |

| T <sub>A</sub> | Temperature range    |            | -40 | 25  | 85   | °C    |

| TJ             | Junction temperature |            |     |     | 100  | °C    |

### 2.2 Immunity

Table 2-2. Immunity

| Symbol | Parameter  | Conditions       | Min   | Max   | Units |

|--------|------------|------------------|-------|-------|-------|

| ESD    | ESD rating | HBM <sup>1</sup> | -2000 | +2000 | V     |

|        |            | CDM <sup>2</sup> | -500  | +500  | V     |

- 1. ESD HBM complies with JESD22 Class 2 standard.

- 2. ESD CDM complies with JESD22 Class 1 standard.

#### 2.3 Absolute Maximum Ratings

Stresses beyond those listed in this section may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2-3. Absolute Maximum Ratings

| Symbol                                    | Parameter                               | Min         | Max         | Units |

|-------------------------------------------|-----------------------------------------|-------------|-------------|-------|

| $V_{DD}$                                  | Power supply voltage                    | 0           | 3.8         | V     |

| V <sub>PIN</sub>                          | Pin voltage with respect to GND and VDD | GND – 0.6 V | VDD + 0.6 V | V     |

| Lead soldering temperature (40 s, reflow) |                                         |             | 260         | °C    |

| Storage temperature                       |                                         | -60         | 150         | °C    |

### 3. Pins

The PD69210 and PD69220 controller each has 32 pins, which are described in this section.

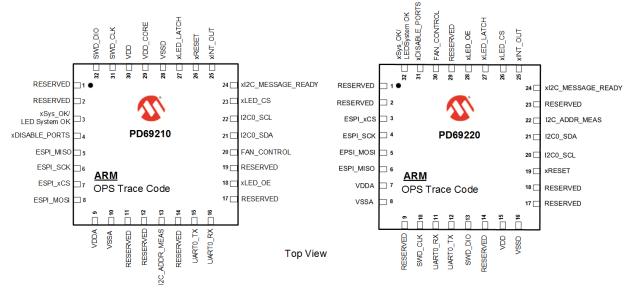

### 3.1 Pin Diagrams

The following figures represent the top view of PD69210 and PD69220 devices.

Figure 3-1. PD69210 and PD69220 Pin Diagram

Note: For definitions about markings in the pinout diagram, see Ordering Information.

#### 3.2 Pin Descriptions

The following table describes the functional pin descriptions of the PD69210 and PD69220 devices.

Table 3-1. Pin Descriptions

| PD69210<br>Pin | PD69220<br>Pin | Designation           | Туре | Description                                                                                                                                                              |

|----------------|----------------|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 1              | Reserved              | OUT  | Reserved UART. Leave open.                                                                                                                                               |

| 2              | 2              | Reserved              | IN   | Reserved UART. Pull up to 3.3 V via 10 k $\Omega$ .                                                                                                                      |

| 3              | 32             | xSys_OK/LED System OK | OUT  | System validity indication. The behavior of this output is controlled by individual software mask. (Active Low)                                                          |

| 4              | 31             | xDISABLE_PORTS        | IN   | Disable all PoE ports. When this input is asserted low, the controller shuts down all PoE ports in the system.  See AN3361 for pin connection requirements. (Active Low) |

| 5              | 6              | ESPI_MISO             | IN   | ESPI bus to PoE manager. SPI master in, slave out. SPI packets are received on this line.                                                                                |

| contii         | continued      |               |            |                                                                                                                                                                 |  |

|----------------|----------------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PD69210<br>Pin | PD69220<br>Pin | Designation   | Туре       | Description                                                                                                                                                     |  |

| 6              | 4              | ESPI_SCK      | OUT        | ESPI bus to PoE manager. SPI clock output to PD6920x, and LED stream clock output, set to 1 MHz.                                                                |  |

| 7              | 3              | ESPI_xCS      | OUT        | ESPI bus to PoE manager. SPI chip select.<br>Pull-up required. See AN3361 for pin<br>connection requirements. (Active Low)                                      |  |

| 8              | 5              | ESPI_MOSI     | OUT        | ESPI bus from PoE manager. SPI master out, slave in. SPI packets are received on this line.                                                                     |  |

| 9              | 7              | VDDA          | Supply     | Main Supply 3.3 V.                                                                                                                                              |  |

| 10             | 8              | VSSA          | GND        | Ground.                                                                                                                                                         |  |

| 11             | 14             | Reserved      | Analog_IN  | Reserved Analog_IN. Connect to 3.3 V or GND through 10 $k\Omega.$                                                                                               |  |

| -              | 9, 29          | Reserved      | Analog_IN  | Reserved Analog_IN. Connect to 3.3 V.                                                                                                                           |  |

| 12, 19         | -              | Reserved      |            | Reserved. Leave open.                                                                                                                                           |  |

| 13             | 22             | I2C_ADDR_MEAS | Analog_IN  | Analog input to determine I <sup>2</sup> C address or UART operation.                                                                                           |  |

| 14             | 23             | Reserved      |            | Connect to GND.                                                                                                                                                 |  |

| 15             | 12             | UART0_TX      | OUT        | UART transmit to host. 15-byte protocol reply/<br>telemetry is transmitted on this line. The baud<br>rate is set to 19,200 bps.                                 |  |

| 16             | 11             | UART0_RX      | IN         | UART receive from a host. 15-byte protocol commands are received on this line. The baud rate is set to 19,200 bps. Pull-up is required. See AN3361 for details. |  |

| 17             | 18             | Reserved      | Oscillator | Reserved. Oscillator output. Leave open.                                                                                                                        |  |

|                | 17             | Reserved      | Oscillator | Reserved. Oscillator output. Leave open.                                                                                                                        |  |

| 18             | 28             | xLED_OE       | OUT        | Output enable signal for the LED stream. (Active Low)                                                                                                           |  |

| 20             | 30             | FAN_CONTROL   | OUT        | Logic out that may be used to control a fan driver. (Active High)                                                                                               |  |

| 21             | 21             | I2C0_SDA      | IN/OUT     | I <sup>2</sup> C bidirectional data. 15-byte protocol messages are transmitted on this line. Pull-up required, see AN3361 for details.                          |  |

| 22             | 20             | I2C0_SCL      | IN/OUT     | I <sup>2</sup> C clock from the host master. Speed is limited to 400 KHz. Clock stretch required. Pull-up required, see AN3361 for details.                     |  |

| 23             | 26             | xLED_CS       | OUT        | Chip select signal for LED stream. (Active Low)                                                                                                                 |  |

| conti          | nued           |                         |        |                                                                                                                                                                                                                                                                                                                                           |

|----------------|----------------|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD69210<br>Pin | PD69220<br>Pin | Designation             | Туре   | Description                                                                                                                                                                                                                                                                                                                               |

| 24             | 24             | xI2C_MESSAGE_READY      | OUT    | I <sup>2</sup> C message ready for reading by the host. Controller asserts this line low when it has an answer to the host. Therefore, the host can poll this line and initiate I <sup>2</sup> C read cycle only when the message is ready. After the host reads the data from the controller, this pin is asserted to high. (Active Low) |

| 25             | 25             | xINT_OUT                | OUT    | Interrupt output indication. This line is asserted low when a pre-configured event is in progress. (Active Low)                                                                                                                                                                                                                           |

| 26             | 19             | xRESET                  | IN/OUT | Host Reset input (Active Low). Controller can generate self-reset. In this case, the xRESET pin is driven low by the controller for 100 µs. See AN3361 for pin connection requirements.                                                                                                                                                   |

| 27             | 27             | xLED_LATCH <sup>2</sup> | OUT    | Latch signal for LED stream. (Active Low)                                                                                                                                                                                                                                                                                                 |

| 28             | 16             | VSSD                    | GND    | Ground.                                                                                                                                                                                                                                                                                                                                   |

| 29             | -              | VDD_CORE                | Power  | 1.2 V core voltage connect 1 μF capacitor to VSSD.                                                                                                                                                                                                                                                                                        |

| 30             | 15             | VDD                     | Supply | Main 3.3 V supply.                                                                                                                                                                                                                                                                                                                        |

| 31             | 10             | SWD_CLK                 |        | PD69210 use a 1 kΩ pull-up to 3.3 V.                                                                                                                                                                                                                                                                                                      |

|                |                |                         |        | PD69220 leave open or use 1k pull-up.                                                                                                                                                                                                                                                                                                     |

| 32             | 13             | SWD_DIO                 |        | Leave open.                                                                                                                                                                                                                                                                                                                               |

| ePAD           | ePAD           | ePAD                    |        | Connect to VSSA. Must have sufficient copper mass to ensure adequate thermal performance.                                                                                                                                                                                                                                                 |

### 4. Package Information

This section provides the package information for the PD69210 and PD69220 devices.

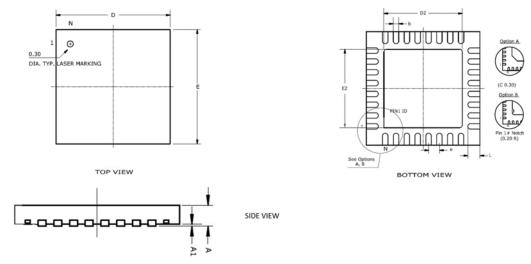

### 4.1 PD69210 Package Outline Drawing

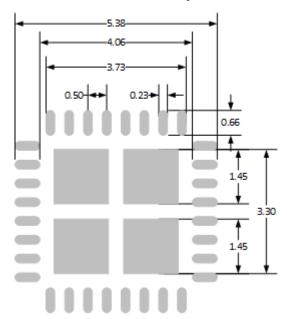

The following figure shows the package drawing of PD69210 device.

Figure 4-1. PD69210 Package Outline Drawing (32 Pin QFN 5 mm × 5 mm)

The following table lists the dimensions and measurements of the PD69210 package.

Table 4-1. PD69210 Package Outline Dimensions and Measurements

| Dimension | Millimeters |      | Inches    |       |

|-----------|-------------|------|-----------|-------|

|           | Min         | Max  | Min       | Max   |

| A         | 0.80        | 1.00 | 0.031     | 0.039 |

| A1        | 0.00        | 0.05 | 0         | 0.002 |

| е         | 0.50 BSC    |      | 0.02 BSC  |       |

| L         | 0.30        | 0.50 | 0.012     | 0.02  |

| b         | 0.18        | 0.30 | 0.007     | 0.012 |

| D2        | 3.50        | 3.70 | 0.138     | 0.147 |

| E2        | 3.50        | 3.70 | 0.138     | 0.147 |

| D         | 5.00 BSC    |      | 0.197 BSC |       |

| Е         | 5.00 BSC    |      | 0.197 BSC |       |

**Note:** Dimensions do not include protrusions; they should not exceed 0.155 mm (0.006 in.) on any side. Lead dimension should not include solder coverage. Dimensions are in millimeters and inches for reference.

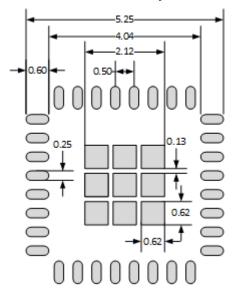

#### 4.2 PD69220 Package Outline Drawing

The following figure shows the package outline drawing of the PD69220 device.

Figure 4-2. PD69220 Package Outline Drawing (32-Pin LGA 5 mm × 5 mm)

The following table lists the dimensions and measurements of the PD69220 package.

Table 4-2. PD69220 Package Outline Dimensions and Measurements

| Dimension | Millimeters |      |     |

|-----------|-------------|------|-----|

|           | Min         | Тур  | Max |

| A         |             |      | 1   |

| A1        |             | 0.21 |     |

| A2        |             | 0.7  |     |

| D         |             | 5    |     |

| E         |             | 5    |     |

| continued |             |      |     |  |

|-----------|-------------|------|-----|--|

| Dimension | Millimeters |      |     |  |

|           | Min         | Тур  | Max |  |

| W         | 0.2         | 0.25 | 0.3 |  |

| L         | 0.30        | 0.35 | 0.4 |  |

| е         |             | 0.5  |     |  |

| n         |             | 32   |     |  |

| D1        |             | 3.5  |     |  |

| E1        |             | 3.5  |     |  |

| SD        |             | 0.25 |     |  |

| SE        |             | 0.25 |     |  |

# 4.3 Thermal Specifications

The following table lists the thermal specifications of the PD69210 and PD69220.

**Table 4-3. Thermal Specifications**

| Thermal Resistance | Device  | Тур  | Units | Description                             |

|--------------------|---------|------|-------|-----------------------------------------|

| $\theta_{JA}$      | PD69210 | 40.9 | °C/W  | Junction-to-ambient thermal resistance. |

| $\theta_{JC}$      | PD69210 | 15.2 | °C/W  | Junction-to-case thermal resistance.    |

| $\theta_{JA}$      | PD69220 | 65.0 | °C/W  | Junction-to-ambient thermal resistance. |

| $\theta_{JC}$      | PD69220 | 21.5 | °C/W  | Junction-to-case thermal resistance.    |

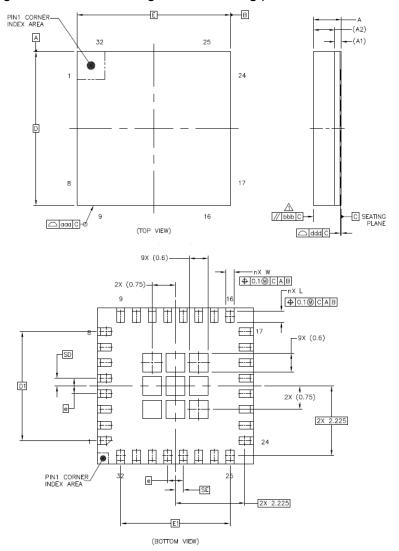

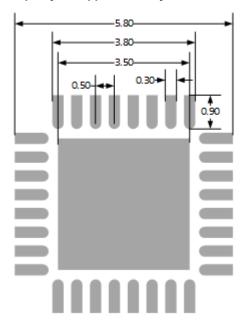

#### 4.4 Recommended PCB Layout

The following figures show the recommended PCB layout pattern for the 32-pin QFN 5 mm × 5 mm PD69210 and for the 32-pin LGA 5 mm × 5 mm PD69220. Units are in mm.

Figure 4-3. PD69210 and PD69220 Top-Layer Copper PCB Layout

The recommended solder paste stencil for the PD69220 is different than the recommended stencil for PD69200.

Figure 4-4. PD69210 Top-Layer Solder Paste and Vias PCB Layout for Thermal Pad Array

**Note:** The contract manufacturer has latitude to modify the solder paste stencil for manufacturability reasons. The solder paste stencil covers 65% to 80% of the thermal pad and must not allow solder to be applied to the thermal vias under the QFN package using any method they deem appropriate. Any design should be subject to system validation and qualification prior to commitment to mass production of field deployment. Use a 5 mil stencil.

Figure 4-5. PD69220 Top-Layer Solder Paste and Vias PCB Layout for Thermal Pad Array

**Note:** The contract manufacturer has latitude to modify the solder paste stencil for manufacturability reasons. The solder paste stencil covers 65% to 80% of the thermal pad and must not allow solder to be applied to the thermal vias under the QFN package using any method they deem appropriate. Any design should be subject to system validation and qualification prior to commitment to mass production of field deployment. Use a 5 mil stencil.

The PD69220 may be used on a PCB that was designed for the PD69200, that is the top layer copper for the two devices is identical. However, the recommended solder paste stencil for the PD69220 is different than the recommended stencil for PD69200. The recommended solder paste stencil for the PD69200 is identical to the PD69210 as shown in figure PD69210 Top-Layer Solder Paste and Vias PCB Layout for Thermal Pad Array. For more information, see the PD69200 Datasheet.

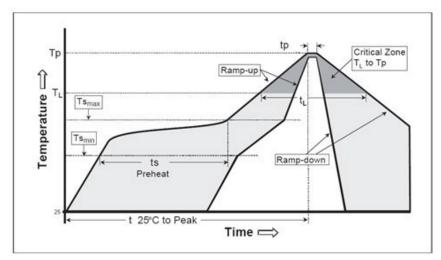

#### 4.5 Recommended Solder Reflow Information

RoHS 6/6

Pb-free 100% Matte Tin Finish

Package Peak Temperature for Solder Reflow (40 s maximum exposure)—260 °C (0 °C, -5 °C)

Table 4-4. Classification Reflow Profiles

| Profile Feature                                | Sn-Pb Eutectic Assembly | Pb-Free Assembly |

|------------------------------------------------|-------------------------|------------------|

| Average ramp-up rate (TS <sub>max</sub> to Tp) | 3 °C/second max         | 3 °C/second max  |

| Preheat                                        |                         |                  |

| Temperature min (TS <sub>min</sub> )           | 100 °C                  | 150 °C           |

| Temperature max (TS <sub>max</sub> )           | 150 °C                  | 200 °C           |

| Time (ts <sub>min</sub> to ts <sub>max</sub> ) | 60 s to 120 s           | 60 s to 180 s    |

| Time Maintained                                |                         |                  |

| Temperature (T <sub>L</sub> )                  | 183 °C                  | 217 °C           |

| Time (t <sub>L</sub> )                         | 60 s to 150 s           | 60 s to 150 s    |

| Peak classification temperature (TP)           | 210 °C to 235 °C        | 240 °C to 255 °C |

| continued                                        |                         |                  |  |  |

|--------------------------------------------------|-------------------------|------------------|--|--|

| Profile Feature                                  | Sn-Pb Eutectic Assembly | Pb-Free Assembly |  |  |

| Time within 5 °C of actual peak temperature (tp) | 10 s to 30 s            | 20 s to 40 s     |  |  |

| Ramp-down rate                                   | 6 °C/second max         | 6 °C/second max  |  |  |

| Time 25 °C to peak temperature                   | 6 minutes max           | 8 minutes max    |  |  |

Figure 4-6. Classification Reflow Profiles

Table 4-5. Pb-Free Process—Package Classification Reflow Temperatures

| Package Thickness                            | Volume <350 mm <sup>3</sup> | Volume 350–2000 mm <sup>3</sup> | Volume >2000 mm <sup>3</sup> |

|----------------------------------------------|-----------------------------|---------------------------------|------------------------------|

| Less than 1.6 mm <sup>1</sup>                | 260 + 0 °C                  | 260 + 0 °C                      | 260 + 0 °C                   |

| 1.6 mm to 2.5 mm <sup>1</sup>                | 260 + 0 °C                  | 250 + 0 °C                      | 245 + 0 °C                   |

| Greater than or equal to 2.5 mm <sup>1</sup> | 250 + 0 °C                  | 245 + 0 °C                      | 245 + 0 °C                   |

Tolerance: The device manufacturer or supplier should assure process compatibility up to and including the stated classification temperature, meaning that the Peak reflow temperature is +0 °C. For example, 260 °C to 0 °C, at the rated MSL value.

Note: Exceeding the ratings that are mentioned in the preceding table might cause damage to the device.

#### 4.6 Reference Documents

- IEEE Std 802.3-2018 Clause 33 Power over Ethernet over 2-Pair and Clause 145 Power over Ethernet

- PD69210 Communication Protocol User Guide

- AN3361 Designing an IEEE 802.3af/at/bt PoE System Based on PD692x0/PD69208.

- PD69208T4, PD69204T4, and PD69208M PoE PSE Manager Datasheet

- PD69200 PoE PSE Controller Datasheet

### 5. Ordering Information

The following table lists the part ordering information for PD69210 and PD69220 devices.

Table 5-1. Ordering Information

| Part Number                                                 | Package                                                           | Packaging<br>Type | Temperature     | Part Marking                                                                              | Tray Marking                                            |

|-------------------------------------------------------------|-------------------------------------------------------------------|-------------------|-----------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------|

| PD69210D <sup>1</sup> VVVV <sup>2</sup> SS <sup>3</sup>     | Plastic QFN<br>5 mm × 5 mm<br>(32 lead)                           | Tray              | –40 °C to 85 °C | Microchip Logo<br>PD69210<br>ARM Logo<br>YY <sup>4</sup> WW <sup>5</sup> NNN <sup>6</sup> | PD69210D-<br>VVVVSS<br>PD-OOOOGabb <sup>7</sup><br>YYWW |

| PD69210D <sup>1</sup> VVVV <sup>2</sup> SS <sup>3</sup> -TR | Plastic QFN<br>5 mm × 5 mm<br>(32 lead)                           | Tape and reel     | -40 °C to 85 °C | Microchip Logo<br>PD69210<br>ARM Logo<br>YY <sup>4</sup> WW <sup>5</sup> NNN <sup>6</sup> |                                                         |

| PD69220D <sup>1</sup> VVVV <sup>2</sup> SS <sup>3</sup>     | Plastic QFN<br>Laminated <sup>8</sup><br>5 mm × 5 mm<br>(32 lead) | Tray              | –40 °C to 85 °C | Microchip Logo<br>PD69220<br>ARM Logo<br>YY <sup>4</sup> WW <sup>5</sup> NNN <sup>6</sup> | PD69220D-<br>VVVVSS<br>PD-OOOOGabb <sup>7</sup><br>YYWW |

| PD69220D <sup>1</sup> VVVV <sup>2</sup> SS <sup>3</sup> -TR | Plastic QFN<br>Laminated <sup>8</sup><br>5 mm × 5 mm<br>(32 lead) | Tape and reel     | –40 °C to 85 °C | Microchip Logo<br>PD69220<br>ARM Logo<br>YY <sup>4</sup> WW <sup>5</sup> NNN <sup>6</sup> |                                                         |

- 1. D is detection method.

- C= IEEE 802.3 and pre-standard

- R= IEEE 802.3 only

- 2. VVVV is firmware revision.

- 3. SS is firmware parameters options.

- 4. Year code (last two digits of calendar year).

- 5. Week code (week of January 1 is week 01).

- 6. Alphanumeric trace code.

- 7. Operational part number.

- 8. Laminated QFN is also called a Land Grid Array (LGA).

The firmware release note has all required information about how to specify the choice of VVVV and SS. Find the Firmware Release Notes in the Microchip Software Libraries, and register to My Microchip account to access the release notes.

**Note:** The package meets RoHS, Pb-free of the European Council to minimize the environmental impact of electrical equipment.

**Note:** Initial burning of controller's firmware is performed in the factory. Firmware upgrades can be performed by users using the communication interface. For more information, see TN-140 (Catalog Number: 06-0024-081).

# 6. Revision History

| Revision | Date    | Section | Description                                                                                                                                                                                                                                                                                                     |

|----------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | 03/2020 |         | This is the initial issue of this document. The PD69220 PoE PSE controller is a new product offering and has not been previously described in any other document. The PD69210 PoE PSE controller was previously described in the following documents:                                                           |

|          |         |         | <ul> <li>PD69208T4 and PD69210 Datasheet (Revision 3 September 2019 Document Number PD-000357193)</li> <li>PD69204T4 and PD69210 Datasheet (Revision 3 September 2019 Document Number PD-000359832)</li> <li>PD69208M and PD69210 Datasheet (Revision 3 September 2019 Document Number PD-000359833)</li> </ul> |

## The Microchip Website

Microchip provides online support via our website at <a href="http://www.microchip.com/">http://www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to http://www.microchip.com/pcn and follow the registration instructions.

### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: http://www.microchip.com/support

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these

methods, to our knowledge, require using the Microchip products in a manner outside the operating

specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of

intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

### **Legal Notice**

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-5722-0

### **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit http://www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                         | ASIA/PACIFIC                             | ASIA/PACIFIC            | EUROPE                |

|----------------------------------|------------------------------------------|-------------------------|-----------------------|

| Corporate Office                 | Australia - Sydney                       | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.         | Tel: 61-2-9868-6733                      | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199          | China - Beijing                          | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200                | Tel: 86-10-8569-7000                     | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277                | China - Chengdu                          | India - Pune            | Tel: 45-4485-5910     |

| Technical Support:               | Tel: 86-28-8665-5511                     | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| http://www.microchip.com/support | China - Chongqing                        | Japan - Osaka           | Finland - Espoo       |

| Web Address:                     | Tel: 86-23-8980-9588                     | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| http://www.microchip.com         | China - Dongguan                         | Japan - Tokyo           | France - Paris        |

| Atlanta                          | Tel: 86-769-8702-9880                    | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                       | China - Guangzhou                        | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614                | Tel: 86-20-8755-8029                     | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455                | China - Hangzhou                         | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                       | Tel: 86-571-8792-8115                    | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370                | China - Hong Kong SAR                    | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                           | Tel: 852-2943-5100                       | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA                  | China - Nanjing                          | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087                | Tel: 86-25-8473-2460                     | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088                | China - Qingdao                          | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                          | Tel: 86-532-8502-7355                    | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                       | China - Shanghai                         | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071                | Tel: 86-21-3326-8000                     | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075                |                                          | Taiwan - Hsin Chu       |                       |

| Dallas                           | China - Shenyang<br>Tel: 86-24-2334-2829 |                         | Germany - Rosenheim   |

|                                  | China - Shenzhen                         | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX                      |                                          | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423                | Tel: 86-755-8864-2200                    | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924                | China - Suzhou                           | Taiwan - Taipei         | Italy - Milan         |

| Detroit                          | Tel: 86-186-6233-1526                    | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                         | China - Wuhan                            | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000                | Tel: 86-27-5980-5300                     | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX                      | China - Xian                             | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983                | Tel: 86-29-8833-7252                     | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis                     | China - Xiamen                           |                         | Tel: 31-416-690399    |

| Noblesville, IN                  | Tel: 86-592-2388138                      |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323                | China - Zhuhai                           |                         | Norway - Trondheim    |

| Fax: 317-773-5453                | Tel: 86-756-3210040                      |                         | Tel: 47-72884388      |

| Tel: 317-536-2380                |                                          |                         | Poland - Warsaw       |

| Los Angeles                      |                                          |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA                |                                          |                         | Romania - Bucharest   |

| Tel: 949-462-9523                |                                          |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608                |                                          |                         | Spain - Madrid        |

| Tel: 951-273-7800                |                                          |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC                      |                                          |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510                |                                          |                         | Sweden - Gothenberg   |

| New York, NY                     |                                          |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000                |                                          |                         | Sweden - Stockholm    |

| San Jose, CA                     |                                          |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110                |                                          |                         | UK - Wokingham        |

| Tel: 408-436-4270                |                                          |                         | Tel: 44-118-921-5800  |

| Canada - Toronto                 |                                          |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980                |                                          |                         |                       |

| Fax: 905-695-2078                |                                          |                         |                       |