## SURFACE MOUNT SILICON CURRENT LIMITING DIODES

www.centralsemi.com

### **DESCRIPTION:**

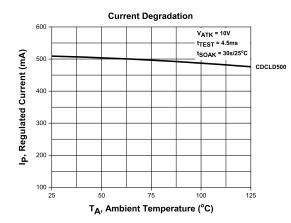

The CENTRAL SEMICONDUCTOR CDCLD200, CDCLD400, and CDCLD500 are Current Limiting Diodes (CLDs) specifically designed for applications requiring a constant current over a wide voltage range. The series is designed with a unique process that holds regulator current constant over temperature excursions (zero temperature coefficient). The devices are available in the thermally efficient DPAK package outline.

MARKING: FULL PART NUMBER

#### **FEATURES:**

- · Zero temperature coefficient

- · High regulator currents available

- · Industry standard thermally efficient DPAK

MAXIMUM RATINGS: (T<sub>A</sub>=25°C unless otherwise noted)

| , A                                               | SYMBOL                            | CDCLD200 | CDCLD400    | CDCLD500 | UNITS |

|---------------------------------------------------|-----------------------------------|----------|-------------|----------|-------|

| Peak Operating Voltage                            | Pov                               | 27       | 13.5        | 10.8     | V     |

| Peak Operating Voltage (T <sub>C</sub> =35°C)     | Pov                               |          | 50          |          | V     |

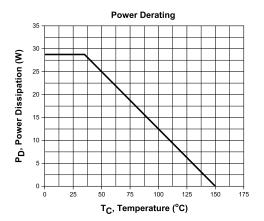

| Power Dissipation (Note 1)                        | $P_{D}$                           |          | 6.25        |          | W     |

| Power Dissipation (T <sub>C</sub> =35°C) (Note 1) | $P_{D}$                           |          | 28.75       |          | W     |

| Thermal Resistance                                | $\Theta$ JC                       |          | 4.0         |          | °C/W  |

| Operating and Storage Junction Temperature        | T <sub>J</sub> , T <sub>stg</sub> |          | -55 to +150 |          | °C    |

Note 1: Mounted on 900mm<sup>2</sup> 4-layer PCB with 2-ounce copper traces.

## ELECTRICAL CHARACTERISTICS: (TA=25°C)

| Туре     |           | Maximum Limiting Voltage (tp=5.0ms) VL @ 0.8 x Ip MIN |           |     |

|----------|-----------|-------------------------------------------------------|-----------|-----|

|          | MIN<br>mA | NOM<br>mA                                             | MAX<br>mA | V   |

| CDCLD200 | 170       | 200                                                   | 230       | 2.0 |

| CDCLD400 | 340       | 400                                                   | 460       | 2.0 |

| CDCLD500 | 425       | 500                                                   | 575       | 2.0 |

## SURFACE MOUNT SILICON **CURRENT LIMITING DIODES**

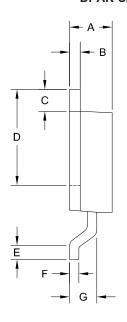

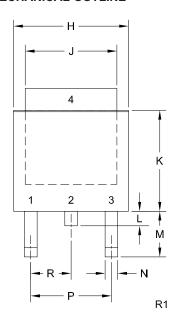

## **DPAK CASE - MECHANICAL OUTLINE**

# **LEAD CODE:**1) Cathode

- 2) Anode

- 3) No Connection

- 4) Anode

Pin 2 is common to the tab (4)

#### MARKING: FULL PART NUMBER

| DIMENSIONS |        |       |             |      |  |  |  |

|------------|--------|-------|-------------|------|--|--|--|

|            | INCHES |       | MILLIMETERS |      |  |  |  |

| SYMBOL     | MIN    | MAX   | MIN         | MAX  |  |  |  |

| Α          | 0.083  | 0.108 | 2.10        | 2.75 |  |  |  |

| В          | 0.016  | 0.032 | 0.40        | 0.81 |  |  |  |

| С          | 0.035  | 0.063 | 0.89        | 1.60 |  |  |  |

| D          | 0.203  | 0.228 | 5.15        | 5.79 |  |  |  |

| E          | 0.020  | -     | 0.51        | -    |  |  |  |

| F          | 0.016  | 0.024 | 0.40        | 0.60 |  |  |  |

| G          | 0.051  | 0.071 | 1.30        | 1.80 |  |  |  |

| Н          | 0.248  | 0.268 | 6.30        | 6.81 |  |  |  |

| J          | 0.197  | 0.217 | 5.00        | 5.50 |  |  |  |

| K          | 0.209  | 0.245 | 5.30        | 6.22 |  |  |  |

| L          | 0.025  | 0.040 | 0.64        | 1.02 |  |  |  |

| М          | 0.090  | 0.115 | 2.30        | 2.91 |  |  |  |

| N          | 0.012  | 0.045 | 0.30        | 1.14 |  |  |  |

| Р          | 0.180  |       | 4.60        |      |  |  |  |

| R          | 0.090  |       | 2.30        |      |  |  |  |

DPAK (REV: R1)

R4 (1-April 2021)

## SURFACE MOUNT SILICON CURRENT LIMITING DIODES

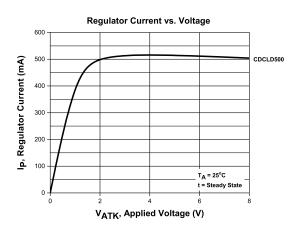

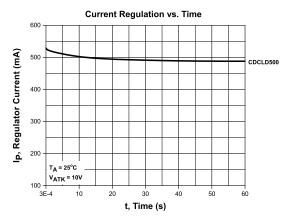

### TYPICAL ELECTRICAL CHARACTERISTICS

#### **TYPICAL APPLICATIONS**

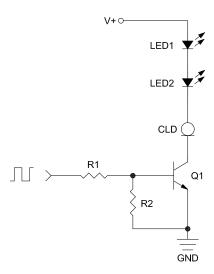

**Figure 1.** CLDs can be used to limit the current flowing through LED strings. Their dynamic performance make them an excellent replacement for current limiting resistors, as they allow for continuous current regulation regardless of input voltage. LED strings like this are commonly used in dimming lighting systems. By using a PWM input to control the transistor, the LED luminosity can be controlled by extending or decreasing the pulse width, allowing for control over the brightness of the LED.

#### **TYPICAL APPLICATIONS**

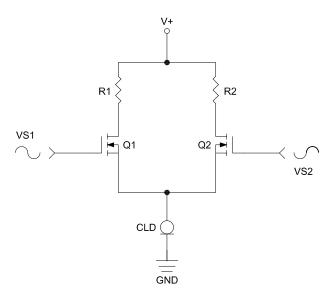

Figure 2. When designing differential amplifiers, it is essential to use a high impedance tail resistor to control both differential and common mode function. For differential signals, the tail resistor effectively splits the current amongst the transistors. This ensures proportional current increase and decrease between the transistors. The high impedance drives down the common mode gain and increases the common mode rejection ratio, thus yielding a more ideal amplifier. Ideally, an infinite impedance current source would be used in place of the tail resistor. While the ideal current source doesn't exist, CLDs serve as an excellent replacement for the tail resistor and also perform much like an active current source, both regulating the circuit to a constant current and presenting a large tail impedance. This yields a larger CMRR than using a high impedance tail resistor would.

#### **OUTSTANDING SUPPORT AND SUPERIOR SERVICES**

#### PRODUCT SUPPORT

Central's operations team provides the highest level of support to insure product is delivered on-time.

- Supply management (Customer portals)

- · Inventory bonding

- · Consolidated shipping options

- · Custom bar coding for shipments

- · Custom product packing

#### **DESIGNER SUPPORT/SERVICES**

Central's applications engineering team is ready to discuss your design challenges. Just ask.

- Free guick ship samples (2<sup>nd</sup> day air)

- Online technical data and parametric search

- SPICE models

- · Custom electrical curves

- · Environmental regulation compliance

- · Customer specific screening

- · Up-screening capabilities

- Special wafer diffusions

- PbSn plating options

- · Package details

- Application notes

- · Application and design sample kits

- Custom product and package development

#### REQUESTING PRODUCT PLATING

- 1. If requesting Tin/Lead plated devices, add the suffix "TIN/LEAD" to the part number when ordering (example: 2N2222A TIN/LEAD).

- 2. If requesting Lead (Pb) Free plated devices, add the suffix "PBFREE" to the part number when ordering (example: 2N2222A PBFREE).

#### **CONTACT US**

#### Corporate Headquarters & Customer Support Team

Central Semiconductor Corp. 145 Adams Avenue Hauppauge, NY 11788 USA

Main Tel: (631) 435-1110 Main Fax: (631) 435-1824

Support Team Fax: (631) 435-3388

www.centralsemi.com

Worldwide Field Representatives: <a href="https://www.centralsemi.com/wwreps">www.centralsemi.com/wwreps</a>

**Worldwide Distributors:**

www.centralsemi.com/wwdistributors

For the latest version of Central Semiconductor's **LIMITATIONS AND DAMAGES DISCLAIMER**, which is part of Central's Standard Terms and Conditions of sale, visit: <a href="https://www.centralsemi.com/terms">www.centralsemi.com/terms</a>

www.centralsemi.com (001)