# Multiple Range, 16-/12-Bit, Bipolar/Unipolar Voltage Output DACs with 2 ppm/°C Reference

**Data Sheet**

AD5761R/AD5721R

### **FEATURES**

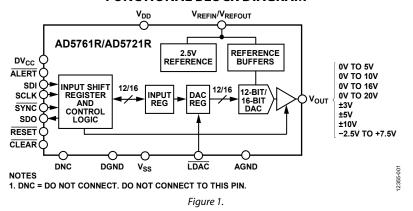

8 software-programmable output ranges: 0 V to +5 V, 0 V to +10 V, 0 V to +16 V, 0 V to +20 V,  $\pm3$  V,  $\pm5$  V,  $\pm10$  V, and -2.5 V

to +7.5 V; 5% overrange

Low drift 2.5 V reference: ±2 ppm/°C typical Total unadjusted error (TUE): 0.1% FSR maximum

16-bit resolution: ±2 LSB maximum INL Guaranteed monotonicity: ±1 LSB maximum

Single channel, 16-/12-bit DACs Settling time: 7.5 µs typical Integrated reference buffers

Low noise: 35 nV/√Hz

Low glitch: 1 nV-sec (0 V to 5 V range)

1.7 V to 5.5 V digital supply range

Asynchronous updating via LDAC

Asynchronous RESET to zero scale/midscale DSP-/microcontroller-compatible serial interface

**Robust 4 kV HBM ESD rating**

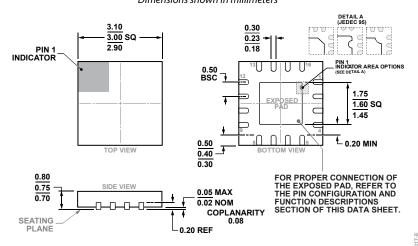

16-lead, 3 mm × 3 mm LFCSP package

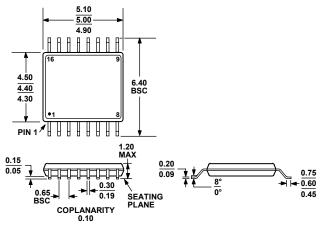

16-lead TSSOP package

Operating temperature range: -40°C to +125°C

# **APPLICATIONS**

Industrial automation

Instrumentation, data acquisition

Open-/closed-loop servo control, process control

Programmable logic controllers

#### **GENERAL DESCRIPTION**

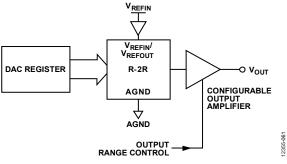

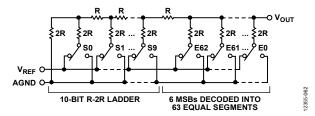

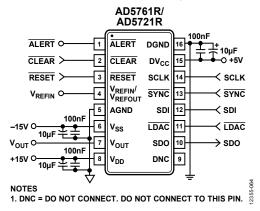

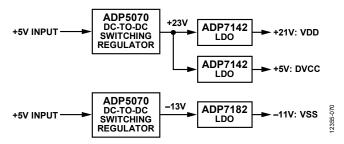

The AD5761R/AD5721R are single channel, 16-/12-bit serial input, voltage output, digital-to-analog converters (DACs). They operate from single supply voltages from +4.75 V to +30 V or dual supply voltages from –16.5 V to 0 V Vss and +4.75 V to +16.5 V Vdd. The integrated output amplifier, reference buffer, and reference provide a very easy to use, universal solution.

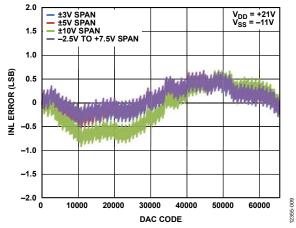

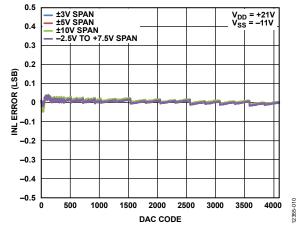

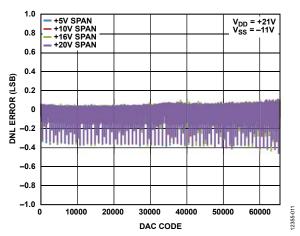

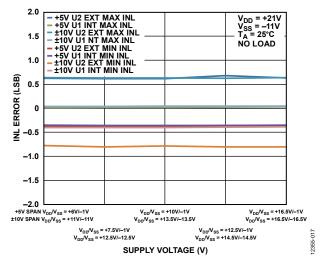

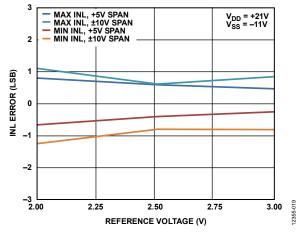

The devices offer guaranteed monotonicity, integral nonlinearity (INL) of  $\pm 2$  LSB maximum, 35 nV/ $\sqrt{Hz}$  noise, and 7.5  $\mu$ s settling time on selected ranges.

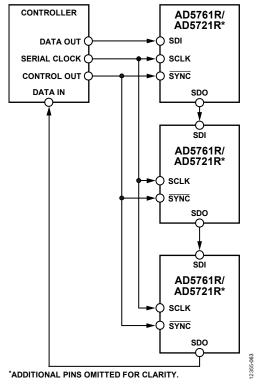

The AD5761R/AD5721R use a serial interface that operates at clock rates of up to 50 MHz and are compatible with DSP and microcontroller interface standards. Double buffering allows the asynchronous updating of the DAC output. The input coding is user-selectable twos complement or straight binary. The asynchronous reset function resets all registers to their default state. The output range is user selectable, via the RA[2:0] bits in the control register.

The devices available in a 3 mm  $\times$  3 mm LFCSP package and a 16-lead TSSOP package offer guaranteed specifications over the  $-40^{\circ}$ C to  $+125^{\circ}$ C industrial temperature range.

# **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                         | Thermal Hysteresis                                        | 27  |

|--------------------------------------------------|-----------------------------------------------------------|-----|

| Applications1                                    | Register Details                                          | 28  |

| General Description                              | Input Shift Register                                      | 28  |

| Functional Block Diagram 1                       | Control Register                                          | 29  |

| Revision History                                 | Readback Control Register                                 |     |

| Specifications                                   | Update DAC Register from Input Register                   | 31  |

| AC Performance Characteristics                   | Readback DAC Register                                     |     |

| Timing Characteristics                           | Write and Update DAC Register                             |     |

| Timing Diagrams                                  | Readback Input Register                                   |     |

| Absolute Maximum Ratings                         | Disable Daisy-Chain Functionality                         |     |

| ESD Caution                                      | Software Data Reset                                       |     |

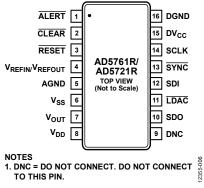

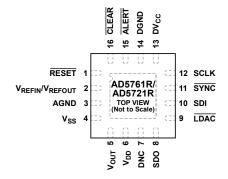

| Pin Configurations and Function Descriptions     |                                                           |     |

| -                                                | Software Full Reset                                       |     |

| Typical Performance Characterstics               | No Operation Registers                                    |     |

| Terminology                                      | Applications Information                                  |     |

| Theory of Operation                              | Typical Operating Circuit                                 |     |

| Digital-to-Analog Converter25                    | Power Supply Considerations                               | 34  |

| Transfer Function                                | Evaluation Board                                          | 34  |

| DAC Architecture                                 | Outline Dimensions                                        | 35  |

| Serial Interface                                 | Ordering Guide                                            | 36  |

| Hardware Control Pins26                          |                                                           |     |

| REVISION HISTORY                                 |                                                           |     |

| 1/2018—Rev. B to Rev. C                          | Changes to Figure 35                                      | 16  |

| Changes to Transfer Function Section             | Changes to Figure 37                                      |     |

| Moved DAC Output Amplifier Section26             | Changes to Figure 50                                      | 19  |

| Change to DB[15:11] Column, Table 11 and RA[2:0] | Changes to Figure 58 to Figure 60                         |     |

| Description Column, Table 1229                   | Changes to Figure 61 to Figure 66                         |     |

| Change to DB[15:13] Column, Table 15             | Changes to Figure 69                                      |     |

| Updated Outline Dimensions                       | Added Figure 71                                           |     |

| Moved Ordering Guide Section                     | Changes to Terminology Section                            |     |

| Changes to Ordering Guide                        | Changes to Digital-to-Analog Converter Section and Inter- |     |

| 10/2016 B A C B B                                | Reference Section                                         |     |

| 10/2016—Rev. A to Rev. B                         | Changes to Asynchronous Clear Function (CLEAR) Section .  |     |

| Changes to Features Section                      | Changes to Table 12                                       | 29  |

| 5/2015 Pay 0 to Pay A                            | Changes to Power Supply Considerations Section and        | 2.4 |

| 5/2015—Rev. 0 to Rev. A Added LFCSP Package      | Figure 77                                                 |     |

| Changes to Table 1                               | Added Figure 79                                           |     |

|                                                  | Updated Outline Dimensions                                |     |

| Changes to Table 4                               | Changes to Ordering Guide                                 | 35  |

| Changes to Table 4                               | 11/2014 Devision 0. In:t:-1 V:                            |     |

| Changes to Figure 21 to Figure 2414              | 11/2014—Revision 0: Initial Version                       |     |

| Changes to rigure 21 to rigure 21                |                                                           |     |

# **SPECIFICATIONS**

$V_{\mathrm{DD}}{}^{1} = 4.75 \ V \ to \ 30 \ V, V_{\mathrm{SS}}{}^{1} = -16.5 \ V \ to \ 0 \ V, \ AGND = DGND = 0 \ V, \ V_{\mathrm{REFIN}}/V_{\mathrm{REFOUT}} = 2.5 \ V \ external, \ DV_{\mathrm{CC}} = 1.7 \ V \ to \ 5.5 \ V, \ R_{\mathrm{LOAD}} = 1 \ k\Omega$  for all ranges except 0 V to 16 V and 0 V to 20 V for which  $R_{\mathrm{LOAD}} = 2 \ k\Omega$ ,  $C_{\mathrm{LOAD}} = 200 \ pF$ , all specifications  $T_{\mathrm{MIN}}$  to  $T_{\mathrm{MAX}}$ , unless otherwise noted.

Table 1.

| Parameter <sup>2</sup>                                  | Min       | Тур | Max  | Unit  | Test Conditions/Comments                                                                                         |

|---------------------------------------------------------|-----------|-----|------|-------|------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                      |           |     |      |       | External reference <sup>3</sup> and internal reference, outputs                                                  |

|                                                         |           |     | _    |       | unloaded                                                                                                         |

| Programmable Output Ranges                              | 0         |     | 5    | V     |                                                                                                                  |

|                                                         | 0         |     | 10   | V     |                                                                                                                  |

|                                                         | 0         |     | 16   | V     |                                                                                                                  |

|                                                         | 0         |     | 20   | V     |                                                                                                                  |

|                                                         | -2.5      |     | +7.5 | V     |                                                                                                                  |

|                                                         | -3        |     | +3   | V     |                                                                                                                  |

|                                                         | -5        |     | +5   | V     |                                                                                                                  |

|                                                         | -10       |     | +10  | V     |                                                                                                                  |

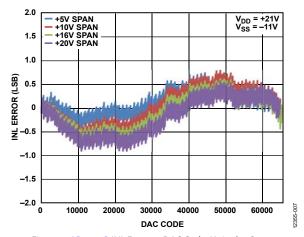

| AD5761R                                                 |           |     |      |       |                                                                                                                  |

| Resolution                                              | 16        |     |      | Bits  |                                                                                                                  |

| Relative Accuracy, INL                                  |           |     | _    |       |                                                                                                                  |

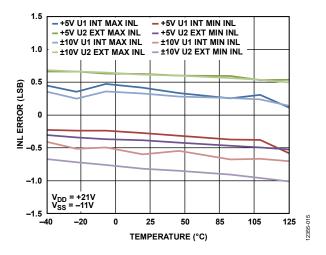

| A Grade                                                 | -8        |     | +8   | LSB   | External reference <sup>3</sup> and internal reference                                                           |

| B Grade⁴                                                | -2        |     | +2   | LSB   | All ranges except 0 V to 16 V and 0 V to 20 V,<br>$V_{REFIN}/V_{REFOUT} = 2.5 V$ external and internal reference |

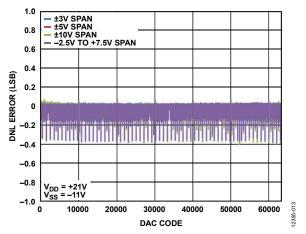

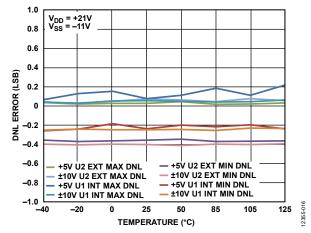

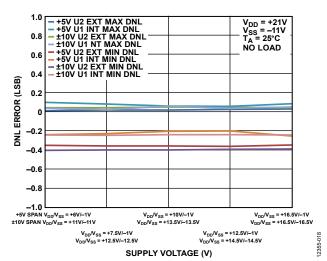

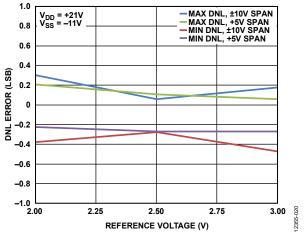

| Differential Nonlinearity, DNL                          | -1        |     | +1   | LSB   |                                                                                                                  |

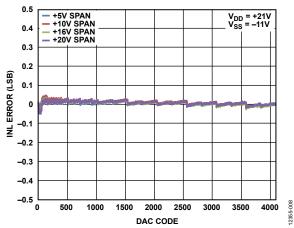

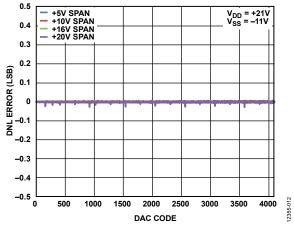

| AD5721R                                                 |           |     |      |       |                                                                                                                  |

| Resolution                                              | 12        |     |      | Bits  |                                                                                                                  |

| Relative Accuracy, INL                                  |           |     |      |       |                                                                                                                  |

| B Grade                                                 | -0.5      |     | +0.5 | LSB   | External reference <sup>3</sup> and internal reference                                                           |

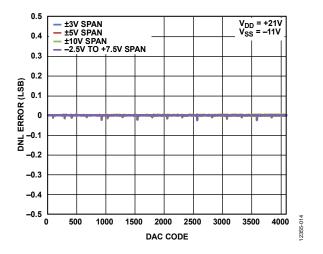

| Differential Nonlinearity, DNL                          | -0.5      |     | +0.5 | LSB   |                                                                                                                  |

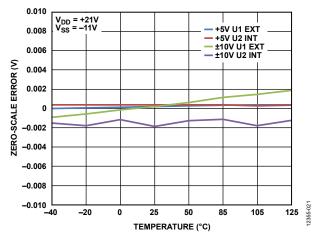

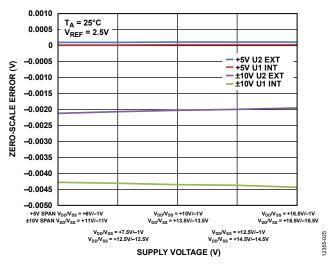

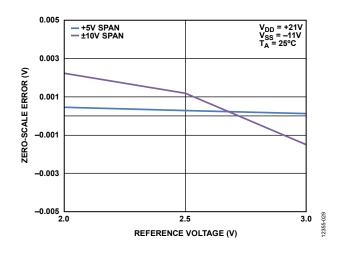

| Zero-Scale Error                                        | -6        |     | +6   | mV    | All ranges except ±10 V and 0 V to 20 V, external reference <sup>3</sup>                                         |

|                                                         | -10       |     | +10  | mV    | 0 V to 20 V, ±10 V ranges, external reference <sup>3</sup>                                                       |

|                                                         | -6        |     | +6   | mV    | All ranges except $\pm 5$ V, $\pm 10$ V and 0 V to 20 V, internal reference                                      |

|                                                         | -8        |     | +8   | mV    | ±5 V range, internal reference                                                                                   |

|                                                         | -9        |     | +9   | mV    | 0 V to 20 V range, internal reference                                                                            |

|                                                         | -13       |     | +13  | mV    | ±10 V range, internal reference                                                                                  |

| Zero-Scale Temperature<br>Coefficient (TC) <sup>5</sup> |           | ±5  |      | μV/°C | Unipolar ranges, external reference <sup>3</sup> and internal reference                                          |

|                                                         |           | ±15 |      | μV/°C | Bipolar ranges, external reference <sup>3</sup> and internal reference                                           |

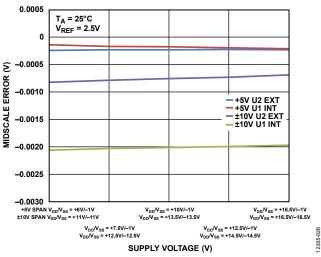

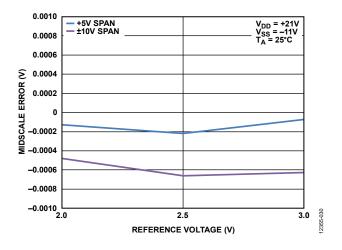

| Bipolar Zero Error                                      | -5        |     | +5   | mV    | All bipolar ranges except ±10 V                                                                                  |

|                                                         | <b>-7</b> |     | +7   | mV    | ±10 V output range                                                                                               |

| Bipolar Zero TC <sup>5</sup>                            |           | ±2  |      | μV/°C | ±3 V range, external reference <sup>3</sup> and internal reference                                               |

|                                                         |           | ±5  |      | μV/°C | All bipolar ranges except ±3 V range, external reference <sup>3</sup> and internal reference                     |

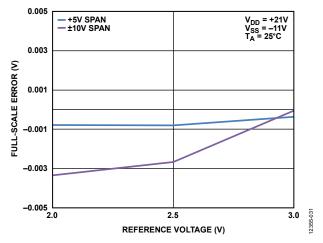

| Offset Error                                            | -6        |     | +6   | mV    | All ranges except ±10 V and 0 V to 20 V, external reference <sup>3</sup>                                         |

|                                                         | -10       |     | +10  | mV    | 0 V to 20 V, ±10 V ranges, external reference <sup>3</sup>                                                       |

|                                                         | -6        |     | +6   | mV    | All ranges except ±5 V, ±10 V, and 0 V to 20 V; internal reference                                               |

|                                                         | -8        |     | +8   | mV    | ±5 V range, internal reference                                                                                   |

|                                                         | <b>-9</b> |     | +9   | mV    | 0 V to 20 V range, internal reference                                                                            |

|                                                         | -13       |     | +13  | mV    | ±10 V range, internal reference                                                                                  |

| Parameter <sup>2</sup>                   | Min                  | Тур  | Max                  | Unit       | Test Conditions/Comments                                                                                                      |

|------------------------------------------|----------------------|------|----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------|

| Offset Error TC <sup>5</sup>             |                      | ±5   |                      | μV/°C      | Unipolar ranges, external reference <sup>3</sup> and internal reference                                                       |

|                                          |                      | ±15  |                      | μV/°C      | Bipolar ranges, external reference <sup>3</sup> and internal reference                                                        |

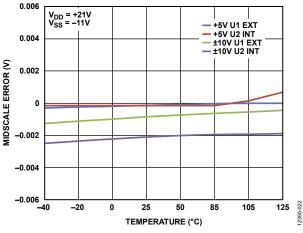

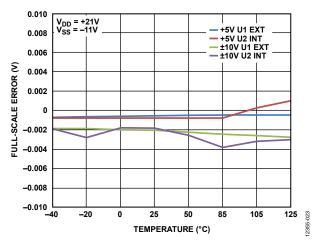

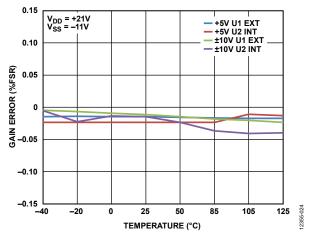

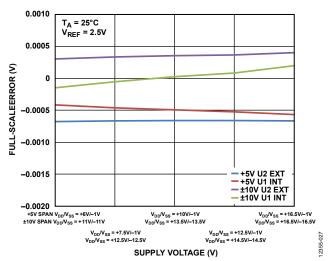

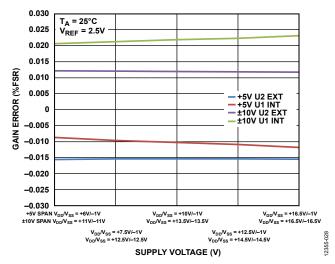

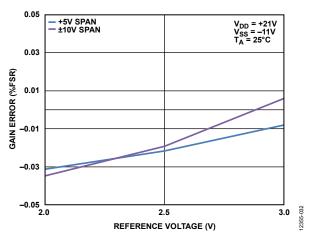

| Gain Error                               | -0.1                 |      | +0.1                 | % FSR      | External reference <sup>3</sup>                                                                                               |

|                                          | -0.15                |      | +0.15                | % FSR      | Internal reference                                                                                                            |

| Gain Error TC⁵                           |                      | ±1.5 |                      | ppm FSR/°C | External reference <sup>3</sup> and internal reference                                                                        |

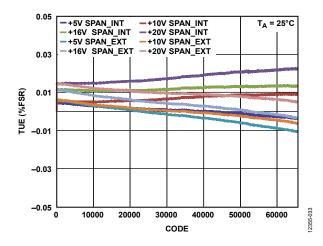

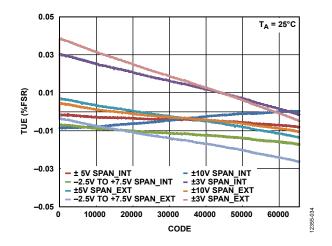

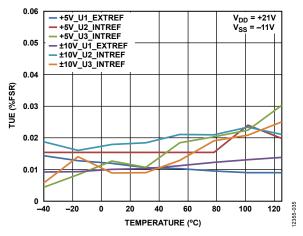

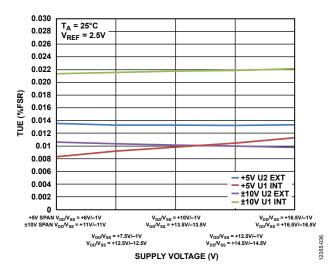

| TUE                                      | -0.1                 |      | +0.1                 | % FSR      | External reference <sup>3</sup>                                                                                               |

|                                          | -0.15                |      | +0.15                | % FSR      | Internal reference                                                                                                            |

| REFERENCE INPUT (EXTERNAL) <sup>5</sup>  |                      |      |                      |            |                                                                                                                               |

| Reference Input Voltage (VREF)           |                      | 2.5  |                      | V          | ±1% for specified performance                                                                                                 |

| Input Current                            | -2                   | ±0.5 | +2                   | μΑ         |                                                                                                                               |

| Reference Range                          | 2                    |      | 3                    | V          |                                                                                                                               |

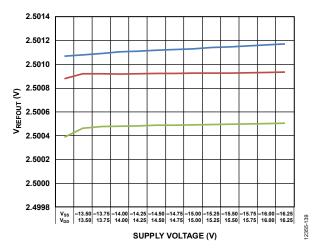

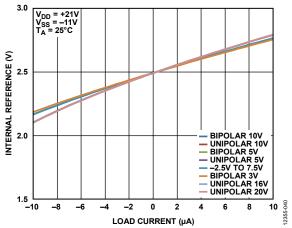

| REFERENCE OUTPUT (INTERNAL) <sup>5</sup> |                      |      |                      |            |                                                                                                                               |

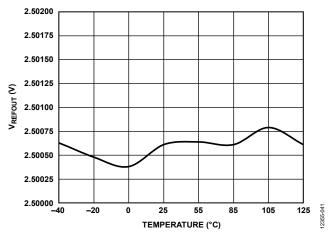

| Output Voltage                           |                      | 2.5  |                      | V          | ±3 mV, at ambient temperature                                                                                                 |

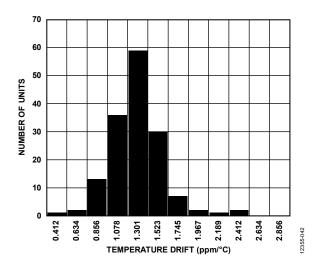

| Voltage Reference TC                     |                      | 2    | 5                    | ppm/°C     | ·                                                                                                                             |

| Output Impedance                         |                      | 25   |                      | kΩ         |                                                                                                                               |

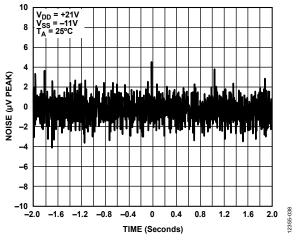

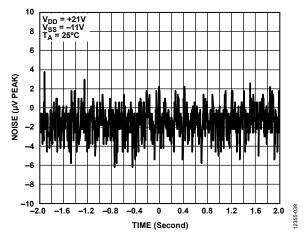

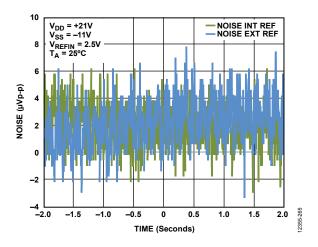

| Output Voltage Noise                     |                      | 6    |                      | μV p-p     | 0.1 Hz to 10 Hz                                                                                                               |

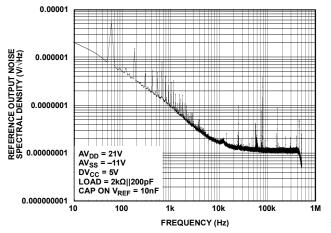

| Noise Spectral Density                   |                      | 10   |                      | nV/√Hz     | At ambient; f = 10 kHz                                                                                                        |

| Line Regulation                          |                      | 6    |                      | μV/V       | At ambient                                                                                                                    |

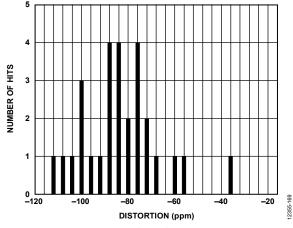

| Thermal Hysteresis                       |                      | 80   |                      | ppm        | First temperature cycle                                                                                                       |

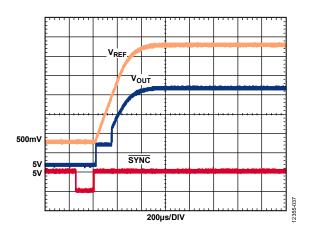

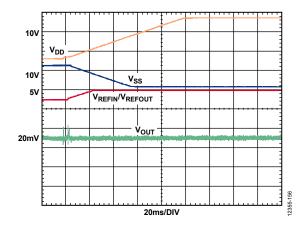

| Start-Up Time                            |                      | 3.5  |                      | ms         | Coming out of power-down mode with a 10 nF capacitor on the VREFIN/VREFOUT pin to improve noise performance; outputs unloaded |

| OUTPUT CHARACTERISTICS <sup>5</sup>      |                      |      |                      |            | performance, outputs unloaded                                                                                                 |

| Output Voltage Range                     | -V <sub>OUT</sub>    |      | +V <sub>OUT</sub>    |            | See Table 7 for the different output voltage ranges available                                                                 |

|                                          | -10                  |      | +10                  | V          | $V_{DD}/V_{SS} = \pm 11 \text{ V}, \pm 10 \text{ V}$ output range                                                             |

|                                          | -10.5                |      | +10.5                | V          | $V_{DD}/V_{SS} = \pm 11 \text{ V}, \pm 10 \text{ V}$ output range with 5% overrange                                           |

| Capacitive Load Stability                |                      |      | 1                    | nF         |                                                                                                                               |

| Headroom                                 |                      | 0.5  | 1                    | V          | $R_{LOAD} = 1 \text{ k}\Omega$ for all ranges except 0 V to 16 V and 0 V to 20 V ranges ( $R_{LOAD} = 2 \text{ k}\Omega$ )    |

| Output Voltage TC                        |                      | ±3   |                      | ppm FSR/°C | ±10 V range, external reference                                                                                               |

| Short-Circuit Current                    |                      | 25   |                      | mA         | Short on the V <sub>OUT</sub> pin                                                                                             |

| Resistive Load                           |                      |      | 1                    | kΩ         | All ranges except 0 V to 16 V and 0 V to 20 V                                                                                 |

|                                          |                      |      | 2                    | kΩ         | 0 V to 16 V, 0 V to 20 V ranges                                                                                               |

| Load Regulation                          |                      | 0.3  |                      | mV/mA      | Outputs unloaded                                                                                                              |

| DC Output Impedance                      |                      | 0.5  |                      | Ω          | Outputs unloaded                                                                                                              |

| LOGIC INPUTS⁵                            |                      |      |                      |            | $DV_{CC} = 1.7 \text{ V to } 5.5 \text{ V, JEDEC compliant}$                                                                  |

| Input Voltage                            |                      |      |                      |            |                                                                                                                               |

| High, V <sub>⊪</sub>                     | $0.7 \times DV_{CC}$ |      |                      | V          |                                                                                                                               |

| Low, V <sub>IL</sub>                     |                      |      | $0.3 \times DV_{CC}$ | V          |                                                                                                                               |

| Input Current                            |                      |      |                      |            |                                                                                                                               |

| Leakage Current                          | -1                   |      | +1                   | μΑ         | SDI, SCLK, SYNC                                                                                                               |

| -                                        | -1                   |      | +1                   | μΑ         | LDAC, CLEAR, RESET pins held high                                                                                             |

|                                          | -55                  |      |                      | μΑ         | LDAC, CLEAR, RESET pins held low                                                                                              |

|                                          | 1                    |      |                      | I          | ,, , p                                                                                                                        |

| Parameter <sup>2</sup>                     | Min                    | Тур   | Max | Unit | Test Conditions/Comments                                                                   |

|--------------------------------------------|------------------------|-------|-----|------|--------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (SDO, ALERT) <sup>5</sup>    |                        |       |     |      |                                                                                            |

| Output Voltage                             |                        |       |     |      |                                                                                            |

| Low, V <sub>OL</sub>                       |                        |       | 0.4 | V    | $DV_{CC} = 1.7 \text{ V to } 5.5 \text{ V, sinking } 200 \mu\text{A}$                      |

| High, V <sub>он</sub>                      | DV <sub>cc</sub> – 0.5 |       |     | V    | $DV_{CC} = 1.7 \text{ V}$ to 5.5 V, sourcing 200 $\mu$ A                                   |

| High Impedance, SDO Pin                    |                        |       |     |      |                                                                                            |

| Leakage Current                            | -1                     |       | +1  | μΑ   |                                                                                            |

| Pin Capacitance                            |                        | 5     |     | pF   |                                                                                            |

| POWER REQUIREMENTS                         |                        |       |     |      |                                                                                            |

| $V_{DD}$                                   | 4.75                   |       | 30  | V    |                                                                                            |

| V <sub>ss</sub>                            | -16.5                  |       | 0   | V    |                                                                                            |

| $DV_CC$                                    | 1.7                    |       | 5.5 | V    |                                                                                            |

| $I_{DD}$                                   |                        | 5.1   | 6.5 | mA   | Outputs unloaded, external reference                                                       |

| I <sub>SS</sub>                            |                        | 1     | 3   | mA   | Outputs unloaded                                                                           |

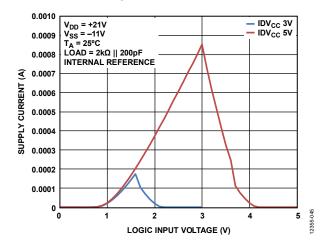

| Dlcc                                       |                        | 0.005 | 1   | μΑ   | $V_{IH} = DV_{CC}$ , $V_{IL} = DGND$                                                       |

| Power Dissipation                          |                        | 67.1  |     | mW   | ±11 V operation, outputs unloaded, TSSOP package                                           |

| DC Power Supply Rejection<br>Ratio (PSRR)⁵ |                        | 0.1   |     | mV/V | $V_{DD} \pm 10\%$ , $V_{SS} = -15 \text{ V}$                                               |

|                                            |                        | 0.1   |     | mV/V | $V_{SS} \pm 10\%$ , $V_{DD} = +15 \text{ V}$                                               |

| AC PSRR⁵                                   |                        | 65    |     | dB   | $V_{DD}$ ±200 mV, 50 Hz/60 Hz, $V_{SS}$ = -15 V, internal reference, $C_{LOAD}$ = 100 nF   |

|                                            |                        | 65    |     | dB   | $V_{SS}$ ±200 mV, 50 Hz/60 Hz, $V_{DD}$ = +15 V, internal reference, $C_{LOAD}$ = 100 nF   |

|                                            |                        | 80    |     | dB   | $V_{DD}$ ±200 mV, 50 Hz/60 Hz, $V_{SS}$ = -15 V, external reference, $C_{LOAD}$ = unloaded |

|                                            |                        | 80    |     | dB   | $V_{SS}$ ±200 mV, 50 Hz/60 Hz, $V_{DD}$ = +15 V, external reference, $C_{LOAD}$ = unloaded |

<sup>&</sup>lt;sup>1</sup> For specified performance, headroom requirement is 1 V.

<sup>2</sup> Temperature range: -40°C to +125°C, typical at +25°C.

<sup>3</sup> External reference means 2 V to 2.85 V with overrange and 2 V to 3 V without overrange.

<sup>4</sup> Integral nonlinearity error is specified at ±4 LSB (min/max) for 16 V and 20 V ranges with V<sub>REFIN</sub>/V<sub>REFOUT</sub> = 2.5 V external and internal, and for all ranges with V<sub>REFIN</sub>/V<sub>REFOUT</sub> = 2 V to 2.85 V with overrange and 2 V to 3 V without overrange.

<sup>5</sup> Guaranteed by design and characterization, not production tested.

# **AC PERFORMANCE CHARACTERISTICS**

$V_{DD}{}^{1}=4.75~V~to~30~V, V_{SS}{}^{1}=-16.5~V~to~0~V, AGND=DGND=0~V, V_{REFIN}/V_{REFOUT}=2.5~V~external, DV_{CC}=1.7~V~to~5.5~V, R_{LOAD}=1~k\Omega~for~all~ranges~except~0~V~to~16~V~and~0~V~to~20~V~for~which~R_{LOAD}=2~k\Omega, C_{LOAD}=200~pF, all~specifications~T_{MIN}~to~T_{MAX}, unless otherwise noted.$

Table 2.

| Parameter <sup>2</sup>                          | Min | Тур | Max  | Unit   | Test Conditions/Comments                                                              |

|-------------------------------------------------|-----|-----|------|--------|---------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE <sup>3</sup>                |     |     |      |        |                                                                                       |

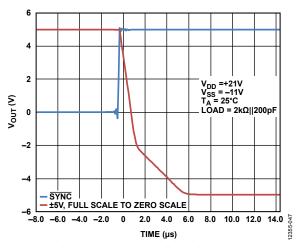

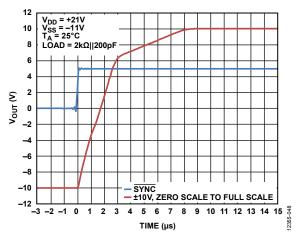

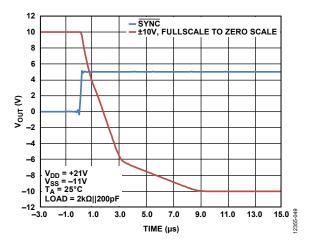

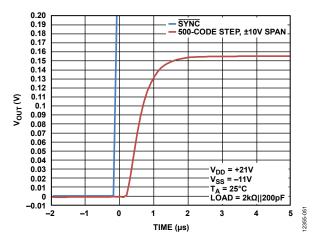

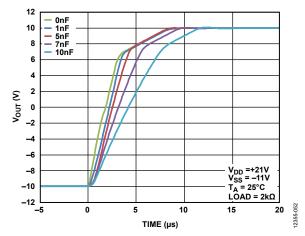

| Output Voltage Settling Time                    |     | 9   | 12.5 | μs     | 20 V step to 1 LSB at 16-bit resolution                                               |

|                                                 |     | 7.5 | 8.5  | μs     | 10 V step to 1 LSB at 16-bit resolution                                               |

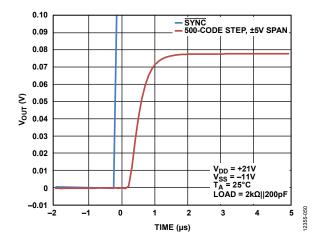

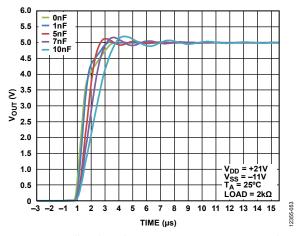

|                                                 |     |     | 5    | μs     | 512 LSB step to 1 LSB at 16-bit resolution                                            |

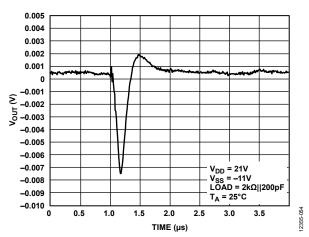

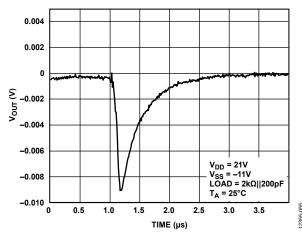

| Digital-to-Analog Glitch Impulse                |     | 8   |      | nV-sec | ±10 V range                                                                           |

|                                                 |     | 1   |      | nV-sec | 0 V to 5 V range                                                                      |

| Glitch Impulse Peak Amplitude                   |     | 15  |      | mV     | ±10 V range                                                                           |

|                                                 |     | 10  |      | mV     | 0 V to 5 V range                                                                      |

| Power-On Glitch                                 |     | 100 |      | mV p-p |                                                                                       |

| Digital Feedthrough                             |     | 0.6 |      | nV-sec |                                                                                       |

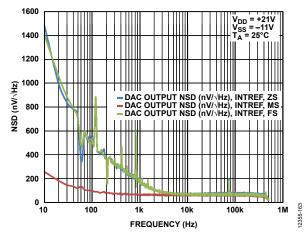

| Output Noise                                    |     |     |      |        |                                                                                       |

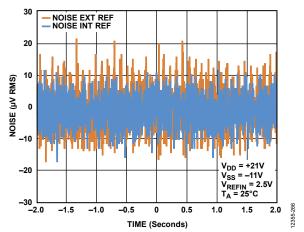

| 0.1 Hz to 10 Hz Bandwidth                       |     | 15  |      | μV p-p |                                                                                       |

| 100 kHz Bandwidth                               |     | 45  |      | μV rms | 0 V to 20 V and 0 V to 16 V ranges, 2.5 V external reference                          |

|                                                 |     | 35  |      | μV rms | 0 V to 10 V, $\pm$ 10 V, and $-2.5$ V to $\pm$ 7.5 V ranges, 2.5 V external reference |

|                                                 |     | 25  |      | μV rms | ±5 V range, 2.5 V external reference                                                  |

|                                                 |     | 15  |      | μV rms | 0 V to 5 V and ±3 V ranges, 2.5 V external reference                                  |

| Output Noise Spectral Density,<br>at 10 kHz     |     | 80  |      | nV/√Hz | ±10 V range, 2.5 V external reference                                                 |

|                                                 |     | 35  |      | nV/√Hz | ±3 V range, 2.5 V external reference                                                  |

|                                                 |     | 70  |      | nV/√Hz | $\pm 5$ V, 0 V to 10 V, and $-2.5$ V to $+7.5$ V ranges, 2.5 V external reference     |

|                                                 |     | 110 |      | nV/√Hz | 0 V to 20 V range, 2.5 V external reference                                           |

|                                                 |     | 90  |      | nV/√Hz | 0 V to 16 V range, 2.5 V external reference                                           |

|                                                 |     | 45  |      | nV/√Hz | 0 V to 5 V range, 2.5 V external reference                                            |

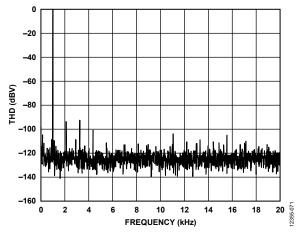

| Total Harmonic Distortion (THD) <sup>4</sup>    |     | -87 |      | dB     | 2.5 V external reference, 1 kHz tone                                                  |

| Signal-to-Noise Ratio (SNR)                     |     | 92  |      | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, f <sub>OUT</sub> = 1 kHz           |

| Peak Harmonic or Spurious<br>Noise (SFDR)       |     | 92  |      | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, f <sub>OUT</sub> = 1 kHz           |

| Signal-to-Noise-and-Distortion<br>(SINAD) Ratio |     | 85  |      | dB     | At ambient, 2.5 V external reference, BW = 20 kHz, f <sub>OUT</sub> = 1 kHz           |

<sup>&</sup>lt;sup>1</sup> For specified performance, headroom requirement is 1 V.

<sup>&</sup>lt;sup>2</sup> Temperature range: -40°C to +125°C, typical at +25°C.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>4</sup> Digitally generated sine wave at 1 kHz.

# **TIMING CHARACTERISTICS**

$DV_{\text{CC}}$  = 1.7 V to 5.5 V, all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}},$  unless otherwise noted.

Table 3.

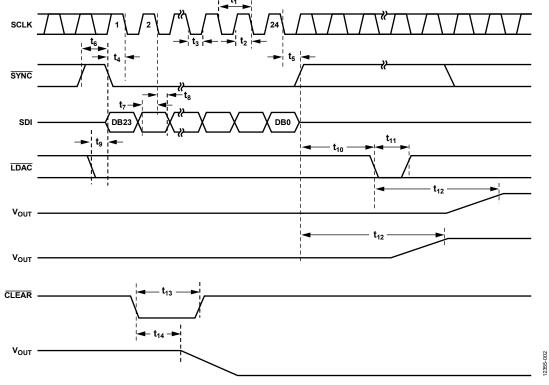

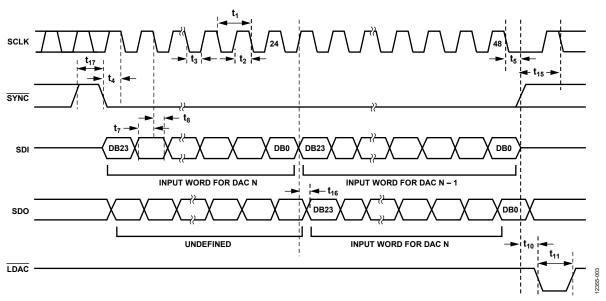

| Parameter             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                     |

|-----------------------|----------------------------------------------|--------|---------------------------------------------------------------------------------|

| t <sub>1</sub> 1      | 20                                           | ns min | SCLK cycle time                                                                 |

| $t_2$                 | 10                                           | ns min | SCLK high time                                                                  |

| t <sub>3</sub>        | 10                                           | ns min | SCLK low time                                                                   |

| t <sub>4</sub>        | 15                                           | ns min | SYNC falling edge to SCLK falling edge setup time                               |

| <b>t</b> <sub>5</sub> | 10                                           | ns min | SCLK falling edge to SYNC rising edge time                                      |

| <b>t</b> <sub>6</sub> | 20                                           | ns min | Minimum SYNC high time (write mode)                                             |

| <b>t</b> <sub>7</sub> | 5                                            | ns min | Data setup time                                                                 |

| t <sub>8</sub>        | 5                                            | ns min | Data hold time                                                                  |

| <b>t</b> 9            | 10                                           | ns min | LDAC falling edge to SYNC falling edge                                          |

| t <sub>10</sub>       | 20                                           | ns min | SYNC rising edge to LDAC falling edge                                           |

| t <sub>11</sub>       | 20                                           | ns min | LDAC pulse width low                                                            |

| t <sub>12</sub>       | 9                                            | μs typ | DAC output settling time, 20 V step to 1 LSB at 16-bit resolution (see Table 2) |

|                       | 7.5                                          | μs typ | DAC output settling time, 10 V step to 1 LSB at 16-bit resolution               |

| t <sub>13</sub>       | 20                                           | ns min | CLEAR pulse width low                                                           |

| t <sub>14</sub>       | 200                                          | ns typ | CLEAR pulse activation time                                                     |

| t <sub>15</sub>       | 10                                           | ns min | SYNC rising edge to SCLK falling edge                                           |

| t <sub>16</sub>       | 40                                           | ns max | SCLK rising edge to SDO valid ( $C_{L\_SDO}^2 = 15 \text{ pF}$ )                |

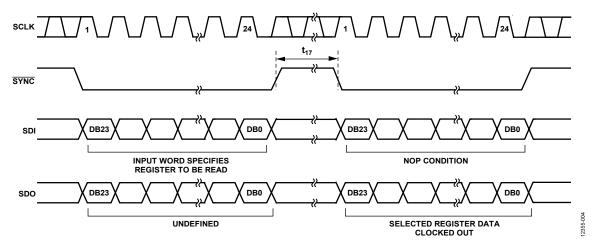

| t <sub>17</sub>       | 50                                           | ns min | Minimum SYNC high time (readback/daisy-chain mode)                              |

$<sup>^1</sup>$  Maximum SCLK frequency is 50 MHz for write mode and 33 MHz for readback mode.  $^2$  CL\_SDO is the capacitive load on the SDO output.

# **TIMING DIAGRAMS**

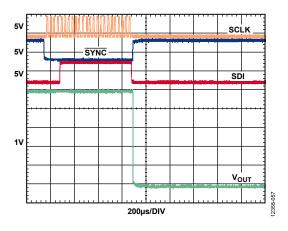

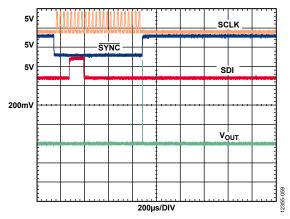

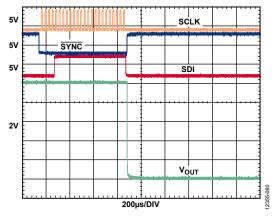

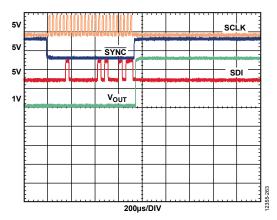

Figure 2. Serial Interface Timing Diagram

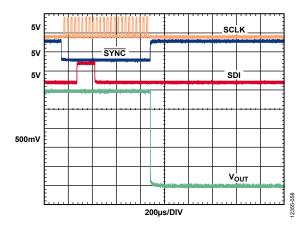

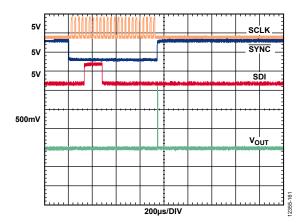

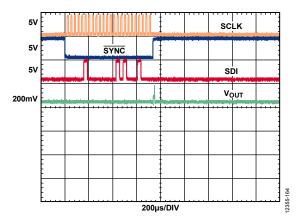

Figure 3. Daisy-Chain Timing Diagram

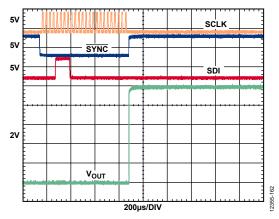

Figure 4. Readback Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted. Transient currents of up to 200 mA do not cause silicon controlled rectifier (SCR) latch-up.

Table 4

| ParameterRatingVDD to AGND-0.3 V to +34 VVSS to AGND+0.3 V to -17 VVDD to VSS-0.3 V to +34 VDVCC to DGND-0.3 V to +7 VDigital Inputs to DGND-0.3 V to DVCC + 0.3 V or 7 VDigital Outputs to DGND-0.3 V to DVCC + 0.3 V or 7 VVREFIN/VREFOUT tO DGND-0.3 V to +7 VVOUT tO AGND-0.3 V to +7 VAGND to DGND-0.3 V to +0.3 VOperating Temperature Range, TA Industrial-0.3 V to +0.3 VStorage Temperature Range-65°C to +150°CJunction Temperature, TJMAX150°C16-Lead TSSOP Package-65°C to +150°CθJC Thermal Impedance113°C/W¹16-Lead LFCSP Package-75°C/W¹θJC Thermal Impedance75°C/W¹Hormal Impedance4.5°C/W²Power Dissipation(TJMAX - TA)/θJALead TemperatureJEDEC industry standardSolderingJ-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 4.                                        |                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------|

| Vss to AGND VDD to Vss DVcc to DGND Digital Inputs to DGND Digital Outputs to DGND  VOUT to AGND AGND Tal Industrial Storage Temperature Range Junction Temperature, TJMAX 16-Lead TSSOP Package θJA Thermal Impedance θJC Thermal Impedance θJC Thermal Impedance θJC Thermal Impedance Power Dissipation Lead Temperature Soldering  +0.3 V to -17 V -0.3 V to +7 V (whichever is less) -0.3 V to DVcc + 0.3 V or 7 V (whichever is less) -0.3 V to +7 V Vout to AGND -0.3 V to +7 V Vout to +0.3 V -40°C to +125°C -65°C to +125°C -65°C to +150°C 150°C -65°C to +150°C -  | Parameter                                       | Rating                             |

| V <sub>DD</sub> to V <sub>SS</sub> DV <sub>CC</sub> to DGND  Digital Inputs to DGND  Digital Outputs to DGND  V <sub>REFIN</sub> /V <sub>REFOUT</sub> to DGND  V <sub>OUT</sub> to AGND  AGND to DGND  Operating Temperature Range, T <sub>A</sub> Industrial  Storage Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package  θ <sub>JA</sub> Thermal Impedance  θ <sub>JC</sub> Thermal Impedance                                                   | V <sub>DD</sub> to AGND                         | −0.3 V to +34 V                    |

| DVcc to DGND Digital Inputs to DGND Digital Outputs to DGND Digital Outputs to DGND Digital Outputs to DGND Digital Outputs to DGND  VREFIN/VREFOUT to DGND VOUT to AGND AGND to DGND Operating Temperature Range, Ta Industrial Storage Temperature, TJ MAX 16-Lead TSSOP Package  θJa Thermal Impedance θJc Thermal Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>ss</sub> to AGND                         | +0.3 V to -17 V                    |

| Digital Inputs to DGND  -0.3 V to DV <sub>CC</sub> + 0.3 V or 7 V (whichever is less)  Digital Outputs to DGND  -0.3 V to DV <sub>CC</sub> + 0.3 V or 7 V (whichever is less)  V <sub>REFIN</sub> /V <sub>REFOUT</sub> to DGND  V <sub>OUT</sub> to AGND  AGND to DGND  Operating Temperature Range, T <sub>A</sub> Industrial  Storage Temperature Range  Junction Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package  θ <sub>JA</sub> Thermal Impedance  θ <sub>JC</sub> Thermal Impedance  113°C/W¹  28°C/W  16-Lead LFCSP Package  θ <sub>JA</sub> Thermal Impedance  θ <sub>JC</sub> Thermal Impedance  γ <sub>S°</sub> C/W¹  4.5°C/W²  Power Dissipation  Lead Temperature  Soldering  J-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{DD}$ to $V_{SS}$                            | −0.3 V to +34 V                    |

| (whichever is less)  Digital Outputs to DGND  VREFIN/VREFOUT to DGND  VOUT to AGND  AGND to DGND  Operating Temperature Range, T <sub>A</sub> Industrial  Storage Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package  θ <sub>JA</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance η <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance η <sub>JC</sub> Thermal Impedance                                                               | DV <sub>cc</sub> to DGND                        | −0.3 V to +7 V                     |

| Whichever is less)  VREFIN/VREFOUT tO DGND  VOUT tO AGND  AGND to DGND  Operating Temperature Range, TA Industrial  Storage Temperature, TJ MAX  16-Lead TSSOP Package  θJA Thermal Impedance  θJC Thermal Impedance  θJA Thermal Impedance  θJA Thermal Impedance  θJA Thermal Impedance  θJC Thermal Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Digital Inputs to DGND                          |                                    |

| Vout to AGND AGND to DGND Operating Temperature Range, T <sub>A</sub> Industrial Storage Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package θ <sub>JA</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance η <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance η <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance                                                                                                                                                                                                                                                                                                                   | Digital Outputs to DGND                         |                                    |

| AGND to DGND  Operating Temperature Range, T <sub>A</sub> Industrial  Storage Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package Θ <sub>JA</sub> Thermal Impedance Θ <sub>JC</sub> Thermal Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>REFIN</sub> /V <sub>REFOUT</sub> to DGND | −0.3 V to +7 V                     |

| Operating Temperature Range, T <sub>A</sub> Industrial  Storage Temperature Range Junction Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package θ <sub>JA</sub> Thermal Impedance 113°C/W¹ 28°C/W  16-Lead LFCSP Package θ <sub>JA</sub> Thermal Impedance 175°C/W¹ θ <sub>JC</sub> Thermal Impedance 75°C/W¹ θ <sub>JC</sub> Thermal Impedance γ <sub>JC</sub> Thermal Impedance η <sub>JC</sub> Thermal Impedance                                                                                                                                                                                                                                                                                           | Vout to AGND                                    | V <sub>SS</sub> to V <sub>DD</sub> |

| T <sub>A</sub> Industrial  Storage Temperature Range  Junction Temperature, T <sub>J MAX</sub> 16-Lead TSSOP Package  θ <sub>JA</sub> Thermal Impedance  θ <sub>JC</sub> Thermal Impedance  113°C/W¹  28°C/W  16-Lead LFCSP Package  θ <sub>JA</sub> Thermal Impedance  75°C/W¹  θ <sub>JC</sub> Thermal Impedance  75°C/W²  Power Dissipation  Lead Temperature  Soldering  -65°C to +150°C  150°C  150°C  170°C/W¹  28°C/W¹  4.5°C/W²  4.5°C/W²  4.5°C/W²  4.5°C/W²  4.5°C/W²  4.5°C/W²                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AGND to DGND                                    | −0.3 V to +0.3 V                   |

| Junction Temperature, TJMAX  16-Lead TSSOP Package  \( \theta_{JA} \) Thermal Impedance  \( \theta_{JC} \) Thermal Impedance  \( \theta_{JA} \) Thermal Impedance  \( \theta_{JA} \) Thermal Impedance  \( \theta_{JA} \) Thermal Impedance  \( \theta_{JC} \) Thermal Impedan |                                                 | −40°C to +125°C                    |

| 16-Lead TSSOP Package  θ <sub>JA</sub> Thermal Impedance  θ <sub>JC</sub> Thermal Impedance  113°C/W¹  28°C/W  16-Lead LFCSP Package  θ <sub>JA</sub> Thermal Impedance  75°C/W¹  θ <sub>JC</sub> Thermal Impedance  4.5°C/W²  Power Dissipation  Lead Temperature  Soldering  J-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Storage Temperature Range                       | −65°C to +150°C                    |

| θ <sub>JA</sub> Thermal Impedance113°C/W¹θ <sub>JC</sub> Thermal Impedance28°C/W16-Lead LFCSP Package75°C/W¹θ <sub>JA</sub> Thermal Impedance75°C/W²θ <sub>JC</sub> Thermal Impedance4.5°C/W²Power Dissipation(T <sub>J MAX</sub> - T <sub>A</sub> )/θ <sub>JA</sub> Lead TemperatureJEDEC industry standardSolderingJ-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Junction Temperature, TJ MAX                    | 150°C                              |

| θ <sub>JC</sub> Thermal Impedance28°C/W16-Lead LFCSP Package75°C/W¹θ <sub>JA</sub> Thermal Impedance4.5°C/W²Power Dissipation(T <sub>J MAX</sub> - T <sub>A</sub> )/θ <sub>JA</sub> Lead TemperatureJEDEC industry standardSolderingJ-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-Lead TSSOP Package                           |                                    |

| 16-Lead LFCSP Package75°C/W¹ $\theta_{JA}$ Thermal Impedance75°C/W² $\theta_{JC}$ Thermal Impedance $4.5$ °C/W²Power Dissipation $(T_{J,MAX} - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standardSolderingJ-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\theta_{JA}$ Thermal Impedance                 | 113°C/W¹                           |

| $\begin{array}{lll} \theta_{JA} \ Thermal \ Impedance & 75^{\circ} C/W^1 \\ \theta_{JC} \ Thermal \ Impedance & 4.5^{\circ} C/W^2 \\ Power \ Dissipation & (T_{J \ MAX} - T_A)/\theta_{JA} \\ Lead \ Temperature & JEDEC \ industry \ standard \\ Soldering & J-STD-020 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\theta_{JC}$ Thermal Impedance                 | 28°C/W                             |

| $\begin{array}{ccc} \theta_{JC} \ Thermal \ Impedance & 4.5^{\circ}C/W^2 \\ Power \ Dissipation & (T_{J \ MAX} - T_A)/\theta_{JA} \\ Lead \ Temperature & JEDEC \ industry \ standard \\ Soldering & J-STD-020 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16-Lead LFCSP Package                           |                                    |

| Power Dissipation $(T_{J MAX} - T_A)/\theta_{JA}$<br>Lead Temperature JEDEC industry standard J-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\theta_{JA}$ Thermal Impedance                 | 75°C/W <sup>1</sup>                |

| Lead Temperature JEDEC industry standard J-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\theta_{JC}$ Thermal Impedance                 | 4.5°C/W <sup>2</sup>               |

| Soldering J-STD-020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power Dissipation                               | $(T_{JMAX} - T_{A})/\theta_{JA}$   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Lead Temperature                                | JEDEC industry standard            |