# 20V, 500mA, Ultralow Noise, Ultrahigh PSRR Linear Regulator

### **FEATURES**

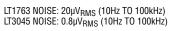

- Ultralow RMS Noise: 0.8µV<sub>RMS</sub> (10Hz to 100kHz)

- Ultralow Spot Noise: 2nV/√Hz at 10kHz

- Ultrahigh PSRR: 76dB at 1MHz

- Output Current: 500mA

- Wide Input Voltage Range: 1.8V to 20V

- Single Capacitor Improves Noise and PSRR

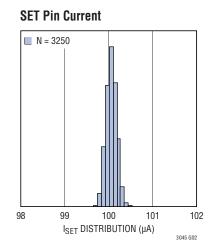

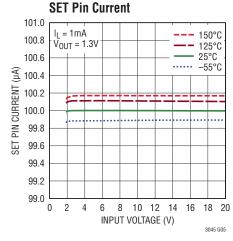

- 100µA SET Pin Current: ±1% Initial Accuracy

- Single Resistor Programs Output Voltage

- High Bandwidth: 1MHz

- Programmable Current Limit

- Low Dropout Voltage: 260mV

- Output Voltage Range: 0V to 15V

- Programmable Power Good

- Fast Start-Up Capability

- Precision Enable/UVLO

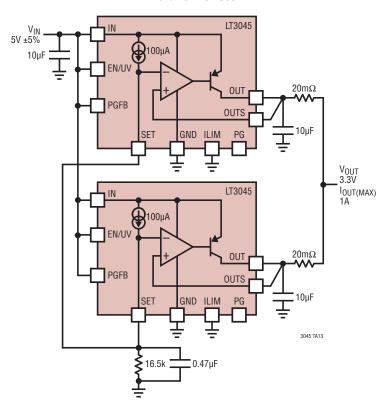

- Parallelable for Lower Noise and Higher Current

- Internal Current Limit with Foldback

- Minimum Output Capacitor: 10µF Ceramic

- Reverse-Battery and Reverse-Current Protection

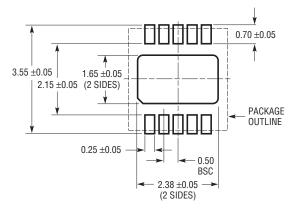

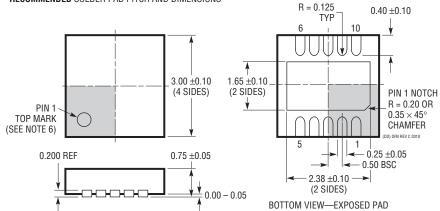

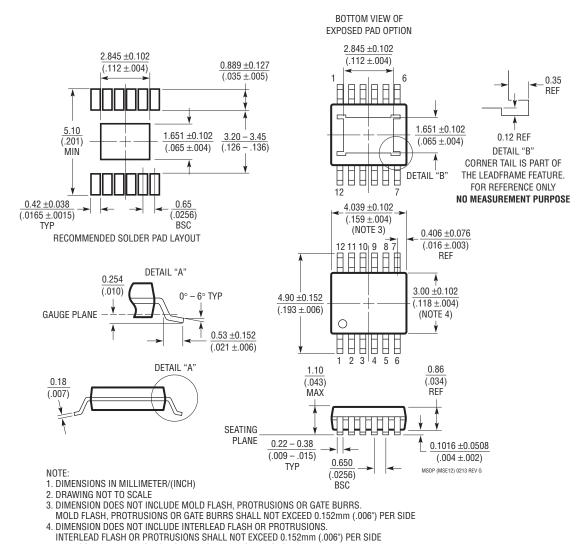

- 12-Lead MSOP and 10-Lead 3mm × 3mm DFN Packages

- AEC-Q100 Qualified for Automotive Applications

### **APPLICATIONS**

- RF Power Supplies: PLLs, VCOs, Mixers, LNAs, PAs

- Very Low Noise Instrumentation

- High Speed/High Precision Data Converters

- Medical Applications: Imaging, Diagnostics

- Precision Power Supplies

- Post-Regulator for Switching Supplies

### DESCRIPTION

The LT®3045 is a high performance low dropout linear regulator featuring LTC's ultralow noise and ultrahigh PSRR architecture for powering noise sensitive applications. Designed as a precision current reference followed by a high performance voltage buffer, the LT3045 can be easily paralleled to further reduce noise, increase output current and spread heat on the PCB.

The device supplies 500mA at a typical 260mV dropout voltage. Operating quiescent current is nominally 2.2mA and drops to <<1 $\mu$ A in shutdown. The LT3045's wide output voltage range (0V to 15V) while maintaining unitygain operation provides virtually constant output noise, PSRR, bandwidth and load regulation, independent of the programmed output voltage. Additionally, the regulator features programmable current limit, fast start-up capability and programmable power good to indicate output voltage regulation.

The LT3045 is stable with a minimum  $10\mu F$  ceramic output capacitor. Built-in protection includes reverse-battery protection, reverse-current protection, internal current limit with foldback and thermal limit with hysteresis. The LT3045 is available in thermally enhanced 12-Lead MSOP and 10-Lead 3mm  $\times$  3mm DFN packages.

All registered trademarks and trademarks are the property of their respective owners.

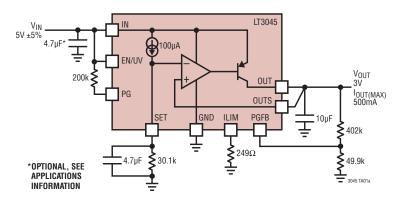

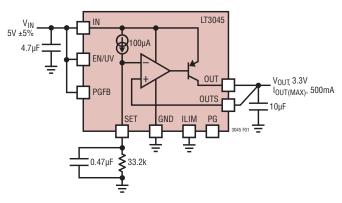

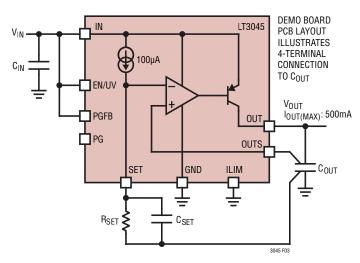

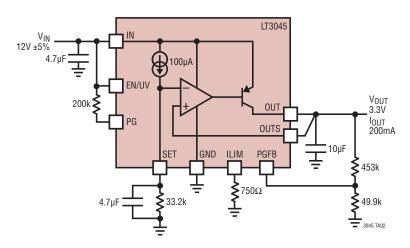

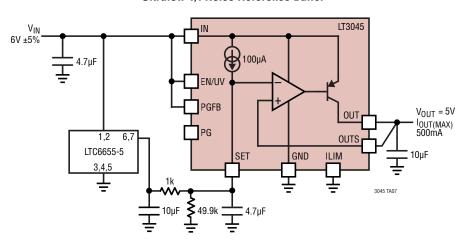

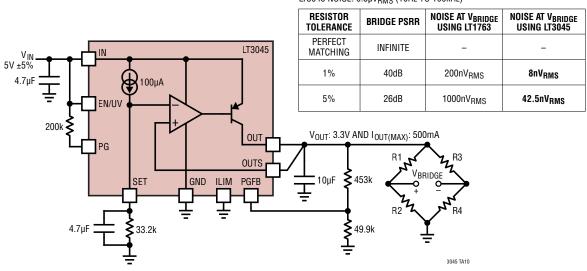

### TYPICAL APPLICATION

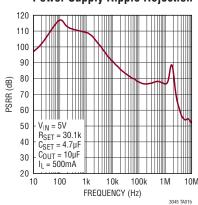

### **Power Supply Ripple Rejection**

Rev. D

1

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| IN Pin Voltage             | ±22V      |

|----------------------------|-----------|

| EN/UV Pin Voltage          |           |

| IN-to-EN/UV Differential   | ±22V      |

| PG Pin Voltage (Note 10)   | 0.3V, 22V |

| ILIM Pin Voltage (Note 10) | 0.3V, 1V  |

| PGFB Pin Voltage (Note 10) | 0.3V, 22V |

| SET Pin Voltage (Note 10)  | 0.3V, 16V |

| SET Pin Current (Note 7)   | ±20mA     |

| OUTS Pin Voltage (Note 10) | 0.3V, 16V |

| OUTS Pin Current (Note 7)  | ±20mA     |

| OUT Pin Voltage (Note 10)  | 0.3V, 16V |

|                            |           |

| OUT-to-OUTS Differential (Note 14) ±1.2V      |

|-----------------------------------------------|

| IN-to-OUT Differential±22V                    |

| IN-to-OUTS Differential±22V                   |

| Output Short-Circuit Duration Indefinite      |

| Operating Junction Temperature Range (Note 9) |

| E-Grade, I-Grade40°C to 125°C                 |

| H-Grade, –40°C to 150°C                       |

| MP-Grade (Note 15)55°C to 150°C               |

| Storage Temperature Range65°C to 150°C        |

| Lead Temperature (Soldering, 10 Sec)          |

| MSE Package300°C                              |

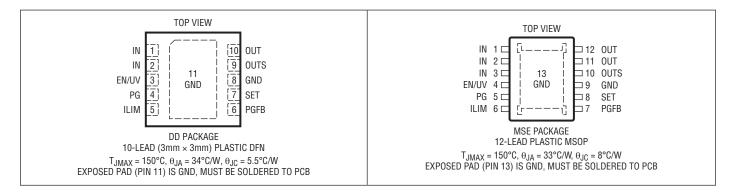

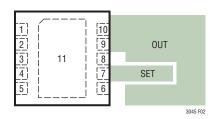

### PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH          | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|---------------------------|-------------------|---------------|---------------------------------|-------------------|

| LT3045EDD#PBF             | LT3045EDD#TRPBF   | LGYP          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3045IDD#PBF             | LT3045IDD#TRPBF   | LGYP          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3045HDD#PBF             | LT3045HDD#TRPBF   | LGYP          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 150°C    |

| LT3045MPDD#PBF            | LT3045MPDD#TRPBF  | LGYP          | 10-Lead (3mm × 3mm) Plastic DFN | −55°C to 150°C    |

| LT3045EMSE#PBF            | LT3045EMSE#TRPBF  | 3045          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3045IMSE#PBF            | LT3045IMSE#TRPBF  | 3045          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3045HMSE#PBF            | LT3045HMSE#TRPBF  | 3045          | 12-Lead Plastic MSOP            | -40°C to 150°C    |

| <b>AUTOMOTIVE PRODUCT</b> | · S * *           |               |                                 |                   |

| LT3045EMSE#WPBF           | LT3045EMSE#WTRPBF | 3045          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3045IMSE#WPBF           | LT3045IMSE#WTRPBF | 3045          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3045HMSE#WPBF           | LT3045HMSE#WTRPBF | 3045          | 12-Lead Plastic MSOP            | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

<sup>\*\*</sup>Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ .

| PARAMETER                                                                                                 | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | MIN      | TYP                            | MAX                    | UNITS                                                       |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|--------------------------------|------------------------|-------------------------------------------------------------|

| Input Voltage Range                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • | 2        |                                | 20                     | V                                                           |

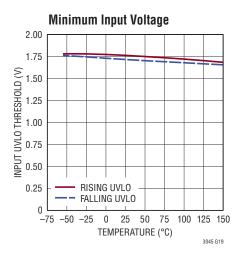

| Minimum IN Pin Voltage (Note 2)                                                                           | $I_{LOAD}$ = 500mA, $V_{IN}$ UVLO Rising $V_{IN}$ UVLO Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • |          | 1.78<br>75                     | 2                      | V<br>mV                                                     |

| Output Voltage Range                                                                                      | V <sub>IN</sub> > V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • | 0        |                                | 15                     | V                                                           |

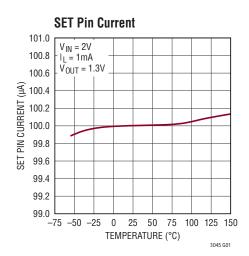

| SET Pin Current (I <sub>SET</sub> )                                                                       | $V_{IN}$ = 2V, $I_{LOAD}$ = 1mA, $V_{OUT}$ = 1.3V<br>2V < $V_{IN}$ < 20V, 0V < $V_{OUT}$ < 15V, 1mA < $I_{LOAD}$ < 500mA (Note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • | 99<br>98 | 100<br>100                     | 101<br>102             | μA<br>μA                                                    |

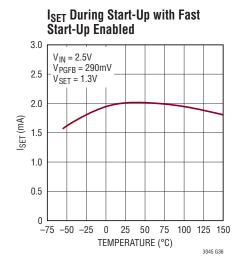

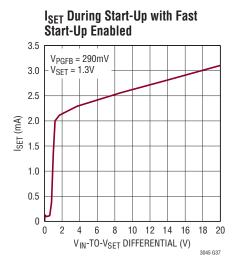

| Fast Start-Up Set Pin<br>Current                                                                          | V <sub>PGFB</sub> = 289mV, V <sub>IN</sub> = 2.8V, V <sub>SET</sub> = 1.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |          | 2                              |                        | mA                                                          |

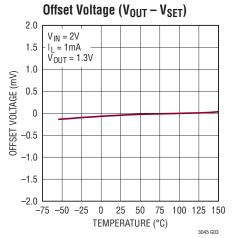

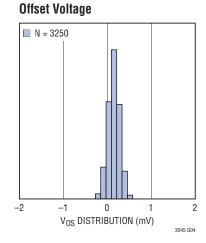

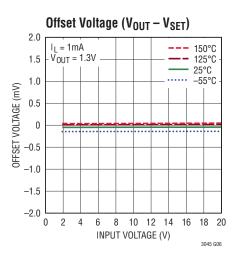

| Output Offset Voltage<br>V <sub>OS</sub> (V <sub>OUT</sub> – V <sub>SET</sub> )<br>(Note 4)               | $V_{IN} = 2V$ , $I_{LOAD} = 1$ mA, $V_{OUT} = 1.3V$<br>$2V < V_{IN} < 20V$ , $0V < V_{OUT} < 15V$ , $1$ mA $< I_{LOAD} < 500$ mA (Note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | -1<br>-2 |                                | 1<br>2                 | mV<br>mV                                                    |

| Line Regulation: $\Delta I_{SET}$<br>Line Regulation: $\Delta V_{OS}$                                     | $V_{IN}$ = 2V to 20V, $I_{LOAD}$ = 1mA, $V_{OUT}$ = 1.3V<br>$V_{IN}$ = 2V to 20V, $I_{LOAD}$ = 1mA, $V_{OUT}$ = 1.3V (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • |          | 0.5<br>0.5                     | ±2<br>±3               | nA/V<br>μV/V                                                |

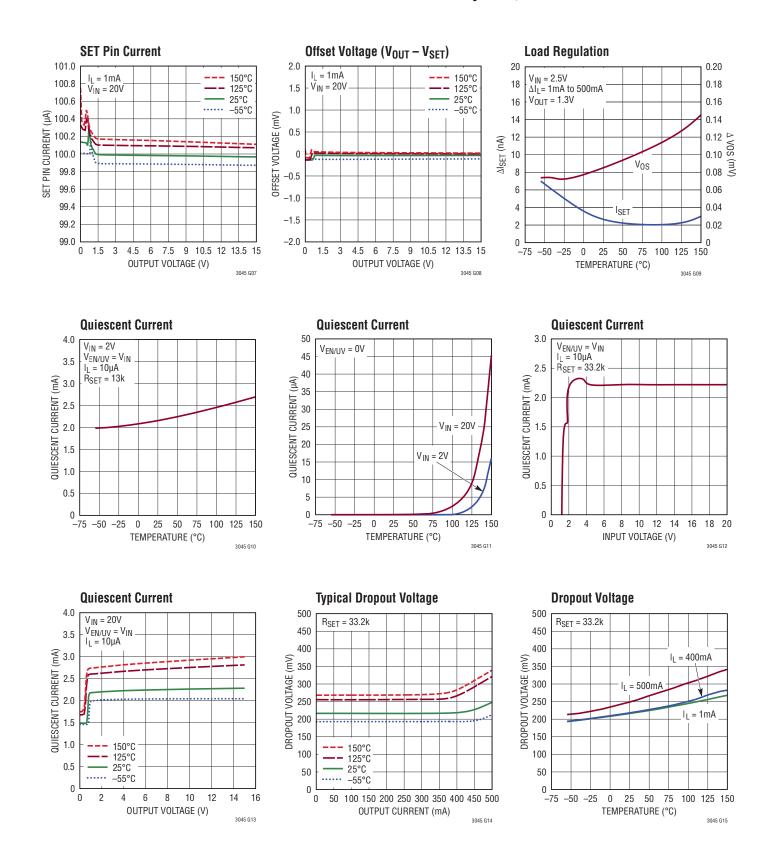

| Load Regulation: ΔI <sub>SET</sub><br>Load Regulation: ΔV <sub>OS</sub>                                   | $I_{LOAD}$ = 1mA to 500mA, $V_{IN}$ = 2V, $V_{OUT}$ = 1.3V<br>$I_{LOAD}$ = 1mA to 500mA, $V_{IN}$ = 2V, $V_{OUT}$ = 1.3V (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • |          | 3<br>0.1                       | 0.5                    | nA<br>mV                                                    |

| Change in I_SET with V_SET Change in V_OS with V_SET Change in I_SET with V_SET Change in V_OS with V_SET | $ \begin{aligned} & V_{SET} = 1.3 \text{V to } 15 \text{V, } V_{\text{IN}} = 20 \text{V, } I_{\text{LOAD}} = 1 \text{mA} \\ & V_{SET} = 1.3 \text{V to } 15 \text{V, } V_{\text{IN}} = 20 \text{V, } I_{\text{LOAD}} = 1 \text{mA (Note 4)} \\ & V_{SET} = 0 \text{V to } 1.3 \text{V, } V_{\text{IN}} = 20 \text{V, } I_{\text{LOAD}} = 1 \text{mA} \\ & V_{SET} = 0 \text{V to } 1.3 \text{V, } V_{\text{IN}} = 20 \text{V, } I_{\text{LOAD}} = 1 \text{mA (Note 4)} \end{aligned} $                                                                                                                                                                                                                                                                           | • |          | 30<br>0.03<br>150<br>0.3       | 400<br>0.6<br>600<br>2 | nA<br>mV<br>nA<br>mV                                        |

| Dropout Voltage                                                                                           | $I_{LOAD} = 1 \text{mA}, 50 \text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • |          | 220                            | 275<br>330             | mV<br>mV                                                    |

|                                                                                                           | I <sub>LOAD</sub> = 300mA (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • |          | 220                            | 280<br>350             | mV<br>mV                                                    |

|                                                                                                           | I <sub>LOAD</sub> = 500mA (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • |          | 260                            | 350<br>450             | mV<br>mV                                                    |

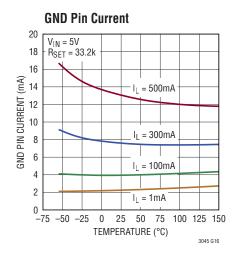

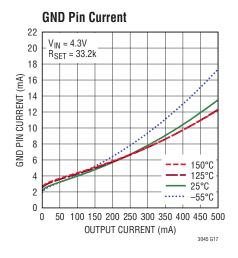

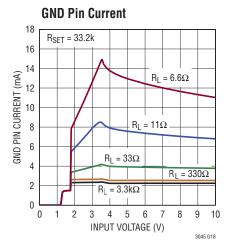

| GND Pin Current V <sub>IN</sub> = V <sub>OUT(NOMINAL)</sub> (Note 6)                                      | $\begin{split} I_{LOAD} &= 10 \mu A \\ I_{LOAD} &= 1 m A \\ I_{LOAD} &= 50 m A \\ I_{LOAD} &= 100 m A \\ I_{LOAD} &= 500 m A \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • |          | 2.2<br>2.4<br>3.5<br>4.3<br>15 | 4<br>5.5<br>7<br>25    | mA<br>mA<br>mA<br>mA                                        |

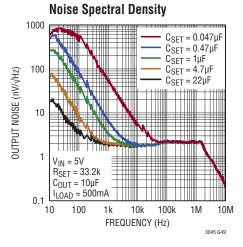

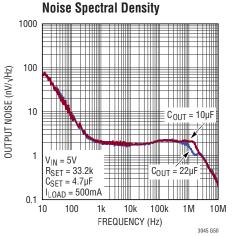

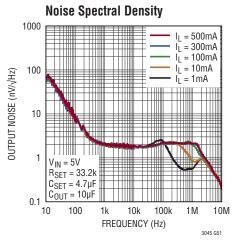

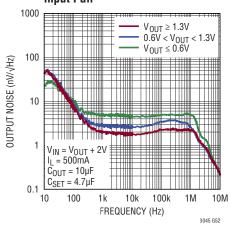

| Output Noise Spectral<br>Density (Notes 4, 8)                                                             | $\begin{array}{l} I_{LOAD} = 500 \text{mA}, \ \text{Frequency} = 10 \text{Hz}, \ C_{OUT} = 10 \mu\text{F}, \ C_{SET} = 0.47 \mu\text{F}, \ V_{OUT} = 3.3 \text{V} \\ I_{LOAD} = 500 \text{mA}, \ \text{Frequency} = 10 \text{Hz}, \ C_{OUT} = 10 \mu\text{F}, \ C_{SET} = 4.7 \mu\text{F}, \ 1.3 \text{V} \leq V_{OUT} \leq 15 \text{V} \\ I_{LOAD} = 500 \text{mA}, \ \text{Frequency} = 10 \text{kHz}, \ C_{OUT} = 10 \mu\text{F}, \ C_{SET} = 0.47 \mu\text{F}, \ 1.3 \text{V} \leq V_{OUT} \leq 15 \text{V} \\ I_{LOAD} = 500 \text{mA}, \ \text{Frequency} = 10 \text{kHz}, \ C_{OUT} = 10 \mu\text{F}, \ C_{SET} = 0.47 \mu\text{F}, \ 0 \text{V} \leq V_{OUT} < 1.3 \text{V} \\ \end{array}$                                                              |   |          | 500<br>70<br>2<br>5            |                        | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz                        |

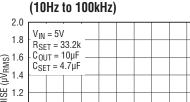

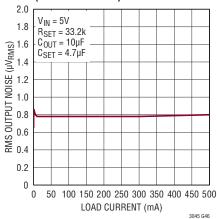

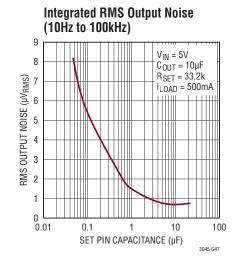

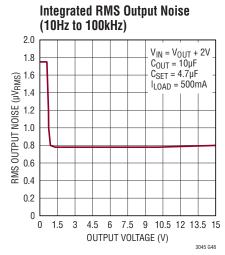

| Output RMS Noise<br>(Notes 4, 8)                                                                          | $\begin{array}{l} I_{LOAD} = 500 mA, \ BW = 10 Hz \ to \ 100 kHz, \ C_{OUT} = 10 \mu F, \ C_{SET} = 0.47 \mu F, \ V_{OUT} = 3.3 V \\ I_{LOAD} = 500 mA, \ BW = 10 Hz \ to \ 100 kHz, \ C_{OUT} = 10 \mu F, \ C_{SET} = 4.7 \mu F, \ 1.3 V \leq V_{OUT} \leq 15 V \\ I_{LOAD} = 500 mA, \ BW = 10 Hz \ to \ 100 kHz, \ C_{OUT} = 10 \mu F, \ C_{SET} = 4.7 \mu F, \ 0V \leq V_{OUT} < 1.3 V \end{array}$                                                                                                                                                                                                                                                                                                                                                          |   |          | 2.5<br>0.8<br>1.8              |                        | μV <sub>RMS</sub><br>μV <sub>RMS</sub><br>μV <sub>RMS</sub> |

| Reference Current RMS<br>Output Noise (Notes 4, 8)                                                        | BW = 10Hz to 100kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |          | 6                              |                        | nA <sub>RMS</sub>                                           |

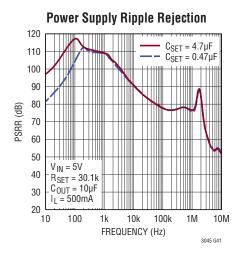

| Ripple Rejection $1.3V \le V_{OUT} \le 15V$ $V_{IN} - V_{OUT} = 2V \text{ (Avg)}$ (Notes 4, 8)            | $ \begin{array}{l} V_{RIPPLE} = 500 mV_{P-P},  f_{RIPPLE} = 120 \text{Hz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 4.7 \mu\text{F} \\ V_{RIPPLE} = 150 mV_{P-P},  f_{RIPPLE} = 10 \text{kHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 150 mV_{P-P},  f_{RIPPLE} = 100 \text{kHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 150 mV_{P-P},  f_{RIPPLE} = 10 \text{MHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 80 mV_{P-P},  f_{RIPPLE} = 10 \text{MHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ \end{array} $ |   |          | 117<br>90<br>77<br>76<br>53    |                        | dB<br>dB<br>dB<br>dB                                        |

| Ripple Rejection $0V \le V_{OUT} < 1.3V$ $V_{IN} - V_{OUT} = 2V \text{ (Avg)}$ (Notes 4, 8)               | $\begin{array}{l} V_{RIPPLE} = 500mV_{P-P},  f_{RIPPLE} = 120 \text{Hz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 50mV_{P-P},  f_{RIPPLE} = 10 \text{kHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 50mV_{P-P},  f_{RIPPLE} = 100 \text{kHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 50mV_{P-P},  f_{RIPPLE} = 10 \text{MHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ V_{RIPPLE} = 50mV_{P-P},  f_{RIPPLE} = 10 \text{MHz},  I_{LOAD} = 500 \text{mA},  C_{OUT} = 10 \mu\text{F},  C_{SET} = 0.47 \mu\text{F} \\ \end{array}$          |   |          | 104<br>85<br>72<br>64<br>54    |                        | dB<br>dB<br>dB<br>dB                                        |

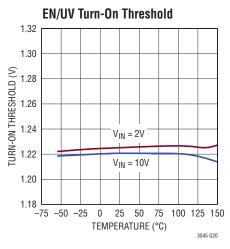

| EN/UV Pin Threshold                                                                                       | EN/UV Trip Point Rising (Turn-On), V <sub>IN</sub> = 2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | 1.18     | 1.24                           | 1.32                   | V                                                           |

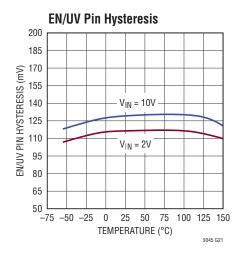

| EN/UV Pin Hysteresis                                                                                      | EN/UV Trip Point Hysteresis, V <sub>IN</sub> = 2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |          | 130                            |                        | mV                                                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| PARAMETER                                                  | CONDITIONS                                                                                                                                                                                                                                                                                                                                                    |   | MIN        | TYP               | MAX           | UNITS               |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------------|---------------|---------------------|

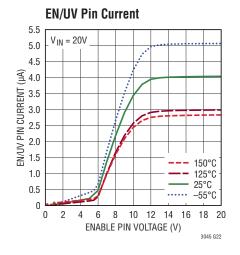

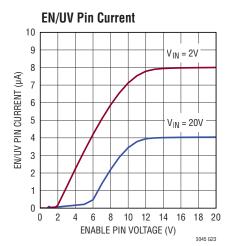

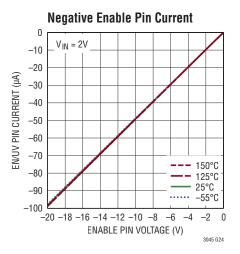

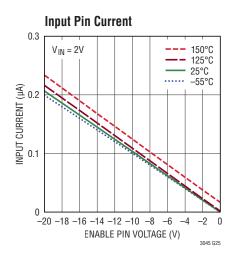

| EN/UV Pin Current                                          | $V_{EN/UV} = 0V, V_{IN} = 20V$<br>$V_{EN/UV} = 1.24V, V_{IN} = 20V$<br>$V_{EN/UV} = 20V, V_{IN} = 0V$                                                                                                                                                                                                                                                         | • |            | 0.03              | ±1<br>15      | μΑ<br>μΑ<br>μΑ      |

| Quiescent Current in<br>Shutdown (V <sub>EN/UV</sub> = 0V) | $V_{IN} = 6V$<br>$T_J \le 125^{\circ}C$ (E/I-Grade)<br>$T_J \le 150^{\circ}C$ (H-/MP-Grade)                                                                                                                                                                                                                                                                   | • |            | 0.3               | 1<br>10<br>20 | μΑ<br>μΑ<br>μΑ      |

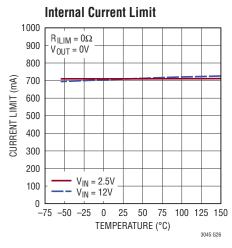

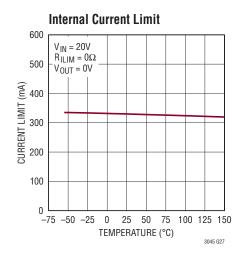

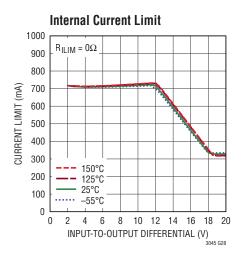

| Internal Current Limit<br>(Note 12)                        | $V_{IN} = 2V, V_{OUT} = 0V \\ V_{IN} = 12V, V_{OUT} = 0V \\ V_{IN} = 20V, V_{OUT} = 0V$                                                                                                                                                                                                                                                                       | • | 570<br>230 | 710<br>700<br>330 | 850<br>430    | mA<br>mA<br>mA      |

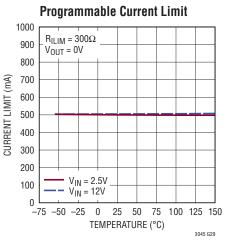

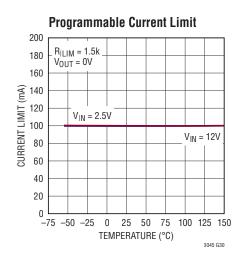

| Programmable<br>Current Limit                              | Programming Scale Factor: $2V < V_{IN} < 20V$ (Note 11) $V_{IN} = 2V$ , $V_{OUT} = 0V$ , $R_{ILIM} = 300\Omega$ $V_{IN} = 2V$ , $V_{OUT} = 0V$ , $R_{ILIM} = 1.5k\Omega$                                                                                                                                                                                      | • | 450<br>90  | 150<br>500<br>100 | 550<br>110    | mA • kΩ<br>mA<br>mA |

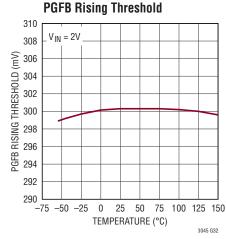

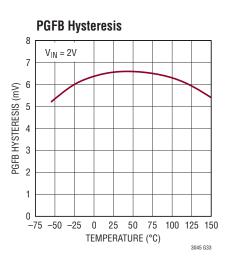

| PGFB Trip Point                                            | PGFB Trip Point Rising                                                                                                                                                                                                                                                                                                                                        | • | 291        | 300               | 309           | mV                  |

| PGFB Hysteresis                                            | PGFB Trip Point Hysteresis                                                                                                                                                                                                                                                                                                                                    |   |            | 7                 |               | mV                  |

| PGFB Pin Current                                           | $V_{IN} = 2V$ , $V_{PGFB} = 300$ mV                                                                                                                                                                                                                                                                                                                           |   |            | 25                |               | nA                  |

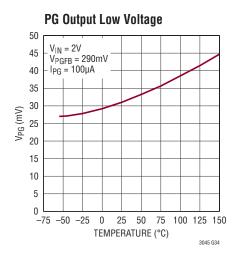

| PG Output Low Voltage                                      | $I_{PG} = 100\mu A$                                                                                                                                                                                                                                                                                                                                           | • |            | 30                | 100           | mV                  |

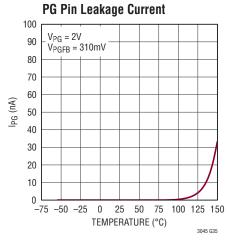

| PG Leakage Current                                         | V <sub>PG</sub> = 20V                                                                                                                                                                                                                                                                                                                                         | • |            |                   | 1             | μA                  |

| Reverse Input Current                                      | $V_{IN} = -20V$ , $V_{EN/UV} = 0V$ , $V_{OUT} = 0V$ , $V_{SET} = 0V$                                                                                                                                                                                                                                                                                          | • |            |                   | 100           | μA                  |

| Reverse Output Current                                     | $V_{IN} = 0$ , $V_{OUT} = 5V$ , SET = Open                                                                                                                                                                                                                                                                                                                    |   |            | 14                | 25            | μA                  |

| Minimum Load Required (Note 13)                            | V <sub>OUT</sub> < 1V                                                                                                                                                                                                                                                                                                                                         | • | 10         |                   |               | μА                  |

| Thermal Shutdown                                           | T <sub>J</sub> Rising<br>Hysteresis                                                                                                                                                                                                                                                                                                                           |   |            | 165<br>8          |               | 0°<br>0°            |

| Start-Up Time                                              | $V_{OUT(NOM)} = 5V$ , $I_{LOAD} = 500$ mA, $C_{SET} = 0.47$ μF, $V_{IN} = 6V$ , $V_{PGFB} = 6V$ $V_{OUT(NOM)} = 5V$ , $I_{LOAD} = 500$ mA, $C_{SET} = 4.7$ μF, $V_{IN} = 6V$ , $V_{PGFB} = 6V$ $V_{OUT(NOM)} = 5V$ , $I_{LOAD} = 500$ mA, $C_{SET} = 4.7$ μF, $V_{IN} = 6V$ , $R_{PG1} = 50$ kΩ, $R_{PG2} = 700$ kΩ (with Fast Start-Up to 90% of $V_{OUT}$ ) |   |            | 55<br>550<br>10   |               | ms<br>ms<br>ms      |

| Thermal Regulation                                         | 10ms Pulse                                                                                                                                                                                                                                                                                                                                                    |   |            | -0.01             |               | %/W                 |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The EN/UV pin threshold must be met to ensure device operation.

**Note 3:** Maximum junction temperature limits operating conditions. The regulated output voltage specification does not apply for all possible combinations of input voltage and output current, especially due to the internal current limit foldback which starts to decrease current limit at  $V_{IN} - V_{OUT} > 12V$ . If operating at maximum output current, limit the input voltage range. If operating at the maximum input voltage, limit the output current range.

Note 4: OUTS ties directly to OUT.

**Note 5:** Dropout voltage is the minimum input-to-output differential voltage needed to maintain regulation at a specified output current. The dropout voltage is measured when output is 1% out of regulation. This definition results in a higher dropout voltage compared to hard dropout — which is measured when V<sub>IN</sub> = V<sub>OUT(NOMINAL)</sub>. For lower output voltages, below 1.5V, dropout voltage is limited by the minimum input voltage specification. **For DFN package: Linear Technology is unable to**

guarantee maximum dropout voltage specifications at high currents due to production test limitations with Kelvin-sensing the package pins. Please consult the Typical Performance Characteristics for curves of dropout voltage as a function of output load current and temperature measured in a typical application circuit.

**Note 6:** GND pin current is tested with  $V_{IN} = V_{OUT(NOMINAL)}$  and a current source load. Therefore, the device is tested while operating in dropout. This is the worst-case GND pin current. GND pin current decreases at higher input voltages. Note that GND pin current does not include SET pin or ILIM pin current but Quiescent current does include them.

**Note 7:** SET and OUTS pins are clamped using diodes and two  $25\Omega$  series resistors. For less than 5ms transients, this clamp circuitry can carry more than the rated current. Refer to Applications Information for more information.

**Note 8:** Adding a capacitor across the SET pin resistor decreases output voltage noise. Adding this capacitor bypasses the SET pin resistor's thermal noise as well as the reference current's noise. The output noise then equals the error amplifier noise. Use of a SET pin bypass capacitor also increases start-up time.

### **ELECTRICAL CHARACTERISTICS**

**Note 9:** The LT3045 is tested and specified under pulsed load conditions such that  $T_J \approx T_A$ . The LT3045E is 100% tested at 25°C and performance is guaranteed from 0°C to 125°C. Specifications over the –40°C to 125°C operating temperature range are assured by design, characterization, and correlation with statistical process controls. The LT3045I is guaranteed over the full –40°C to 125°C operating temperature range. LT3045H is 100% tested at the 150°C operating junction temperature. LT3045MP is 100% tested and guaranteed over the full –55°C to 150°C operating temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 10:** Parasitic diodes exist internally between the ILIM, PG, PGFB, SET, OUTS, and OUT pins and the GND pin. Do not drive these pins more than 0.3V below the GND pin during a fault condition. These pins must remain at a voltage more positive than GND during normal operation.

**Note 11:** The current limit programming scale factor is specified while the internal backup current limit is not active. Note that the internal current limit has foldback protection for  $V_{\text{IN}} - V_{\text{OUT}}$  differentials greater than 12V.

**Note 12:** The internal back-up current limit circuitry incorporates foldback protection that decreases current limit for  $V_{IN} - V_{OUT} > 12V$ . Some level of output current is provided at all  $V_{IN} - V_{OUT}$  differential voltages. Consult the Typical Performance Characteristics graph for current limit vs  $V_{IN} - V_{OUT}$ .

Note 13: For output voltages less than 1V, the LT3045 requires a  $10\mu A$  minimum load current for stability.

Note 14: Maximum OUT-to-OUTS differential is guaranteed by design.

Note 15: MP-Grade is only offered in the DFN package.

# TYPICAL PERFORMANCE CHARACTERISTICS T<sub>J</sub> = 25°C, unless otherwise noted.

Rev. [

# TYPICAL PERFORMANCE CHARACTERISTICS T<sub>J</sub> = 25°C, unless otherwise noted.

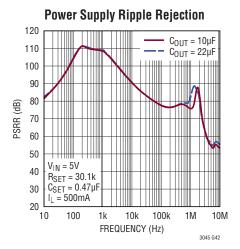

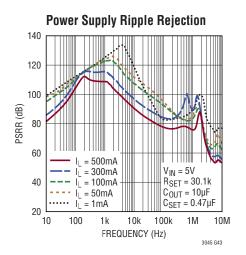

**Power Supply Ripple Rejection**

**Integrated RMS Output Noise**

### **Noise Spectral Density as** a Function of Error Amplifier **Input Pair**

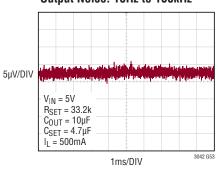

### Output Noise: 10Hz to 100kHz

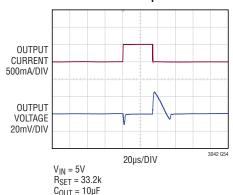

### **Load Transient Response**

V<sub>IN</sub> = 5V R<sub>SET</sub> = 33.2k C<sub>OUT</sub> = 10μF C<sub>SET</sub> = 0.47μF LOAD STEP = 10mA TO 500mA

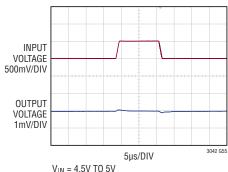

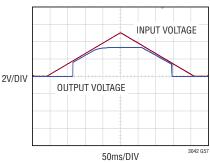

### **Line Transient Response**

$$\begin{split} &V_{|N} = 4.5 V \text{ TO 5V} \\ &R_{SET} = 33.2 k \\ &C_{OUT} = 10 \mu F \\ &C_{SET} = 0.47 \mu F \\ &I_{\perp} = 500 \text{mA} \end{split}$$

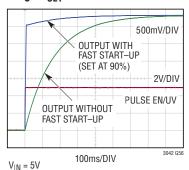

### Start-Up Time with and without Fast Start-Up Circuitry for Large C<sub>SET</sub>

$R_{SET} = 33.2k$   $C_{OUT} = 10\mu F$   $C_{SET} = 4.7\mu F$   $R_{L} = 6.6\Omega$

### **Input Supply Ramp-Up and** Ramp-Down

V<sub>IN</sub> = 0V TO 5V  $\begin{aligned} &V_{EN/UV} = V_{IN} \\ &R_{SET} = 33.2k \\ &C_{OUT} = 10 \mu F \\ &C_{SET} = 0.47 \mu F \\ &R_L = 6.6 \Omega \end{aligned}$

### PIN FUNCTIONS (DFN/MSOP)

IN (Pins 1, 2/Pins 1, 2, 3): Input. These pins supply power to the regulator. The LT3045 requires a bypass capacitor at the IN pin. In general, a battery's output impedance rises with frequency, so include a bypass capacitor in battery-powered applications. While a 4.7µF input bypass capacitor generally suffices, applications with large load transients may require higher input capacitance to prevent input supply droop. Consult the Applications Information section on the proper use of an input capacitor and its effect on circuit performance, in particular PSRR, The LT3045 withstands reverse voltages on IN with respect to GND. OUTS and OUT. In the case of a reversed input, which occurs if a battery is plugged-in backwards, the LT3045 acts as if a diode is in series with its input. Hence, no reverse current flows into the LT3045 and no negative voltage appears at the load. The device protects itself and the load.

**EN/UV** (**Pin 3/Pin 4**): Enable/UVLO. Pulling the LT3045's EN/UV pin low places the part in shutdown. Quiescent current in shutdown drops to less than 1μA and the output voltage turns off. Alternatively, the EN/UV pin can set an input supply undervoltage lockout (UVLO) threshold using a resistor divider between IN, EN/UV and GND. The LT3045 typically turns on when the EN/UV voltage exceeds 1.24V on its rising edge, with a 130mV hysteresis on its falling edge. The EN/UV pin can be driven above the input voltage and maintain proper functionality. If unused, tie EN/UV to IN. Do not float the EN/UV pin.

**PG** (**Pin 4/Pin 5**): Power Good. PG is an open-collector flag that indicates output voltage regulation. PG pulls low if PGFB is below 300mV. If the power good functionality is not needed, float the PG pin. A parasitic substrate diode exists between PG and GND pins of the LT3045; do not drive PG more than 0.3V below GND during normal operation or during a fault condition.

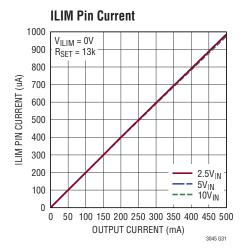

**ILIM (Pin 5/Pin 6):** Current Limit Programming Pin. Connecting a resistor between ILIM and GND programs the current limit. For best accuracy, Kelvin connect this resistor directly to the LT3045's GND pin. The programming scale factor is nominally  $150mA \cdot k\Omega$ . The ILIM pin sources current proportional (1:500) to output current;

therefore, it also serves as a current monitoring pin with a 0V to 300mV range. If the programmable current limit functionality is not needed, tie ILIM to GND. A parasitic substrate diode exists between ILIM and GND pins of the LT3045; do not drive ILIM more than 0.3V below GND during normal operation or during a fault condition.

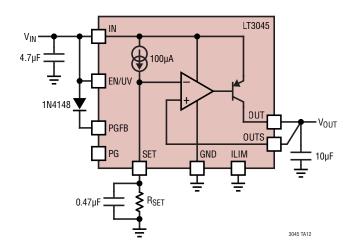

**PGFB (Pin 6/Pin 7):** Power Good Feedback. The PG pin pulls high if PGFB increases beyond 300mV on its rising edge, with 7mV hysteresis on its falling edge. Connecting an external resistor divider between OUT, PGFB and GND sets the programmable power good threshold with the following transfer function: 0.3V • (1 + R<sub>PG2</sub>/R<sub>PG1</sub>). As discussed in the Applications Information section, PGFB also activates the fast start-up circuitry. Tie PGFB to IN if power good and fast start-up functionalities are not needed, and if reverse input protection is additionally required, tie the anode of a 1N4148 diode to IN and its cathode to PGFB. See the Typical Applications section for details. A parasitic substrate diode exists between PGFB and GND pins of the LT3045; do not drive PGFB more than 0.3V below GND during normal operation or during a fault condition.

**SET (Pin 7/Pin 8):** SET. This pin is the inverting input of the error amplifier and the regulation set-point for the LT3045. SET sources a precision  $100\mu\text{A}$  current that flows through an external resistor connected between SET and GND. The LT3045's output voltage is determined by  $V_{\text{SET}} = I_{\text{SET}} \cdot R_{\text{SET}}$ . Output voltage range is from zero to 15V. Adding a capacitor from SET to GND improves noise, PSRR and transient response at the expense of increased start-up time. For optimum load regulation, Kelvin connect the ground side of the SET pin resistor directly to the load. A parasitic substrate diode exists between SET and GND pins of the LT3045; do not drive SET more than 0.3V below GND during normal operation or during a fault condition.

**GND** (Pin 8, Exposed Pad Pin 11/Pin 9, Exposed Pad Pin 13): Ground. The exposed backside is an electrical connection to GND. To ensure proper electrical and thermal performance, solder the exposed backside to the PCB ground and tie it directly to the GND pin.

### PIN FUNCTIONS

**OUTS (Pin 9/Pin 10):** Output Sense. This pin is the non-inverting input to the error amplifier. For optimal transient performance and load regulation, Kelvin connect OUTS directly to the output capacitor and the load. Also, tie the GND connections of the output capacitor and the SET pin capacitor directly together. A parasitic substrate diode exists between OUTS and GND pins of the LT3045; do not drive OUTS more than 0.3V below GND during normal operation or during a fault condition.

**OUT (Pin 10/Pins 11, 12):** Output. This pin supplies power to the load. For stability, use a minimum  $10\mu F$  output capacitor with an ESR below  $20m\Omega$  and an ESL below 2nH. Large load transients require larger output capacitance to limit peak voltage transients. Refer to the Applications Information section for more information on output capacitance. A parasitic substrate diode exists between OUT and GND pins of the LT3045; do not drive OUT more than 0.3V below GND during normal operation or during a fault condition.

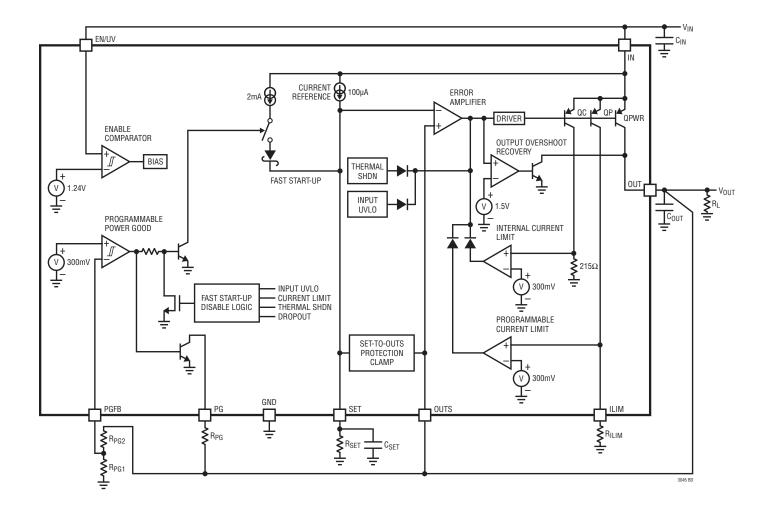

# **BLOCK DIAGRAM**

The LT3045 is a high performance low dropout linear regulator featuring LTC's ultralow noise  $(2nV/\sqrt{Hz})$  at 10kHz) and ultrahigh PSRR (76dB at 1MHz) architecture for powering noise sensitive applications. Designed as a precision current source followed by a high performance rail-to-rail voltage buffer, the LT3045 can be easily paralleled to further reduce noise, increase output current and spread heat on the PCB. The device additionally features programmable current limit, fast start-up capability and programmable power good.

The LT3045 is easy to use and incorporates all of the protection features expected in high performance regulators. Included are short-circuit protection, safe operating area protection, reverse battery protection, reverse current protection, and thermal shutdown with hysteresis.

### **Output Voltage**

The LT3045 incorporates a precision  $100\mu\text{A}$  current source flowing out of the SET pin, which also ties to the error amplifier's inverting input. Figure 1 illustrates that connecting a resistor from SET to ground generates a reference voltage for the error amplifier. This reference voltage is simply the product of the SET pin current and the SET pin resistor. The error amplifier's unity-gain configuration produces a low impedance version of this voltage on its noninverting input, i.e. the OUTS pin, which is externally tied to the OUT pin.

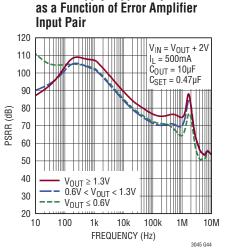

The LT3045's rail-to-rail error amplifier and current reference allows for a wide output voltage range from 0V (using a  $0\Omega$  resistor) to  $V_{IN}$  minus dropout — up to 15V. A PNP-based input pair is active for 0V to 0.6V output and an

Figure 1. Basic Adjustable Regulator

NPN-based input pair is active for output voltages greater than 1.3V, with a smooth transition between the two input pairs from 0.6V to 1.3V output. While the NPN-based input pair is designed to offer the best overall performance, refer to the Electrical Characteristics Table for details on offset voltage, SET pin current, output noise and PSRR variation with the error amp input pair. Table 1 lists many common output voltages and their corresponding 1% R<sub>SET</sub> resistors.

Table 1. 1% Resistor for Common Output Voltages

| V <sub>OUT</sub> (V) | R <sub>SET</sub> (kΩ) |

|----------------------|-----------------------|

| 2.5                  | 24.9                  |

| 3.3                  | 33.2                  |

| 5                    | 49.9                  |

| 12                   | 121                   |

| 15                   | 150                   |

The benefit of using a current reference compared with a voltage reference as used in conventional regulators is that the regulator always operates in unity gain configuration, independent of the programmed output voltage. This allows the LT3045 to have loop gain, frequency response and bandwidth independent of the output voltage. As a result, noise, PSRR and transient performance do not change with output voltage. Moreover, since none of the error amp gain is needed to amplify the SET pin voltage to a higher output voltage, output load regulation is more tightly specified in the hundreds of microvolts range and not as a fixed percentage of the output voltage.

Since the zero TC current source is highly accurate, the SET pin resistor can become the limiting factor in achieving high accuracy. Hence, it should be a precision resistor. Additionally, any leakage paths to or from the SET pin create errors in the output voltage. If necessary, use high quality insulation (e.g., Teflon, Kel-F); moreover, cleaning of all insulating surfaces to remove fluxes and other residues may be required. High humidity environments may require a surface coating at the SET pin to provide a moisture barrier.

Minimize board leakage by encircling the SET pin with a guard ring operated at a potential close to itself — ideally tied to the OUT pin. Guarding both sides of the circuit board is recommended. Bulk leakage reduction depends

on the guard ring width. Leakages of 100nA into or out of the SET pin creates a 0.1% error in the reference voltage. Leakages of this magnitude, coupled with other sources of leakage, can cause significant errors in the output voltage, especially over wide operating temperature range. Figure 2 illustrates a typical guard ring layout technique.

Figure 2. DFN Guard Ring Layout

Since the SET pin is a high impedance node, unwanted signals may couple into the SET pin and cause erratic behavior. This is most noticeable when operating with a minimum output capacitor at heavy load currents. Bypassing the SET pin with a small capacitance to ground resolves this issue — 10nF is sufficient.

For applications requiring higher accuracy or an adjustable output voltage, the SET pin may be actively driven by an external voltage source capable of sinking 100µA. Connecting a precision voltage reference to the SET pin eliminates any errors present in the output voltage due to the reference current and SET pin resistor tolerances.

### **Output Sensing and Stability**

The LT3045's OUTS pin provides a Kelvin sense connection to the output. The SET pin resistor's GND side provides a Kelvin sense connection to the load's GND side.

Additionally, for ultrahigh PSRR, the LT3045 bandwidth is made quite high (~1MHz), making it very close to a typical  $10\mu F$  (1206 case size) ceramic output capacitor's self-resonance frequency (~1.6MHz). Therefore, it is very important to avoid adding extra impedance (ESR and ESL) outside the feedback loop. To that end, as shown in Figure 3, minimize the effects of PCB trace and solder inductance by tying the OUTS pin directly to  $C_{OUT}$  and

Figure 3.  $C_{OUT}$  and  $C_{SET}$  Connections for Best Performance

the GND side of CSET directly to the GND side of  $C_{OUT}$ , as well as keep the GND sides of  $C_{IN}$  and  $C_{OUT}$  reasonably close. Refer to the LT3045 demo board manual for more information on the recommended layout that meets these requirements. While the LT3045 is robust enough not to oscillate if the recommended layout is not followed, depending on the actual layout, phase/gain margin, noise and PSRR performance may degrade.

### **Stability and Output Capacitance**

The LT3045 requires an output capacitor for stability. Given its high bandwidth, LTC recommends low ESR and ESL ceramic capacitors. A minimum 10 $\mu$ F output capacitance with an ESR below 20m $\Omega$  and an ESL below 2nH is required for stability.

Given the high PSRR and low noise performance attained using a single  $10\mu F$  ceramic output capacitor, larger values of output capacitor only marginally improves the performance because the regulator bandwidth decreases with increasing output capacitance — hence, there is little to be gained by using larger than the minimum  $10\mu F$  output capacitor. Nonetheless, larger values of output capacitance do decrease peak output deviations during a load transient. Note that bypass capacitors used to decouple individual components powered by the LT3045 increase the effective output capacitance.

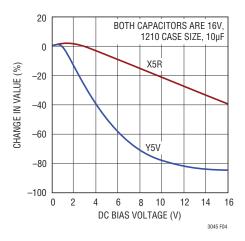

Give extra consideration to the type of ceramic capacitors used. They are manufactured with a variety of dielectrics, each with different behavior across temperature and applied voltage. The most common dielectrics used are specified with EIA temperature characteristic codes of Z5U, Y5V, X5R and X7R. The Z5U and Y5V dielectrics are good for providing high capacitance in the small packages, but they tend to have stronger voltage and temperature coefficients as shown in Figure 4 and Figure 5. When used with a 5V regulator, a  $16V 10\mu F Y5V$  capacitor can exhibit an effective value as low as  $1\mu F$  to  $2\mu F$  for the DC bias voltage applied over the operating temperature range.

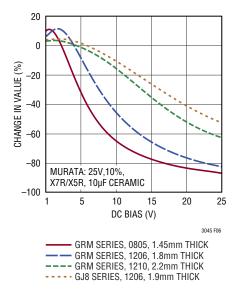

X5R and X7R dielectrics result in more stable characteristics and are thus more suitable for LT3045. The X7R dielectric has better stability across temperature, while the X5R is less expensive and is available in higher values. Nonetheless, care must still be exercised when using X5R and X7R capacitors. The X5R and X7R codes only specify operating temperature range and the maximum capacitance change over temperature. While capacitance change due to DC bias for X5R and X7R is better than Y5V and Z5U dielectrics, it can still be significant enough to drop capacitance below sufficient levels. As shown in Figure 6, capacitor DC bias characteristics tend to improve as component case size increases, but verification of expected capacitance at the operating voltage is highly **recommended**. Due to its good voltage coefficient in small case sizes, LTC recommends using Murata's GJ8 series ceramic capacitors.

### **High Vibration Environments**

Voltage and temperature coefficients are not the only sources of problems. Some ceramic capacitors have a piezoelectric response. A piezoelectric device generates voltage across its terminals due to mechanical stress upon it, similar to how a piezoelectric microphone works. For a ceramic capacitor, this stress can be induced by mechanical vibrations within the system or due to thermal transients.

LT3045 applications in high vibration environments have three distinct piezoelectric noise generators: ceramic output, input, and SET pin capacitors. However, due to LT3045's very low output impedance over a wide frequency range, negligible output noise is generated using

Figure 4. Ceramic Capacitor DC Bias Characteristics

Figure 5. Ceramic Capacitor Temperature Characteristics

Figure 6. Capacitor Voltage Coefficient for Different Case Sizes

a ceramic output capacitor. Similarly, due to LT3045's ultrahigh PSRR, negligible output noise is generated using a ceramic input capacitor. Nonetheless, given the high SET pin impedance, any piezoelectric response from a ceramic SET pin capacitor generates significant output noise – peak-to-peak excursions of hundreds of µVs. However, due to the SET pin capacitor's high ESR and ESL tolerance, any non-piezoelectrically responsive (tantalum, electrolytic, or film) capacitor can be used at the SET pin – although electrolytic capacitors tend to have high 1/f noise. In any case, use of a surface mount capacitor is highly recommended.

### **Stability and Input Capacitance**

The LT3045 is stable with a minimum  $4.7\mu FIN$  pin capacitor. LTC recommends using low ESR ceramic capacitors. In cases where long wires connect the power supply to the LT3045's input and ground terminals, the use of low value input capacitors combined with a large load current can result in instability. The resonant LC tank circuit formed by the wire inductance and the input capacitor is the cause and not because of LT3045's instability.

The self-inductance, or isolated inductance, of a wire is directly proportional to its length. The wire diameter, however, has less influence on its self-inductance. For example, the self-inductance of a 2-AWG isolated wire with a diameter of 0.26" is about half the inductance of a 30-AWG wire with a diameter of 0.01". One foot of 30-AWG wire has 465nH of self-inductance.

Several methods exist to reduce a wire's self-inductance. One method divides the current flowing towards the LT3045 between two parallel conductors. In this case, placing the wires further apart reduces the inductance; up to a 50% reduction when placed only a few inches apart. Splitting the wires connect two equal inductors in parallel. However, when placed in close proximity to each other, their mutual inductance adds to the overall self inductance of the wires — therefore a 50% reduction is not possible in such cases. The second and more effective technique to reduce the overall inductance is to place the forward and return current conductors (the input and ground wires) in close proximity. Two 30-AWG wires separated by 0.02" reduce the overall inductance to about one-fifth of a single wire.

If a battery mounted in close proximity powers the LT3045, a 4.7µF input capacitor suffices for stability. However, if a distantly located supply powers the LT3045, use a larger value input capacitor. Use a rough guideline of 1µF (in addition to the 4.7µF minimum) per 6" of wire length. The minimum input capacitance needed to stabilize the application also varies with the output capacitance as well as the load current. Placing additional capacitance on the LT3045's output helps. However, this requires significantly more capacitance compared to additional input bypassing. Series resistance between the supply and the LT3045 input also helps stabilize the application; as little as  $0.1\Omega$  to  $0.5\Omega$ suffices. This impedance dampens the LC tank circuit at the expense of dropout voltage. A better alternative is to use a higher ESR tantalum or electrolytic capacitor at the LT3045 input in parallel with a 4.7µF ceramic capacitor.

### **PSRR** and Input Capacitance

For applications utilizing the LT3045 for post-regulating switching converters, placing a capacitor directly at the LT3045 input results in ac current (at the switching frequency) to flow near the LT3045. This relatively highfrequency switching current generates a magnetic field that couples to the LT3045 output, thereby degrading its effective PSRR. While highly dependent on the PCB, the switching pre-regulator, the input capacitance, amongst other factors, the PSRR degradation can be easily over 30dB at 1MHz. This degradation is present even if the LT3045 is de-soldered from the board, because it effectively degrades the PSRR of the PC board itself. While negligible for conventional low PSRR LDOs, LT3045's ultrahigh PSRR requires careful attention to higher order parasitics in order to extract the full performance offered by the regulator.

To mitigate the flow of high-frequency switching current near the LT3045, the LT3045 input capacitor can be entirely removed -- as long as the switching converter's output capacitor is located more than an inch away from the LT3045. Magnetic coupling rapidly decreases with increasing distance. Nonetheless, if the switching pre-regulator is placed too far away (conservatively more than a couple inches) from the LT3045, with no input capacitor present, as with any regulator, the LT3045 input will oscillate at the

parasitic LC resonance frequency. Besides, it is generally a very common (and a preferred) practice to bypass regulator input with some capacitance. So this option is fairly limited in its scope and not the most palatable solution.

To that end, LTC recommends using the LT3045 demo board layout for achieving the best possible PSRR performance. The LT3045 demo board layout utilizes magnetic field cancellation techniques to prevent PSRR degradation caused by this high-frequency current flow—while utilizing the input capacitor.

### Filtering High Frequency Spikes

For applications where the LT3045 is used to post-regulate a switching converter, its high PSRR effectively suppresses any "noise" present at the switcher's switching frequency — typically 100kHz to 4MHz. However, the very high frequency (hundreds of MHz) "spikes" — beyond the LT3045's bandwidth — associated with the switcher's power switch transition times will almost directly pass through the LT3045. While the output capacitor is partly intended to absorb these spikes, its ESL will limit its ability at these frequencies. A ferrite bead or even the inductance associated with a short (e.g. 0.5") PCB trace between the switcher's output and the LT3045's input can serve as an LC-filter to suppress these very high frequency spikes.

### **Output Noise**

The LT3045 offers many advantages with respect to noise performance. Traditional linear regulators have several sources of noise. The most critical noise sources for a traditional regulator are its voltage reference, error amplifier, noise from the resistor divider network used for setting output voltage and the noise gain created by this resistor divider. Many low noise regulators pin out their voltage reference to allow for noise reduction by bypassing the reference voltage.

Unlike most linear regulators, the LT3045 does not use a voltage reference; instead, it uses a 100µA current reference. The current reference operates with typical noise current level of  $20pA/\sqrt{Hz}$  ( $6nA_{RMS}$  over a 10Hz to 100kHz bandwidth). The resultant voltage noise equals the current noise multiplied by the resistor value, which in turn is RMS summed with the error amplifier's noise and the resistor's

own noise of  $\sqrt{4kTR}$  — whereby k = Boltzmann's constant 1.38 • 10<sup>-23</sup>J/K and T is the absolute temperature.

One problem that conventional linear regulators face is that the resistor divider setting the output voltage gains up the reference noise. In contrast, the LT3045's unity-gain follower architecture presents no gain from the SET pin to the output. Therefore, if a capacitor bypasses the SET pin resistor, then the output noise is independent of the programmed output voltage. The resultant output noise is then set just by the error amplifier's noise — typically  $2nV/\sqrt{\text{Hz}}$  from 10kHz to 1MHz and  $0.8\mu V_{RMS}$  in a 10Hz to 100kHz bandwidth using a  $4.7\mu F$  SET pin capacitor. Paralleling multiple LT3045s further reduces noise by  $\sqrt{N}$ , for N parallel regulators.

Refer to the Typical Performance Characteristics section for noise spectral density and RMS integrated noise over various load currents and SET pin capacitances.

# Set Pin (Bypass) Capacitance: Noise, PSRR, Transient Response and Soft-Start

In addition to reducing output noise, using a SET pin bypass capacitor also improves PSRR and transient performance. Note that any bypass capacitor leakage deteriorates the LT3045's DC regulation. Capacitor leakage of even 100nA is a 0.1% DC error. Therefore, LTC recommends the use of a good quality low leakage ceramic capacitor.

Using a SET pin bypass capacitor also soft-starts the output and limits inrush current. The RC time constant, formed by the SET pin resistor and capacitor, controls soft-start time. Ramp-up rate from 0 to 90% of nominal  $V_{OLIT}$  is:

$$t_{SS} \approx 2.3 \bullet R_{SET} \bullet C_{SET}$$

(Fast Start-Up Disabled)

### Fast Start-Up

For ultralow noise applications that require low 1/f noise (i.e. at frequencies below 100Hz), a larger value SET pin capacitor is required, up to  $22\mu F$ . While this would normally significantly increase the regulator's start-up time, the LT3045 incorporates fast start-up circuitry that increases the SET pin current to about 2mA during start-up.

As shown in the Block Diagram, the 2mA current source remains engaged while PGFB is below 300mV, unless the

regulator is in current limit, dropout, thermal shutdown or input voltage is below minimum  $V_{\text{IN}}$ .

If fast start-up capability is not used, tie PGFB to IN or to OUT for output voltages above 300mV. Note that doing so also disables power good functionality.

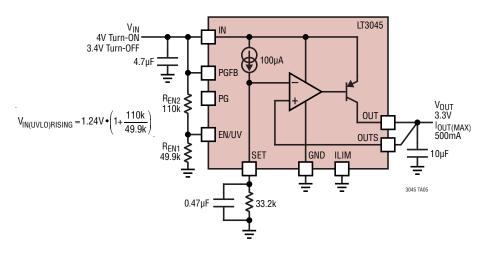

### **ENABLE/UVLO**

The EN/UV pin is used to put the regulator into a micropower shutdown state. The LT3045 has an accurate 1.24V turn-on threshold on the EN/UV pin with 130mV of hysteresis. This threshold can be used in conjunction with a resistor divider from the input supply to define an accurate undervoltage lockout (UVLO) threshold for the regulator. The EN/UV pin current ( $I_{EN}$ ) at the threshold from the Electrical Characteristics table needs to be considered when calculating the resistor divider network:

$$V_{IN(UVLO)} = 1.24V \bullet \left(1 + \frac{R_{EN2}}{R_{EN1}}\right) + I_{EN} \bullet R_{EN2}$$

The EN/UV pin current ( $I_{EN}$ ) can be ignored if  $R_{EN1}$  is less than 100k. If unused, tie EN/UV pin to IN.

### **Programmable Power Good**

As illustrated in the Block Diagram, power good threshold is user programmable using the ratio of two external resistors, R<sub>PG2</sub> and R<sub>PG1</sub>:

$$V_{OUT(PG\_THRESHOLD)} = 0.3V \bullet \left(1 + \frac{R_{PG2}}{R_{PG1}}\right) - I_{PGFB} \bullet R_{PG2}$$

If the PGFB pin increases above 300mV, the open-collector PG pin de-asserts and becomes high impedance. The power good comparator has 7mV hysteresis and 5 $\mu$ s of deglitching. The PGFB pin current (I<sub>PGFB</sub>) from the Electrical Characteristics table must be considered when determining the resistor divider network. The PGFB pin current (I<sub>PGFB</sub>) can be ignored if R<sub>PG1</sub> is less than 30k. If power good functionality is not used, float the PG pin. Please note that programmable power good and fast start-up capabilities are disabled for output voltages below 300mV.

The power good functionality is disabled in shutdown, i.e. when EN/UV is set to 0V. If power good functionality

is desired in shutdown, tie the power good resistor (i.e. RPG in the Block Diagram) between the PG pin and either the EN/UV or OUT pins.

### **Externally Programmable Current Limit**

The ILIM pin's current limit threshold is 300mV. Connecting a resistor from ILIM to GND sets the maximum current flowing out of the ILIM pin, which in turn programs the LT3045's current limit. With a 150mA  $\bullet$  k $\Omega$  programming scale factor, the current limit can be calculated as follows:

Current Limit =

$$\frac{150 \text{mA} \cdot k\Omega}{R_{\text{ILIM}}}$$

For example, a  $1k\Omega$  resistor programs the current limit to 150mA and a  $2k\Omega$  resistor programs the current limit to 75mA. For good accuracy, Kelvin connect this resistor to the LT3045's GND pin.

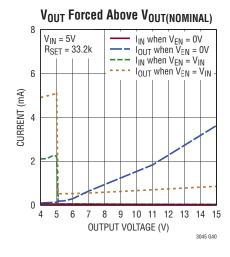

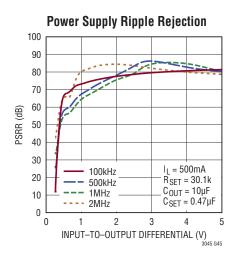

In cases where IN-to-OUT differential is greater than 12V, the LT3045's foldback circuitry decreases the internal current limit. As a result, internal current limit may override the externally programmed current limit level to keep the LT3045 within its safe-operating-area (SOA). See the Internal Current Limit vs Input-to-Output Differential graph in the Typical Performance Characteristics section.

As shown in the Block Diagram, the ILIM pin sources current proportional (1:500) to output current; therefore, it also serves as a current monitoring pin with a 0V to 300mV range. If external current limit or current monitoring is not used, tie ILIM to GND.

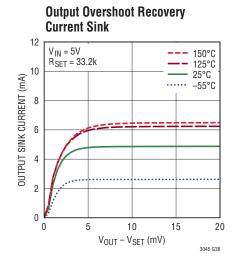

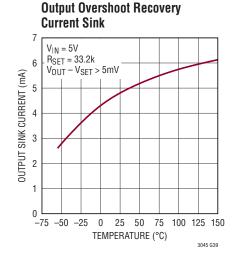

### **Output Overshoot Recovery**

During a load step from full load to no load (or light load), the output voltage overshoots before the regulator responds to turn the power transistor OFF. Given that there is no load (or very light load) present at the output, it takes a long time to discharge the output capacitor.

As illustrated in the Block Diagram, the LT3045 incorporates an overshoot recovery circuitry that turns on a current sink to discharge the output capacitor in the event OUTS is higher than SET. This current is typically about 4mA. No load recovery is disabled for input voltages less than 2.5V or output voltages less than 1.5V.

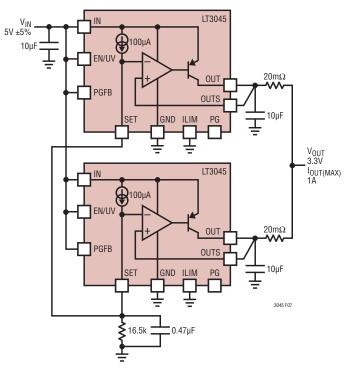

Figure 7. Parallel Devices

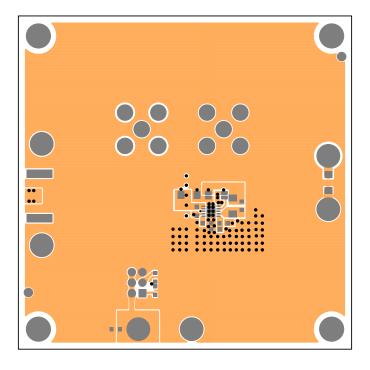

Figure 8. Recommended DFN Layout

If OUTS is externally held above SET, the current sink turns ON in an attempt to restore OUTS to its programmed voltage. The current sink remains ON until the external circuitry releases OUTS.

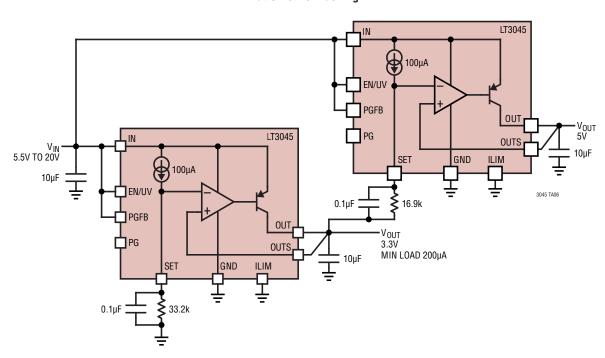

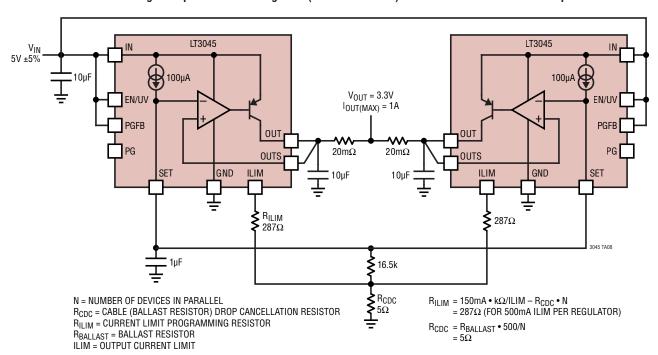

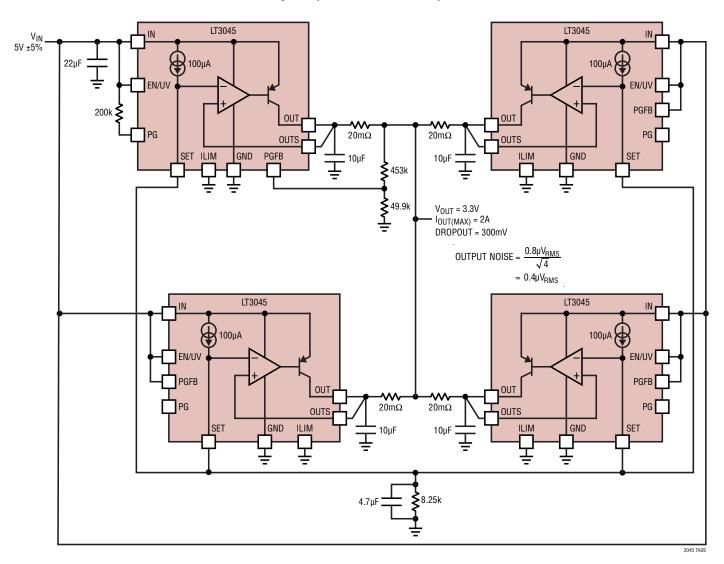

### **Direct Paralleling for Higher Current**

Higher output current is obtained by paralleling multiple LT3045s. Tie all SET pins together and all IN pins together. Connect the OUT pins together using small pieces of PCB trace (used as a ballast resistor) to equalize currents in the LT3045s. PCB trace resistance in milliohms/inch is shown in Table 2.

Table 2. PC Board Trace Resistance

| WEIGHT (oz) | 10mil WIDTH | 20mil WIDTH |

|-------------|-------------|-------------|

| 1           | 54.3        | 27.1        |

| 2           | 27.1        | 13.6        |

Trace resistance is measured in  $m\Omega$ /in.

The small worst-case offset of 2mV for each paralleled LT3045 minimizes the required ballast resistor value. Figure 7 illustrates that two LT3045s, each using a  $20m\Omega$  PCB trace ballast resistor, provide better than 20% accurate output current sharing at full load. The two  $20m\Omega$  external resistors only add 10mV of output regulation drop with a 1A maximum current. With a 3.3V output, this only adds 0.3% to the regulation accuracy. As has been discussed previously, tie the OUTS pin directly to the output capacitor.

More than two LT3045s can also be paralleled for even higher output current and lower output noise. Paralleling multiple LT3045s is also useful for distributing heat on the PCB. For applications with high input-to-output voltage differential, an input series resistor or resistor in parallel with the LT3045 can also be used to spread heat.

### **PCB Layout Considerations**

Given the LT3045's high bandwidth and ultrahigh PSRR, careful PCB layout must be employed to achieve full device performance. Figure 8 shows a recommended layout that delivers full performance of the regulator. Refer to the LT3045's DC2491A demo board manual for further details.

### **Thermal Considerations**

The LT3045 has internal power and thermal limiting circuits that protect the device under overload conditions. The thermal shutdown temperature is nominally 165°C with about 8°C of hysteresis. For continuous normal load conditions, do not exceed the maximum junction temperature (125°C for E- and I-grades and 150°C for H- and MP-Grades). It is important to consider all sources of thermal resistance from junction to ambient. This includes junction-to-case, case-to-heat sink interface, heat sink resistance or circuit board-to-ambient as the application dictates. Additionally, consider all heat sources in close proximity to the LT3045.

The undersides of the DFN and MSOP packages have exposed metal from the lead frame to the die attachment. Both packages allow heat to directly transfer from the die junction to the PCB metal to limit maximum operating junction temperature. The dual-in-line pin arrangement allows metal to extend beyond the ends of the package on the topside (component side) of the PCB.

For surface mount devices, heat sinking is accomplished by using the heat spreading capabilities of the PCB and its copper traces. Copper board stiffeners and plated throughholes can also be used to spread the heat generated by the regulator.

Table 3 and Table 4 list thermal resistance as a function of copper area on a fixed board size. All measurements were taken in still air on a 4 layer FR-4 board with 1oz solid internal planes and 2oz top/bottom planes with a total board thickness of 1.6mm. The four layers were electrically isolated with no thermal vias present. PCB layers, copper weight, board layout and thermal vias affect the resultant thermal resistance. For more information on thermal resistance and high thermal conductivity test boards, refer to JEDEC standard JESD51, notably JESD51-7 and JESD51-12. Achieving low thermal resistance necessitates attention to detail and careful PCB layout.

Table 3. Measured Thermal Resistance for DFN Package

| COPPE               | COPPER AREA         |                     | THERMAL    |  |

|---------------------|---------------------|---------------------|------------|--|

| TOP SIDE*           | BOTTOM SIDE         | BOARD AREA          | RESISTANCE |  |

| 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 34°C/W     |  |

| 1000mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 34°C/W     |  |

| 225mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 35°C/W     |  |

| 100mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 36°C/W     |  |

<sup>\*</sup>Device is mounted on topside

Table 4. Measured Thermal Resistance for MSOP Package

| COPPER AREA         |                     |                     | THERMAL    |

|---------------------|---------------------|---------------------|------------|

| TOP SIDE*           | BOTTOM SIDE         | BOARD AREA          | RESISTANCE |

| 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 33°C/W     |

| 1000mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 33°C/W     |

| 225mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 34°C/W     |

| 100mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 35°C/W     |

<sup>\*</sup>Device is mounted on topside

### **Calculating Junction Temperature**

Example: Given an output voltage of 3.3V and input voltage of  $5V \pm 5\%$ , output current range from 1mA to 500mA, and a maximum ambient temperature of  $85^{\circ}$ C, what is the maximum junction temperature?

The LT3045's power dissipation is:

$$I_{OUT(MAX)} \bullet (V_{IN(MAX)} - V_{OUT}) + I_{GND} \bullet V_{IN(MAX)}$$

where:

$I_{OUT(MAX)} = 500 \text{mA}$

$V_{IN(MAX)} = 5.25V$

$I_{GND}$  (at  $I_{OUT}$  = 500mA and  $V_{IN}$  = 5.25V) = 12.5mA thus:

$P_{DISS} = 0.5A \cdot (5.25V - 3.3V) + 12.5mA \cdot 5.25V = 1W$

Using a DFN package, the thermal resistance is in the range of 34°C/W to 36°C/W depending on the copper area. Therefore, the junction temperature rise above ambient approximately equals:

The maximum junction temperature equals the maximum ambient temperature plus the maximum junction temperature rise above ambient:

$$T_{\text{JMAX}} = 85^{\circ}\text{C} + 35^{\circ}\text{C} = 120^{\circ}\text{C}$$

### **Overload Recovery**

Like many IC power regulators, the LT3045 incorporates safe-operating-area (SOA) protection. The SOA protection activates at input-to-output differential voltages greater than 12V. The SOA protection decreases the current limit as the input-to-output differential increases and keeps the power transistor inside a safe operating region for all values of input-to-output voltages up to the LT3045's absolute maximum ratings. The LT3045 provides some level of output current for all values of input-to-output differentials. Refer to the Current Limit curves in the Typical Performance Characteristics section. When power is first applied and input voltage rises, the output follows the input and keeps the input-to-output differential low to allow the regulator to supply large output current and start-up into high current loads.

Due to current limit foldback, however, at high input voltages a problem can occur if the output voltage is low and the load current is high. Such situations occur after the removal of a short-circuit or if the EN/UV pin is pulled high after the input voltage has already turned ON. The load line in such cases intersects the output current profile at two points. The regulator now has two stable operating points. With this double intersection, the input power supply may need to be cycled down to zero and brought back up again to make the output recover. Other linear regulators with foldback current limit protection (such as the LT1965 and LT1963A) also exhibit this phenomenon, so it is not unique to the LT3045.

### **Protection Features**