## 60V, 300W Hybrid Step-Down µModule Bus Converter

### **FEATURES**

- Input Voltage Range: 30V to 60V (65V Abs. Max.)

- Wide Output Voltage: 4.5V to 18V  $(V_{OIIT} < V_{IN}/2)$

- 97.3% Peak Efficiency (12V<sub>OUT</sub> at 15A, 48V<sub>IN</sub>)

- ±1.5% Maximum Total DC Output Error

- Up to 300W Output Power

- Scalable: Parallel LTM4660s for Higher Power

- Fixed Frequency Current Mode Control

- Phase-Lockable External Synchronization from 200kHz to 1MHz

- Low Start-Up Inrush Current with Flying Capacitor Voltage-Balancing Prior to DC/DC Switching Action

- Output Voltage Tracking with Soft-Start

- Short-Circuit Protection with Adjustable Retry-Timer

- Overcurrent and Overtemperature Protection

- **Onboard Diode Temperature Monitor**

- Optional External Reference Input

- Power Good and FAULT Indicators

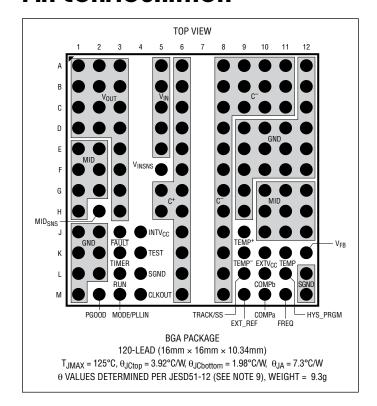

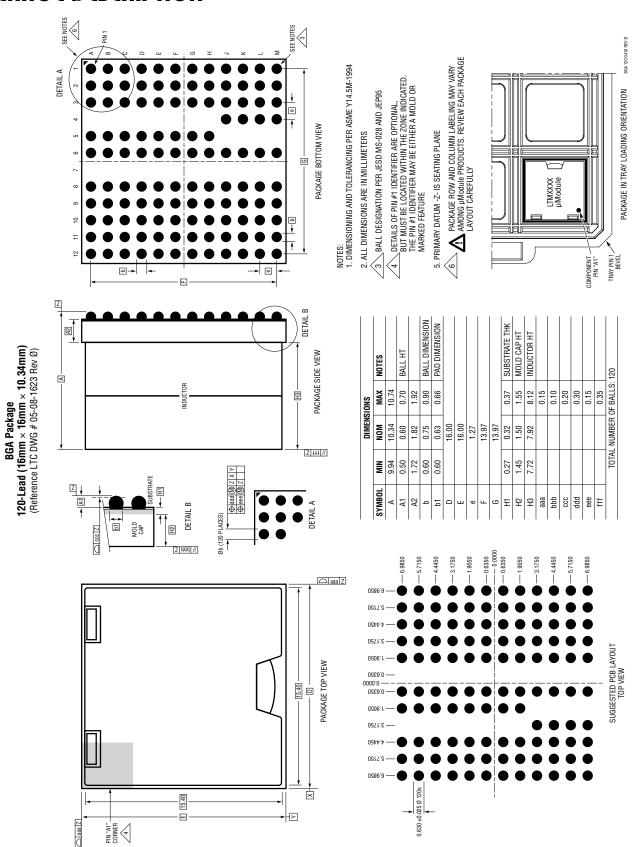

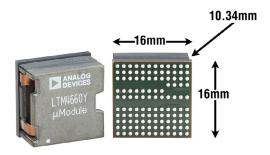

- 16mm × 16mm × 10.34mm BGA Package

## **APPLICATIONS**

- Telecom, Data Centers and Networking Equipment

- Industrial and Test Equipment

## DESCRIPTION

The LTM<sup>®</sup>4660 is a complete 300W output switching mode hybrid-topology step-down DC/DC μModule® (micromodule) nonisolated bus converter. Its exposed power inductor resides on the top of the package, providing an intrinsic path for heat to dissipate up and out of the module—away from one's printed circuit board. Included in the package are the switching controller IC, power MOSFETs and supporting components. Only flying (charge-pump) capacitors, bulk input and output bypass capacitors, and a few configuration passives are needed.

The LTM4660 features frequency synchronization, Burst Mode® operation and output voltage soft-start and tracking. An onboard temperature diode is available for temperature monitoring. The LTM4660 protects against short-circuit, overcurrent, and overtemperature faults. For higher power applications, multiple LTM4660 modules can be easily paralleled.

The LTM4660 is offered in a 16mm × 16mm × 10.34mm BGA package with RoHS compliant terminal finish.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 9484799.

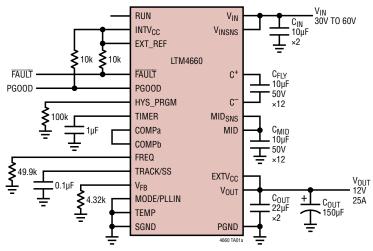

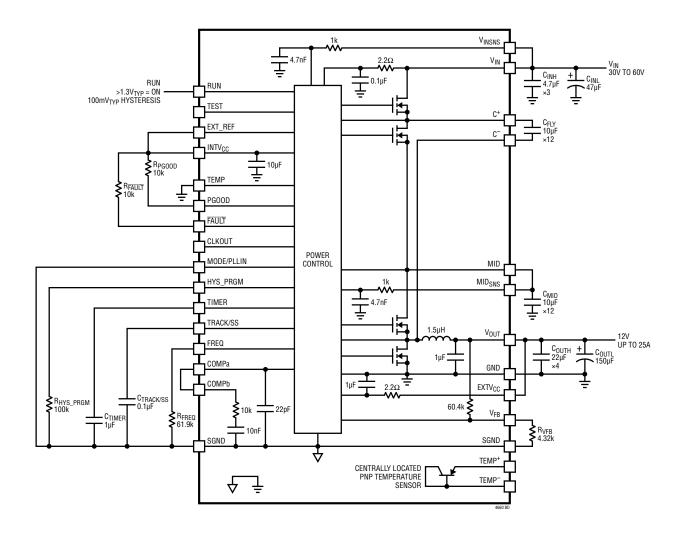

## TYPICAL APPLICATION

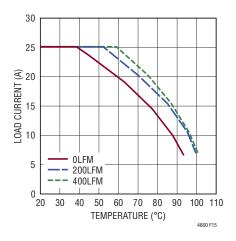

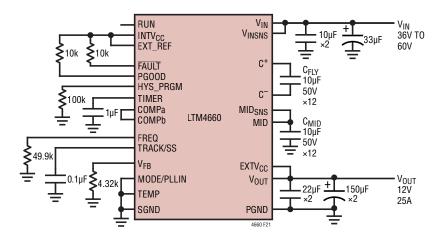

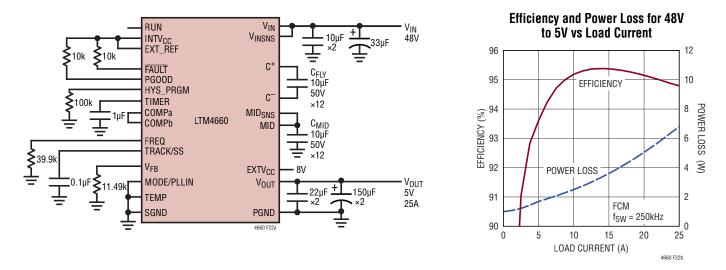

12V, 25A DC/DC µModule Nonisolated Bus Converter

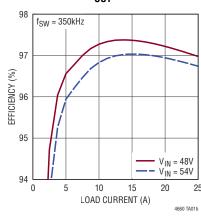

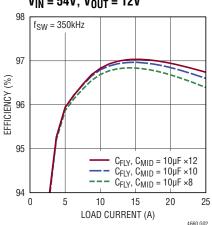

**Efficiency vs Load Current**  $V_{OUT} = 12V$

PINS NOT USED IN THIS CIRCUIT: CLKOUT. TEMP+. TEMP

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Terminal Voltages                                               |

|-----------------------------------------------------------------|

| V <sub>IN</sub> , V <sub>INSNS</sub> 0.3V to 65V                |

| V <sub>OUT</sub> , EXTV <sub>CC</sub> , PGOOD, FAULT0.3V to 20V |

| MID, MID <sub>SNS</sub> –0.3V to 32.5V                          |

| RUN, FREQ, HYS_PRGM, TEMP, V <sub>FB</sub> , TRACK/SS,          |

| TIMER, MODE/PLLIN, EXT_REF –0.3V to INTV <sub>CC</sub>          |

| Terminal Currents                                               |

| TEMP <sup>+</sup> –1mA to 1mA                                   |

| TEMP <sup>-</sup> 1mA to 1mA                                    |

| Temperatures                                                    |

| Internal Operating Temperature                                  |

| Range (Note 2)40°C to 125°C                                     |

| Storage Temperature Range55°C to 125°C                          |

| Peak Package Body Temperature                                   |

| During Reflow245°C                                              |

| ·                                                               |

(All Voltages Relative to GND Unless Otherwise Indicated)

## PIN CONFIGURATION

## ORDER INFORMATION

|               |                     | PART N     | MARKING     | PACKAGE | MSL    | TEMPERATURE RANGE |  |

|---------------|---------------------|------------|-------------|---------|--------|-------------------|--|

| PART NUMBER   | PAD OR BALL FINISH* | DEVICE     | FINISH CODE | TYPE    | RATING | (SEE NOTE 2)      |  |

| LTM4660EY#PBF | CACOOE (DoUC)       | LTM4660Y   | 01          | BGA     | 4      | -40°C to 125°C    |  |

| LTM4660IY#PBF | SAC305 (RoHS)       | L11V140001 | e1          | DGA     | 4      | -40 6 10 125 6    |  |

- Contact the factory for parts specified with wider operating temperature ranges. \*Pad or ball finish code is per IPC/JEDEC J-STD-609.

- Device temperature grade is indicated by a label on the shipping container.

- Recommended LGA and BGA PCB Assembly and Manufacturing Procedures

- LGA and BGA Package and Tray Drawings

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over specified internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = V_{INSNS} = 54V$ ,  $V_{OUT} = 12V$  and  $EXTV_{CC} = 12V$  (see Note 4). Configured per Block Diagram circuit with no output load unless otherwise noted.

| SYMBOL                        | PARAMETER                                              | CONDITIONS                                                                                                                                                                                                                                                          |   | MIN   | TYP         | MAX   | UNITS      |

|-------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-------------|-------|------------|

| V <sub>IN(DC)</sub>           | Input DC Voltage                                       |                                                                                                                                                                                                                                                                     | • | 30    |             | 60    | V          |

| V <sub>OUT(RANGE)</sub>       | Output Voltage, Supported Range of Regulation          | V <sub>IN</sub> = 54V                                                                                                                                                                                                                                               | • | 4.5   |             | 18    | V          |

| V <sub>OUT(DC)</sub>          | Output Voltage Variation                               | V <sub>OUT</sub> = 12V, I <sub>OUT</sub> = 15A (Notes 3, 5)                                                                                                                                                                                                         | • | 11.8  | 12          | 12.2  | ٧          |

| Input Specification           | ons                                                    |                                                                                                                                                                                                                                                                     |   |       |             |       |            |

| V <sub>IN(UVLO)</sub>         | Undervoltage Lockout Threshold                         | V <sub>IN</sub> Rising<br>Hysteresis                                                                                                                                                                                                                                | • |       | 8.8<br>0.38 | 9.4   | V<br>V     |

| I <sub>S(VIN, FCM)</sub>      | Input Supply Power Current, in Forced Continuous Mode  | MODE/PLLIN = 0V, I <sub>OUT</sub> = 0A (Note 6)<br>MODE/PLLIN = 0V, I <sub>OUT</sub> = 0.5A                                                                                                                                                                         |   |       | 38<br>150   |       | mA<br>mA   |

| I <sub>S(VIN, PS)</sub>       | Input Supply Power Current, in Pulse-<br>Skipping Mode | MODE/PLLIN = INTV <sub>CC</sub> , I <sub>OUT</sub> = 0.5A                                                                                                                                                                                                           |   |       | 135         |       | mA         |

| I <sub>S(VIN, BM)</sub>       | Input Supply Power Current, in Burst Mode              | MODE/PLLIN = Open Circuit, I <sub>OUT</sub> = 0.5A                                                                                                                                                                                                                  |   |       | 120         |       | mA         |

| I <sub>S(VIN, SHUTDOWN)</sub> | Input Supply Power Current in Shutdown                 | Shutdown, V <sub>RUN</sub> = 0V                                                                                                                                                                                                                                     |   |       | 300         |       | μA         |

| Output Specificat             | tions                                                  |                                                                                                                                                                                                                                                                     |   |       |             |       |            |

| I <sub>OUT(DC)</sub>          | Output Continuous Current Range                        | (Note 3)                                                                                                                                                                                                                                                            |   | 0     |             | 25    | A          |

| $\Delta V_{OUT}/V_{OUT}$      | Line Regulation Accuracy                               | $30 \le V_{IN} \le 60V$ , $I_{OUT} = 0A$                                                                                                                                                                                                                            |   |       | 0.003       | 0.2   | %/V        |

|                               | Load Regulation Accuracy                               | $I_{OUT}$ =15A $30 \le V_{IN} \le 60V$ , $0A \le I_{OUT} \le 25A$ (Note 7)                                                                                                                                                                                          | • |       | 0.5         | 1.5   | %<br>%     |

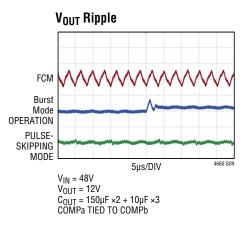

| $\Delta V_{OUT(AC)}$          | Output Voltage Ripple                                  |                                                                                                                                                                                                                                                                     |   |       | 150         |       | $mV_{P-P}$ |

| f <sub>s</sub>                | V <sub>OUT</sub> Ripple Frequency                      | $R_{FREQ} = 61.9k\Omega$ , $I_{OUT} = 0A$                                                                                                                                                                                                                           |   |       | 450         |       | kHz        |

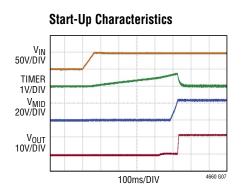

| t <sub>Start-Up</sub>         | Turn-On Start-Up Time                                  | Capacitor Balancing – Delay Measured from Toggling RUN on to MID Reaching $V_{IN}/2$ , $C_{TIMER}=1.47\mu\text{F}$ , $C_{MID}$ and $C_{FLY}=10\mu\text{F}\times12$ Delay Measured from MID Reaching $V_{IN}/2$ to PGOOD Exceeding 3V, $C_{TRACK/SS}=0.1\mu\text{F}$ |   |       | 300<br>5    |       | ms<br>ms   |

| $\Delta V_{OUT(LS)}$          | Peak Output Voltage Deviation for Dynamic<br>Load Step | Load: 0W to 150W in 1 $\mu$ s and 150W to 0W in 1 $\mu$ s C <sub>0UT</sub> =150 $\mu$ F ×2, 10 $\mu$ F ×3 (Note 7)                                                                                                                                                  |   |       | 0.3         |       | V          |

| t <sub>SETTLE</sub>           | Settling Time for Dynamic Load Step                    | Load: 0W to 150W in 1 $\mu$ s and 150W to 0W in 1 $\mu$ s C <sub>0UT</sub> =150 $\mu$ F ×2, 10 $\mu$ F ×3 (Note 7)                                                                                                                                                  |   |       | 300         |       | μs         |

| <b>Control Section</b>        |                                                        |                                                                                                                                                                                                                                                                     |   |       |             |       |            |

| $V_{VFB}$                     | Regulated V <sub>FB</sub> Pin Feedback Voltage         | $I_{OUT} = 0A$ , $V_{OUT} = 12V$                                                                                                                                                                                                                                    | • | 0.792 | 0.8         | 0.808 | V          |

| I <sub>VFB</sub>              | V <sub>FB</sub> Pin Leakage Current                    | (Note 8)                                                                                                                                                                                                                                                            |   |       | ±10         |       | nA         |

| I <sub>TRACK/SS</sub>         | Soft-Start Charge Current                              | V <sub>TRACK/SS</sub> = 0V                                                                                                                                                                                                                                          |   | -9    | -10         | -11   | μA         |

| Monitors                      |                                                        |                                                                                                                                                                                                                                                                     |   |       |             |       |            |

| I <sub>VINSNS</sub>           | V <sub>INSNS</sub> Bias Current                        | V <sub>RUN</sub> = 5V, Normal Mode<br>V <sub>RUN</sub> = 0V, Shutdown                                                                                                                                                                                               |   |       | 1<br>45     |       | mA<br>μA   |

| RUN Enable Pin                | S                                                      |                                                                                                                                                                                                                                                                     |   |       |             |       |            |

| $\overline{V_{RUN}}$          | RUN Turn-On Threshold                                  | V <sub>RUN</sub> Rising                                                                                                                                                                                                                                             | • | 1.1   | 1.3         | 1.6   | V          |

| V <sub>RUN, HYS</sub>         | RUN Hysteresis                                         |                                                                                                                                                                                                                                                                     |   |       | 100         |       | mV         |

| I <sub>RUN</sub>              | RUN Pull-Up Current                                    | V <sub>RUN</sub> = 0V                                                                                                                                                                                                                                               |   |       | 1           |       | μА         |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over specified internal operating temperature range, otherwise specifications are at  $T_A = 25\,^{\circ}\text{C}$  (Note 2).  $V_{IN} = V_{INSNS} = 54V$ ,  $V_{OUT} = 12V$  and  $EXTV_{CC} = 12V$  (see Note 4). Configured per Block Diagram circuit with no output load unless otherwise noted.

| SYMBOL                      | PARAMETER                                                                                            | CONDITIONS                                                                                                                               |   | MIN      | TYP                  | MAX      | UNITS       |

|-----------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|----------|----------------------|----------|-------------|

| Capacitor Voltag            | je-Balancing                                                                                         | ,                                                                                                                                        |   |          |                      |          |             |

| V <sub>TIMER_LOW</sub>      | Voltage at TIMER Pin to Start Capacitor<br>Balancing                                                 |                                                                                                                                          |   |          | 0.5                  |          | V           |

| V <sub>TIMER_HIGH</sub>     | Voltage at TIMER Pin to Stop Capacitor<br>Balancing                                                  |                                                                                                                                          |   |          | 1.25                 |          | V           |

| I <sub>TIMER</sub>          | TIMER Pin Charge Current                                                                             | V <sub>TIMER</sub> = 0.9V<br>V <sub>TIMER</sub> = 2.8V                                                                                   | • | -6<br>-3 | −7<br>−3.5           | -8<br>-4 | μA<br>μA    |

| V <sub>HYS_PRGM</sub>       | Capacitor Balancing Window Comparator<br>Threshold                                                   | V <sub>HYS_PRGM</sub> = 0V<br>V <sub>HYS_PRGM</sub> = 1.2V<br>V <sub>HYS_PRGM</sub> = INTV <sub>CC</sub>                                 |   |          | ±0.3<br>±1.2<br>±0.8 |          | V<br>V<br>V |

| I <sub>HYS_PRGM</sub>       | HYS_PRGM Pin Current                                                                                 | V <sub>HYS_PRGM</sub> = 0V                                                                                                               | • | -9       | -10                  | -11      | μА          |

| V <sub>FAULT</sub>          | FAULT Pin Voltage Low                                                                                | I <sub>FAULT</sub> = 0.6mA                                                                                                               |   |          | 0.2                  | 0.4      | V           |

| I <sub>FAULT</sub>          | FAULT Leakage Current                                                                                | V <sub>FAULT</sub> = 20V                                                                                                                 |   |          |                      | 1        | μA          |

| Ic <sup>+</sup> (SOURCE)    | Current Out of C+ During Capacitor Balancing                                                         | $V_{C}^{+}$ to $V_{C}^{-} < V_{IN}/2$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8)                                                      |   |          | 40                   |          | mA          |

| I <sub>C</sub> +(SINK)      | Current Into C+ During Capacitor Balancing                                                           | $V_{C}^{+}$ to $V_{C}^{-} > V_{IN}/2$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8)                                                      |   |          | 6                    |          | mA          |

| I <sub>C</sub> (SINK)       | Current Into C <sup>-</sup> During Capacitor Balancing                                               | $V_{C}^{+}$ to $V_{C}^{-} < V_{IN}/2$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8)                                                      |   |          | 40                   |          | mA          |

| I <sub>C</sub> -(SOURCE)    | Current Out of C <sup>-</sup> During Capacitor Balancing                                             | $V_{C}^{+}$ to $V_{C}^{-} > V_{IN}/2$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8)                                                      |   |          | 6                    |          | mA          |

| I <sub>MID</sub> (SOURCE)   | Current Out of MID During Capacitor Balancing                                                        | $V_{MID} < V_{IN}/2$ , $V_{MID} = V_{MID\_SNS} = 23V$ , $V_{C}^{+}$ to $V_{C}^{-} \ge 27V$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8) |   |          | 60                   |          | mA          |

| I <sub>MID(SINK)</sub>      | Current Into MID During Capacitor Balancing                                                          | $V_{MID} > V_{IN}/2$ , $V_{MID} = V_{MID\_SNS} = 31V$ , $V_{C}^{+}$ to $V_{C}^{-} \ge 27V$ , $V_{C}^{-} = 12V$ , $V_{IN} = 48V$ (Note 8) |   |          | 40                   |          | mA          |

| Oscillator and Ti           | imer Circuits                                                                                        |                                                                                                                                          |   |          |                      |          |             |

| f <sub>SYNC(RANGE)</sub>    | External Frequency Synchronization Range                                                             |                                                                                                                                          |   | 200      |                      | 1000     | kHz         |

| f <sub>SW</sub>             | Nominal Switching Frequency                                                                          | $R_{FREQ} = 61.9k\Omega$                                                                                                                 |   |          | 450                  |          | kHz         |

| I <sub>FREQ</sub>           | FREQ Setting Current                                                                                 | V <sub>FREQ</sub> = 0V (Note 8)                                                                                                          |   | -9.5     | -10                  | -10.5    | μA          |

| Power Good                  |                                                                                                      |                                                                                                                                          |   |          |                      |          |             |

| R <sub>PGOOD</sub>          | PGOOD Pull-Down Resistance                                                                           | I <sub>PG00D</sub> = 0.6mA                                                                                                               |   |          | 650                  |          | Ω           |

| I <sub>PGOOD_LEAK</sub>     | PGOOD Leakage Current                                                                                | V <sub>PG00D</sub> = 20V                                                                                                                 |   |          |                      | ±1       | μA          |

| INTV <sub>CC</sub> Regulato | or and EXTV <sub>CC</sub> Circuits                                                                   |                                                                                                                                          |   |          |                      | ,        |             |

| V <sub>INTVCC_INT</sub>     | INTV <sub>CC</sub> Voltage No Load                                                                   | $10V \le V_{IN} \le 60V$ , $V_{EXTVCC} = 0V$                                                                                             | • | 5.65     |                      | 5.95     | V           |

|                             | INTV <sub>CC</sub> Load Regulation                                                                   | I <sub>INTVCC</sub> = 0 to 50mA, V <sub>EXTVCC</sub> = 0V                                                                                |   |          | 0.8                  | ±2       | %           |

| V <sub>INTVCC_EXT</sub>     | INTV <sub>CC</sub> Voltage No Load with EXTV <sub>CC</sub> Bias                                      | 12V < V <sub>EXTVCC</sub> < 18V                                                                                                          |   | 5.65     | 5.8                  | 5.95     | V           |

|                             | INTV <sub>CC</sub> Load Regulation with EXTV <sub>CC</sub> Bias                                      | I <sub>INTVCC</sub> = 0 to 50mA, V <sub>EXTVCC</sub> = 12V                                                                               |   |          | 0.5                  | ±2       | %           |

|                             | EXTV <sub>CC</sub> Switchover Voltage                                                                | EXTV <sub>CC</sub> Ramping Positive                                                                                                      |   |          | 7                    |          | V           |

|                             | EXTV <sub>CC</sub> Hysteresis                                                                        |                                                                                                                                          |   |          | 200                  |          | mV          |

| Temperature Ser             | nsor                                                                                                 |                                                                                                                                          | ! |          |                      |          |             |

| $\Delta V_{TEMP}$           | Temperature Sensor Forward Voltage, V <sub>TEMP</sub> <sup>+</sup> to V <sub>TEMP</sub> <sup>-</sup> | I <sub>TEMP</sub> <sup>+</sup> = 100μA and I <sub>TEMP</sub> <sup>-</sup> = -100 μA at<br>T <sub>A</sub> = 25°C                          |   |          | 0.6                  |          | V           |

| $TC_{\Delta V(TEMP)}$       | ΔV <sub>TEMP</sub> Temperature Coefficient                                                           |                                                                                                                                          |   |          | -2.0                 | ,        | mV/°C       |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listing under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating conditions for extended periods may affect device reliability and lifetime.

Note 2: The LTM4660 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTM4660E is guaranteed to meet performance specifications over the 0°C to 125°C internal operating temperature range. Specifications over the full –40°C to 125°C internal operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTM4660I is guaranteed to meet specifications over the full internal operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

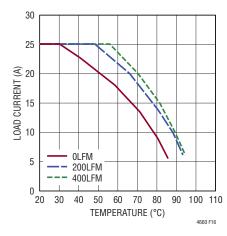

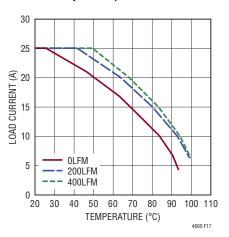

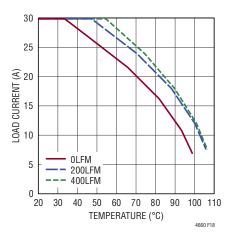

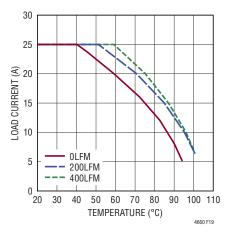

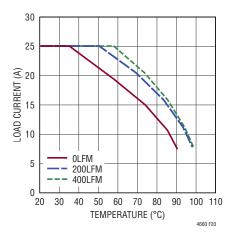

**Note 3:** See output current derating curves for different  $V_{IN}$ ,  $V_{OUT}$ , and  $T_{A}$ , located in the Applications Information section.

**Note 4:** To reduce internal module temperature rise, it is recommended to bias EXTV<sub>CC</sub>. For applications where  $V_{OUT} > 8V$ , tie  $V_{OUT}$  to EXTV<sub>CC</sub>. For applications where  $V_{OUT} < 8V$ , it is strongly recommended to drive EXTV<sub>CC</sub> with an auxiliary supply.

**Note 5:** Total DC output voltage error includes all errors over temperature: line and load regulation as well as the tolerance of the  $60.4 k\Omega$  feedback resistor internally connecting  $V_{OUT}$  to  $V_{FB}$ .

**Note 6:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency in forced continuous mode operation. See Applications Information.

Note 7: Guaranteed by design. Validated from bench measurements.

Note 8: ATE-tested at wafer sort only.

**Note 9:**  $\theta_{JA}$  value obtained from demo board DC2879A. Refer to Thermal Considerations in Applications Information section.

## TYPICAL PERFORMANCE CHARACTERISTICS

**Efficiency vs Output Current**  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$

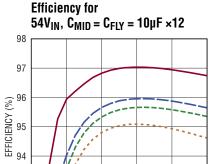

**Efficiency vs Output Current**  $V_{IN} = 54V, V_{OUT} = 12V$

12V<sub>OUT</sub>, 350kHz 9V<sub>OUT</sub>, 450kHz 7.5V<sub>OUT</sub>, 400kHz 5V<sub>OUT</sub>, 250kHz

20

25

4660 G03

**Efficiency for**

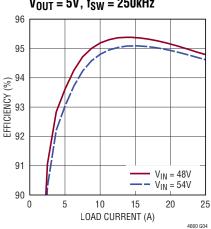

$V_{OUT} = 5V$ ,  $f_{SW} = 250$ kHz

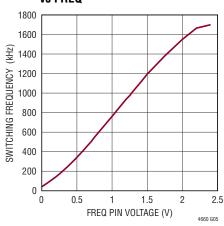

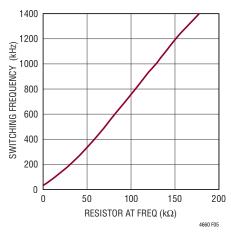

**Switching Frequency** vs FREQ

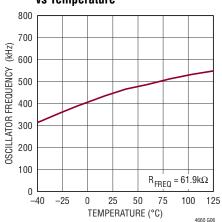

**Oscillator Frequency** vs Temperature

10

15

LOAD CURRENT (A)

5

93

92

0

## TYPICAL PERFORMANCE CHARACTERISTICS

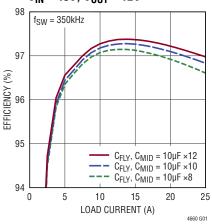

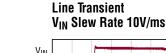

$V_{OUT} = 12V$   $P_{OUT} = 300W$  $C_{MID}$  AND  $C_{FLY} = 10 \mu F \times 12$

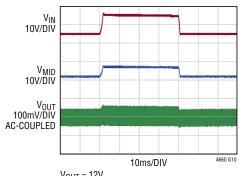

#### **Load Transient** 12.5A to 25A to 12.5A

$V_{IN} = 48V$   $V_{OUT} = 12V$   $C_{OUT} = 150 \mu F \times 2 + 10 \mu F \times 3$   $COMPa\ TIED\ TO\ COMPb$

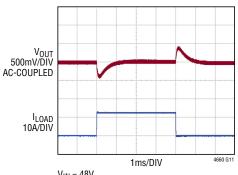

#### Radiated EMI Performance (CISPR22 Radiated **Emission Test with Class B 3m Limits)**

## PIN FUNCTIONS

**V<sub>OUT</sub>** (A1-3, B1-3, C1-3, D1-3, E3, F3, G3, H3): Output Voltage. Bypass to ground with capacitors appropriate for the application. See Decoupling Requirements.

$V_{IN}$  (A5, B5, C5, D5, E5): Main Input Supply. Bypass this pin to GND with at least  $2 \times 4.7 \mu F$  X7R- or X7S-type capacitors with appropriate voltage rating.

**C+** (A6, B6, C6, D6, E6, F6, G5-6, H5-6, J6, K6, L6, M6): Switch Node Connection to One Terminal of Flying Capacitor. Voltage at this pin swings between  $V_{IN}/2$  and  $V_{IN}$ .

**C**<sup>-</sup> (A8-11, B8-11, C8-11, D8, E8, F8, G8, H8, J8, K8, L8, M8): Switch Node Connection to Internal Power Inductor and One Terminal of Flying Capacitor. Voltage at this pin swings between ground and  $V_{IN}/2$ .

GND (A12, B12, C12, D9-D12, E9-12, F9-12, G9, H9, J1-2, K1-2, L1-2, M1): Power Ground. Connect all module GND pins to the application's power ground plane.

MID (E1-2, F1-2, G1-2, G10-12, H1, H10-12, J10-12): Half Supply from  $V_{IN}$ . Do not use this to source current. Connect MLCC bypass capacitors from this node to GND. A minimum of  $8\times 10\mu F$  X7R or X7S MLCC capacitors is recommended. Higher efficiency can be achieved with  $12\times 10\mu F$  X7R or X7S MLCC capacitors. All MID pins are internally connected within the module, but in order for the LTM4660 to achieve the best possible efficiency, it is necessary to connect all MID pins together with large copper plane(s) external to the module. See the Applications Information section.

$V_{INSNS}$  (F5):  $V_{IN}$  Kelvin Sensing Input. Used to accurately sense input voltage. Connect to  $V_{IN}$ , under the module.

MID<sub>SNS</sub> (H2): MID Kelvin Sensing Input. Used to accurately sense MID voltage. Connect to MID under the module.

**FAULT (J3):** Open Drain Output pin. When the signal goes low, it indicates one of the following conditions:

a. In the capacitor balancing phase, capacitors  $C_{FLY}$  or  $C_{MID}$  (see Typical Applications) are not charged to  $V_{IN}/2$ . A low FAULT indicates an abnormal condition that is preventing  $C_{FLY}$  or  $C_{MID}$  from being be charged up to  $V_{IN}/2$ .

- b. During normal operation, the voltage deviates from  $V_{\text{IN}}/2$  by a window amount set by the voltage on the HYS PRGM pin.

- c. The die temperature exceeds its internally set limit or the PTC resistor connected as the lower leg of a resistor divider (if used) trips the TEMP pin threshold.

During any of the aforementioned conditions, the TRACK/SS pin will also be pulled low.

**INTV<sub>CC</sub> (J4):** Internal Regulator Output. Powers control circuits and gate drivers internal to the module. Leave this pin floating.

**TEMP+ (J9):** Temperature Sensor, Positive Input. Emitter of a 2N3906-genre PNP bipolar junction transistor (BJT). Optionally interface to temperature monitoring circuitry such as LTC®2997, LTC2990, LTC2974 or LTC2975. Otherwise leave electrically open.

**TEMP**<sup>-</sup> **(K9):** Temperature Sensor, Negative Input. Collector-base of a 2N3906-genre PNP bipolar junction transistor (BJT). Optionally interface to temperature monitoring circuitry such as LTC2997, LTC2990, LTC2974 or LTC2975. Otherwise leave electrically open.

**TIMER (K3):** Charge Balancing Timer Input. A capacitor connected from this pin to SGND sets the amount of time allocated to charge  $C_{FLY}$  and  $C_{MID}$  to  $V_{IN}/2$  during the capacitor balancing phase. It also sets the auto-retry timeout, should the capacitors fail to reach this voltage within the set time. Capacitors  $C_{FIY}$  and  $C_{MID}$  begin and end charging when the TIMER voltage is between 0.5V and 1.2V, respectively. If the capacitor is balanced before the TIMER voltage reaches 1.2V, this voltage is reset to ground and normal operation begins. However, if the balance is not reached when the voltage reaches 1.2V, then the charging of the capacitors stops and the auto-retry timeout period begins. The TIMER capacitor will now slew at half the rate until it reaches 4V and then resets to zero and begins to slew at 1x rate. Once it reaches 0.5V, the  $C_{FLY}$  and  $C_{MID}$  begin to charge again and the process repeats.

**TEST (K4):** Test Pin. Used in ATE test, only. Leave open circuit.

## PIN FUNCTIONS

**EXTV**<sub>CC</sub> (**K10**): External Power Input to an Internal LDO Connected to INTV<sub>CC</sub>. This LDO supplies INTV<sub>CC</sub> power, bypassing the internal LDO powered from  $V_{IN}$  whenever EXTV<sub>CC</sub> is higher than 8V. Do not float or exceed 20V on this pin. Connect EXTV<sub>CC</sub> to GND, if the features is unused.

To reduce internal module temperature rise, it is strongly recommended to bias  $\mathsf{EXTV}_{CC}$  with  $\mathsf{8V}_{DC}$  or higher. For applications where  $\mathsf{V}_{OUT} \geq \mathsf{8V}$ , there is an easy way: connect  $\mathsf{V}_{OUT}$  to  $\mathsf{EXTV}_{CC}$ . For applications where  $\mathsf{V}_{OUT} < \mathsf{8V}$ , it is strongly recommended to drive  $\mathsf{EXTV}_{CC}$  to  $\mathsf{8V}$  (or higher) with an external bias supply. When driving  $\mathsf{EXTV}_{CC}$  externally, take precautions to ensure  $\mathsf{EXTV}_{CC} \leq \mathsf{V}_{IN}$  at all times.

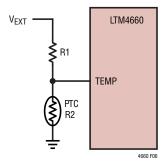

**TEMP (K11):** Temperature Sensing Input. Using a PTC resistor as the lower leg of a resistor divider, connect the TEMP pin to the common point of the divider. The PTC resistor is used to monitor a hot spot on the PCB. Once it reaches the TEMP threshold of 1.22V, the LTM4660 stops switching for 100ms before retrying. Ground this pin if not used.

$V_{FB}$  (K12): Error Amplifier Feedback Input. Connect resistor  $R_{VFB}$  from this pin to SGND in order to configure the  $V_{OUT}$  output voltage setting.  $R_{VFB}$  is given by Equation 1.

$$R_{VFB} (k\Omega) = \frac{60.4}{\left(\frac{V_{OUT}}{V_{VFB}} - 1\right)}$$

(1)

When EXT\_REF is connected to INTV<sub>CC</sub>, the module regulates the  $V_{FB}$  pin at 0.8V, nominal. If EXT\_REF is used or TRACK/SS is externally driven to influence the  $V_{FB}$  target servo voltage, the value of  $R_{VFB}$  must be computed accordingly. (See the Applications Information section.)

**RUN (L3):** Run Control Input. A voltage above 1.3V turns the LTM4660 ON. A voltage below 1.1V causes the module to shutdown. There is a  $1\mu A$  pull-up current on this pin when its voltage is below 1.3V.

**SGND (L4, L12, M12):** Signal Ground. All small-signal components and compensation components (if used) should connect to this signal SGND, which connects to GND internal to the module. It is not necessary to connect SGND to GND externally.

**TRACK/SS (L9):** Output Voltage Tracking and Soft-Start Input. The LTM4660 regulates the  $V_{FB}$  voltage to the lowest of three voltages: 0.8V, the voltage on the EXT\_REF pin or the voltage on the TRACK/SS pin. An internal 10µA pull-up current source is connected to this pin. A capacitor to SGND at this pin sets the ramp time to the final regulated output voltage. Alternatively, a resistor divider from another voltage supply connected to this pin allows the LTM4660 output voltage to track the other supply during start-up.

HYS\_PRGM (L11): There is a  $10\mu A$  current flowing out of this pin. A voltage created by connecting a resistor from this pin to SGND sets an equal amount of window threshold around  $V_{IN}/2$  to a window comparator. When the voltage at MID<sub>SNS</sub> is not within this window threshold, FAULT will be pulled low and switching will stop.  $C_{FLY}$  and  $C_{MID}$  will be rebalanced to half of  $V_{IN}$  before resuming normal operation.

**PGOOD (M2):** Power Good Pin. This is an open drain output. PGOOD is pulled to ground when voltage at V<sub>FB</sub> pin falls below 7.5% or rises above 8.5% of its set point. It will also be pulled low when FAULT is tripped.

**MODE/PLLIN (M3):** Mode Selection or External Synchronization Input to Phase Detector. When external synchronization is not used, this pin selects the operating modes and can be tied to SGND, to  $INTV_{CC}$  or left open circuit. If the pin is connected to SGND, it enables forced continuous mode while a connection to  $INTV_{CC}$  enables pulse-skipping mode. Floating the pin enables Burst Mode operation. For external sync, apply a clock signal to this pin. The integrated PLL along with its internal compensation network will synchronize the internal oscillator to external clock. Forced continuous mode will be enabled when an external clock is applied.

**CLKOUT (M4):** Clock Output Pin. This pin outputs a clock 180° out of phase with the main operating clock of the LTM4660.

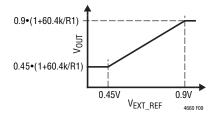

**EXT\_REF (M9):** External Reference Input. A voltage applied to this pin forces the  $V_{FB}$  to regulate to this voltage. Internal clamps set at 0.45V and 0.9V limit the lower and upper bounds of  $V_{FB}$  regulation that EXT\_REF can

## PIN FUNCTIONS

command. Connecting this pin to  $INTV_{CC}$  will cause the internal reference to be used for output voltage regulation.

**COMPb** (L10): Default Loop Compensation Network. Connect COMPa to COMPb for default loop compensation—or otherwise, leave open circuit.

**COMPa (M10):** Current Control Threshold and Error Amplifier Compensation Point. The current comparator

threshold increases with its COMPa control voltage. Connect COMPa to COMPb for default loop compensation—or alternatively, connect a series R-C network from COMPa to SGND, to apply application-specific loop compensation.

**FREQ (M11):** Frequency Set Pin. There is a  $10\mu A$  current flowing out of this pin. A resistor to ground sets a voltage which in turn programs the switching frequency of the module.

## **BLOCK DIAGRAM**

## **DECOUPLING REQUIREMENTS** $T_A = 25^{\circ}C$ . Refer to Block Diagram.

| SYMBOL           | PARAMETER                                                                                  | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|------------------|--------------------------------------------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

| C <sub>FLY</sub> | External Flying Capacitor Requirement, $30V \le V_{IN} \le 60V$ , $V_{OUT} = 12V$          | P <sub>OUT</sub> = 300W (Note 3) | 80  | 100 | 120 | μF    |

| C <sub>MID</sub> | External Midpoint Capacitor Requirement, $30V \le V_{IN} \le 60V$ , $V_{OUT} = 12V$        | P <sub>OUT</sub> = 300W (Note 3) | 80  | 100 | 120 | μF    |

| C <sub>OUT</sub> | External Output Capacitor Requirement, 30V ≤ V <sub>IN</sub> ≤ 60V, V <sub>OUT</sub> = 12V | P <sub>OUT</sub> = 300W          |     | 100 |     | μF    |

## **OPERATION**

#### **Module Description**

LTM4660 is a high efficient Intermediate Bus Converter (IBC) utilizing a hybrid switched capacitor topology. Four power switches along with capacitor bank  $C_{\text{FLY}}$  and  $C_{\text{MID}}$  form a switched capacitor stage, dividing the input voltage by two at MID. Voltage at MID is further stepped down through a power inductor and output capacitor, similar to a step down switching converter. LTM4660 employs peak current mode control of the inductor current for pulse width modulation of the switches and to maintain accurate output regulation. Soft switching of the power switches results in excellent efficiency and EMI performance.

Current mode control enables fast cycle-by-cycle current limiting of the inductor current and hence protects the internal components of LTM4660 during short-circuit conditions. With current mode control, LTM4660 exhibits good transient performance and stability margins for wide range of output capacitors. An internal compensation network included inside LTM4660 is sufficient for most typical applications. The  $V_{FB}$  pin is used to program the output voltage with a single resistor to ground.

Switching frequency can be programmed by a single resistor connected between FREQ pin and SGND. Typical switching frequency for IBC applications with LTM4660 is 300kHz to 500kHz. A phase-locked loop inside the module enables synchronizing the switching frequency to an external clock.

Pulling the RUN pin below 1.1V forces the regulator into a shutdown state by turning off all switching and internal circuits. The TRACK/SS pin is used for programming the output voltage ramp and voltage tracking during start-up. Internal bandgap reference of 0.8V can be overridden

by applying a suitable voltage at EXT\_REF pin. See the Applications Information section.

A general purpose temperature diode is included to monitor internal temperature of the module. In addition, TEMP pin of the module is used to program the OTP trip point. Internal overvoltage and undervoltage comparators pull the open-drain PGOOD output low if the output feedback voltage exits the regulation window.

Capacitor banks C<sub>FIY</sub> and C<sub>MID</sub> connected external to the µModule, are also part of the energy transfer elements. LTM4660 utilizes these capacitor-banks to efficiently deliver energy from input to output. These capacitors are initially precharged in the Capacitor Balancing phase using proprietary control techniques. This balancing eliminates large transient currents seen in similar switched capacitor based topologies. Voltages of capacitor banks are continuously monitored and balanced by LTM4660. Dedicated pins TIMER and HYS PRGM are provided to set the balancing time interval and voltage window and can be adjusted for each application of LTM4660. Following balancing phase, regular switching action begins. During each switching cycle, capacitor CFLY is connected either in series with or in parallel to  $C_{MID}$ . See Operation and Applications Information section.

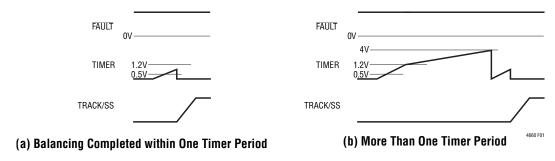

## **Capacitor Balancing Phase**

During initial power up, voltage across the flying capacitor ( $C_{FLY}$ ) and  $C_{MID}$  are measured. If either of these voltages are not at  $V_{IN}/2$ , the TIMER's capacitor will be allowed to charge up. When the TIMER capacitor's voltage reaches 0.5V, internal current sources to bring  $C_{FLY}$  voltage to  $V_{IN}/2$  are turned ON. After the  $C_{FLY}$  voltage has reached  $V_{IN}/2$ ,  $C_{MID}$  will then be charged to  $V_{IN}/2$ . The TRACK/SS pin is pulled low during this duration. The FAULT pin will

## **OPERATION**

not be pulled low during this initial power up. If the voltages across  $C_{FLY}$  and  $C_{MID}$  reach  $V_{IN}/2$  before the TIMER capacitor's voltage reaches 1.2V, the TRACK/SS will be released and allowed to charge up. The TIMER pin will reset to ground and remain there. Normal operation will begin (see Figure 1a).

If, however, the  $C_{FLY}$  or  $C_{MID}$  voltage is not at  $V_{IN}/2$  when  $V_{TIMER}$  reaches 1.2V, the internal current sources will be turned OFF and the TIMER capacitor will be charged at half the initial rate until it reaches 4V. Timer will then be reset to zero, and the LTM4660 will repeat the above process again until  $C_{FLY}$  and  $C_{MID}$  are at  $V_{IN}/2$ . (See Figure 1b).

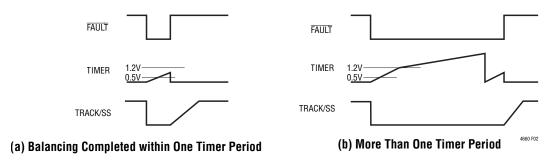

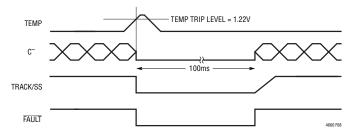

During normal operation, only  $C_{MID}$  is monitored for deviation away from  $V_{IN}/2$  by a window amount set by a resistor connected from HYS\_PRGM to ground. The voltage across this resistor sets the same amount of window threshold above and below  $V_{IN}/2$ . If  $V_{CMID}$  leaves this voltage window, all switching will stop, and the TRACK/SS pin will be pulled low. Corresponding internal current sources will be turned on to bring  $C_{FLY}$  and  $C_{MID}$  voltages back to  $V_{IN}/2$ . FAULT will be pulled low and released once the balancing is complete. During this balancing period,

PGOOD will also be pulled low. The TRACK/SS pin is also allowed to charge up upon the completion of balancing (see Figure 2). Connecting HYS\_PRGM to INTV<sub>CC</sub> sets the window threshold to  $\pm 0.8V$  around  $V_{IN}/2$ .

### **Main Control Loop**

Once the capacitor balancing phase is complete, normal operation begins. Power switches are turned ON/ OFF based on peak current in the power inductor. Peak inductor current is controlled by voltage on COMPa pin, which is the output of a transconductance error amplifier. The  $V_{FB}$  pin receives the voltage feedback signal from  $V_{OUT}$ , which is compared to the internal reference voltage by the error amplifier. When load current increases, it causes a slight decrease in  $V_{FB}$  relative to the 0.8V reference voltage, which in turn causes the COMPa voltage to increase until average inductor current matches the new load current.

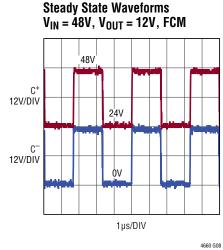

During each switching cycle, capacitor  $C_{FLY}$  is connected in series with or parallel to  $C_{MID}$ . Voltage at  $C^+$  alternates between  $V_{IN}$  and  $V_{IN}/2$  whereas voltage at  $C^-$  alternates between  $V_{IN}/2$  and ground. The voltage at MID and across  $C_{FLY}$  will each be approximately at  $V_{IN}/2$ .

Figure 1. Charge Balancing During Power-Up

Figure 2. Charge Balancing During Normal Operation

The Typical Applications on the first page is a basic LTM4660 application circuit.

#### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for power switch drivers and most internal circuitry is derived from the INTV $_{CC}$  pin. When the EXTV $_{CC}$  pin is grounded or tied to a voltage less than 7V, an internal 5.8V linear regulator supplies INTV $_{CC}$  power from V $_{IN}$ . If EXTV $_{CC}$  is taken above 8V, this linear regulator is turned OFF and another 5.8V linear regulator turns ON to provide the INTV $_{CC}$  power from EXTV $_{CC}$ . Using the EXTV $_{CC}$  pin allows the INTV $_{CC}$  power to be derived from a high efficiency external source, resulting in an overall increase in LTM4660 efficiency. For LTM4660 applications where V $_{OUT}$  is greater than 8V, EXTV $_{CC}$  can be directly tied to V $_{OUT}$ .

#### Shutdown and Start-Up

When RUN pin is below 1.1V, INTV<sub>CC</sub> linear regulator along with all the internal circuitry including the main control loop enters shutdown mode. Releasing the RUN pin will allow a internal  $1\mu A$  current source to pull this pin up, thus enabling LTM4660. RUN pin can also be driven directly by logic if this voltage does not exceed the absolute maximum rating of 6V.

The slew rate of the output voltage  $V_{OLIT}$  can be controlled by the voltage on the TRACK/SS pin. When voltage on TRACK/ SS is less than internal reference voltage of 0.8V (or EXT\_ REF if this feature is utilized), the LTM4660 regulates the V<sub>FR</sub> voltage to the TRACK/SS voltage instead of to the reference voltage. This allows TRACK/SS pin to be used to program the soft-start period by connecting an external capacitor from the TRACK/SS pin to SGND. After capacitor balancing phase of LTM4660 is completed, an internal 10µA pull-up current charges the soft-start capacitor, creating a voltage ramp. As the voltage on this pin rises linearly from OV to the reference voltage (and beyond), output voltage  $V_{OLIT}$ rises smoothly from zero to the final set value. Note that soft-start is achieved not by limiting the maximum output current of LTM4660 but by controlling the output ramp voltage according to the ramp rate at the TRACK/SS pin. The total soft-start time can be calculated with Equation 2.

$$t_{SOFT-START} = 0.8V \text{ or } V_{EXT\_REF} \cdot \frac{Css}{10\mu A}$$

(2)

A 0.1µF capacitor connected between TRACK/SS pin and SGND would be sufficient for most typical IBC applications with LTM4660.

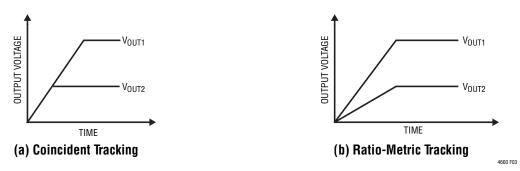

#### **Output Voltage Tracking**

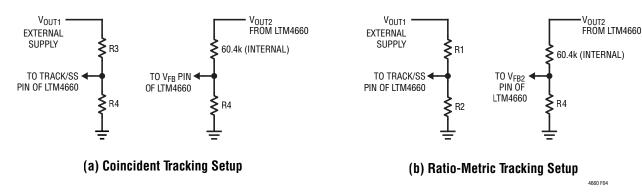

Alternatively, TRACK/SS pin allows start-up of  $V_{OUT}$  to track that of another supply. Typically, this requires connecting to the TRACK/SS pin an external resistor divider from the other supply to ground. Tracking can be configured to be either coincident or ratiometric as shown in Figure 3. In the following discussions,  $V_{OUT1}$  refers to another supply's output while  $V_{OUT2}$  refers to the LTM4660 output that tracks  $V_{OUT1}$ . To implement the coincident tracking in Figure 3a, connect an additional resistive divider to  $V_{OUT1}$  and connect its midpoint to the TRACK/SS pin of the LTM4660. The ratio of this divider should be the same as that of the slave channel's feedback divider shown in Figure 4a. In this tracking mode,  $V_{OUT1}$  must be higher than  $V_{OUT2}$ . This ensures the final voltage on TRACK/SS pin is greater than 0.8V.

To implement ratiometric tracking shown in Figure 3b, connect a resistor divider R1 and R2 from external supply to TRACK/SS pin of LTM4660. Select R1 and R2 such that when external supply reaches steady state, final voltage on TRACK/SS is less than 0.8V. Use this final voltage to select FB resistor R4 (see Figure 4b). Output voltage  $V_{OUT2}$  of LTM4660 which ratiometrically tracks external supply voltage  $V_{OUT1}$  is given by Equation 3.

$$V_{OUT2} = \frac{V_{OUT1} \left( 1 + \frac{60.4k}{R4} \right)}{1 + \frac{R1}{R2}}$$

(3)

In order to track down another supply after the soft-start has successfully reached 82.5% of 0.8V or  $V_{EXT\_REF}$ , it is recommended to set the LTM4660 into forced continuous mode operation by setting the MODE/PLLIN = 0V. By selecting different resistors, the LTM4660 can achieve different modes of tracking including the two in Figure 3. The ratio-metric mode has lesser output accuracy on  $V_{OUT2}$  but is fully coupled to any variations in  $V_{OUT1}$ . In both modes, there is an error in output voltage setting caused by the pin current of TRACK/SS. To minimize this error, use smaller resistor values in the divider.

Figure 3. Two Different Methods of Output Voltage Tracking

Figure 4. Setup for Coincident and Ratio-Metric Tracking

#### Burst Mode Operation, Pulse-Skipping Mode, or Forced Continuous Mode

The LTM4660 can be enabled to enter high efficiency Burst Mode operation, constant-frequency pulse-skipping mode, or forced continuous mode. To select forced continuous operation, tie the MODE/PLLIN pin to SGND. To select pulse-skipping mode of operation, tie the MODE/ PLLIN pin to INTV<sub>CC</sub>. To select Burst Mode operation, float the MODE/PLLIN pin. When the controller is enabled for Burst Mode operation, if the average inductor current is higher than the load current, the error amplifier will decrease the voltage on the COMPa pin. When the COMPa voltage drops below 0.5V, the internal sleep signal goes high (enabling sleep mode) and switching is turned off. In sleep mode, the load current is supplied by the output capacitor. As the output voltage decreases, the voltage on COMPa pin begins to rise. When the output voltage drops enough, the sleep signal goes low, and the controller resumes normal operation by turning on the power switches on the next cycle of the internal oscillator. When a controller is enabled for Burst Mode operation, the controller operates in discontinuous operation. In forced continuous operation, the peak inductor current is determined by the voltage on the COMPa pin. Switching frequency is constant as set by R<sub>FRFQ</sub> resistor and inductor current remains continuous through the switching period. In this mode, the efficiency at light loads is lower than in Burst Mode operation. However, continuous mode has the advantages of faster response to load transients and less interference with audio circuitry. When the MODE/ PLLIN pin is connected to INTV<sub>CC</sub>, the LTM4660 operates in PWM pulse-skipping mode at light loads. At very light loads, switching is off for few numbers of cycles (i.e., skipping pulses) and the part operates in discontinuous mode. This mode, like forced continuous operation, exhibits low output ripple as well as low audio noise and reduced RF interference as compared to Burst Mode operation. At light loads, pulse-skipping mode provides higher efficiency than forced continuous mode, but not nearly as high as Burst Mode operation. Regardless of the

mode selected by MODE/PLLIN pin, LTM4660 will always operate in pulse-skipping mode during start-up.

#### Frequency Selection and Phase-Locked Loop

The switching frequency of the LTM4660 can be selected using the FREQ pin. If the MODE/PLLIN pin is not being driven by an external clock source, the FREQ pin can be used to program the controller's operating frequency from 200kHz to 1MHz. There is a 10 $\mu$ A current flowing out of the FREQ pin, so the user can program the controller's switching frequency with a single resistor to SGND. Figure 5 shows variation of switching frequency versus resistor connected from FREQ pin to SGND. For typical datacenter IBC applications of LTM4660 with  $V_{IN}=48V$  or 54V bus voltage and with  $V_{OUT}=12V$ , choose FREQ resistor to be 40k to 60k for maximum efficiency.

Figure 5. Variation of Switching Frequency vs Resistor Connected from FREQ Pin to SGND

A phase-locked loop (PLL) is integrated on the LTM4660 to synchronize the internal oscillator to an external clock source that is connected to the MODE/PLLIN pin. Rising edge of C<sup>-</sup> pin synchronizes to the rising edge of the external clock source. The controller operates in forced continuous mode when it is synchronized. The phase-locked loop is capable of locking any frequency within the range of 200kHz to 1MHz. The frequency setting resistor should always be present to set the controller's initial switching frequency before locking to the external clock.

#### **Temperature Monitoring**

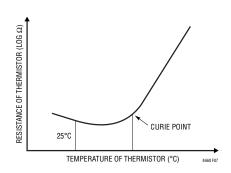

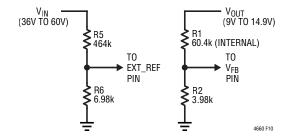

The LTM4660 can provide hotspot monitoring via the TEMP pin. By using a PTC thermistor as the lower leg of a resistor divider and connecting the common point of this divider to the TEMP pin, the voltage increases drastically when the temperature reaches beyond the Curie point of the PTC thermistor as shown in Figure 6. The characteristic of the PTC thermistor is shown in Figure 7. When the TEMP pin reaches 1.22V, all switching stops for 100ms.

The voltage on the TRACK/SS pin and  $\overline{\text{FAULT}}$  is pulled low and is released after 100ms (Figure 8) if the voltage on the TEMP pin goes below 1.1V during this 100ms timeout. If the TEMP pin voltage remains above 1.1V, the timeout period will be extended until the voltage drops below 1.1V. The temperature that is used to trigger the hotspot protection will determine the thermistor selection. This temperature will be the Curie point of the thermistor, which is often defined as having two times its resistance at 25°C. With the Curie point resistance of the thermistor known, R2<sub>CURIE</sub>, the upper resistance, R1, can be selected by Equation 4.

$$R1 = \frac{R2_{\text{CURIE}} (V_{\text{EXT}} - 1.22)}{1.22}$$

(4)

A diode-connected PNP transistor is connected internally between pins TEMP<sup>+</sup> and TEMP<sup>-</sup>. The transistor is centrally located inside LTM4660, in close proximity to the hotspot. Voltage derived from the TEMP<sup>+</sup> and TEMP<sup>-</sup> pins provides a close estimate of the internal temperature of LTM4660.

Figure 6. Temperature Monitoring Setup

Figure 7. Characteristic of a Thermistor

Figure 8. Temperature Trip Characteristic

#### **Power Good**

When  $V_{FB}$  pin voltage falls below 7.5% or rises above 8.5% of the internal 0.8V reference or the reference set by EXT\_REF, the PGOOD pin is pulled low. The PGOOD pin is also pulled low when the RUN pin is below 1.1V or when the LTM4660 is in the soft-start or tracking phase. The PGOOD pin will flag power good immediately when the  $V_{FB}$  pin is within the reference window. However, there is an internal 50µs power bad mask when  $V_{FB}$  goes out this window. The PGOOD pin can be pulled up by an external resistor to sources of up to 20V.

#### **FAULT**

During initial power up of the LTM4660 or when enabling the part via the RUN pin, the  $\overline{FAULT}$  pin will not be pulled low even when  $C_{FLY}$  and/or  $C_{MID}$  need to be rebalanced to  $V_{IN}/2$ . But during normal operation, when rebalancing is needed, the  $\overline{FAULT}$  will be pulled low. Another condition that causes the  $\overline{FAULT}$  to go low is thermal shutdown, either caused by the internal temperature reaching 150°C or the voltage at TEMP pin reaching 1.22V. The  $\overline{FAULT}$  pin is allowed to be pulled up by an external resistor to sources of up to 20V.

#### **Frequency Compensation**

The LTM4660 µModule employs peak current mode control for pulse width modulation of the power switches. This method of control simplifies the compensation design by eliminating the dynamics of the power inductor contributing to the closed loop response. A Type-II network is sufficient to compensate the LTM4660 feedback loop. Such a network comprises of a resistor in series with capacitor connected at COMPa pin—the output of a transconductance error amplifier inside LTM4660, to SGND. A high frequency roll-off capacitor of 22pF, as part of the Type-II network is already connected at the COMPa pin internal to LTM4660.

Choose the components of the Type-II network dependent on the desired output response for line and load variations as well as loop stability parameters phase margin and gain margin of the feedback loop. In general, selecting a low capacitance and a high resistance for the Type-II network at COMPa pin leads to fast transient response but may adversely affect the loop stability parameters.

A resistor capacitor network of 10k in series with 10nF is connected from COMPb pin to SGND internal to LTM4660. For most LTM4660 applications, it is sufficient to tie COMPa and COMPb pins together to ensure closed loop stability across line and load variations. Refer to LTM4660 model in LTspice® to fine tune and optimize the Type-II network for each application circuit with LTM4660.

#### **Input Capacitor Selection**

The LTM4660 module should be connected to a low AC-impedance DC source. For the regulator input, two  $10\mu F$  input ceramic capacitors are required for RMS ripple current. A  $33\mu F$  or  $47\mu F$  surface mount aluminum electrolytic bulk capacitor can be used for more input bulk capacitance. This bulk input capacitance is only needed if the input source impedance is compromised by long inductive leads. If low impedance power planes are used, then this bulk capacitor is not needed. For IBC applications with 48V or 54V bus, choose input capacitors rated to at least 100V.

Without considering the inductor current ripple, the RMS current of the input capacitor can be estimated by Equation 5.

$$I_{\text{CIN(RMS)}} = \frac{I_{\text{OUT(MAX)}}}{2 \cdot \eta\%} \cdot \sqrt{(D \cdot D')}$$

(5)

where D is 2 •  $V_{OUT}/V_{IN}$  and D' = 1 - D

In the above equation,  $\eta\%$  is the estimated efficiency of the power module. The bulk capacitor can be a switcher-rated electrolytic aluminum capacitor or Polymer capacitor.

#### **Output Capacitor Selection**

The LTM4660 is designed to achieve good transient response and low output voltage ripple. Choose  $C_{OUT}$  with low ESR to meet the output ripple and transient performance requirements. Place at least two  $10\mu F$  output ceramic capacitors close to  $V_{OUT}$  and GND pins. This lowers the output ripple by lowering the total ESR of  $C_{OUT}$ . Aluminum electrolytic capacitors of  $100\mu F$  or  $150\mu F$  can be placed further away as bulk output capacitors. Choose enough bulk capacitance to meet the transient specification demanded by downstream loads. When choosing  $C_{OUT}$ , be aware of the impact of its ESR on loop stability. Refer to LTM4660 model in LTspice to optimize and fine tune the combination of  $C_{OUT}$  for each LTM4660 application.

#### **CFIY and CMID Selection**

For the LTM4660  $\mu$ Module, capacitor banks  $C_{FLY}$  and  $C_{MID}$  connected external to the  $\mu$ Module, are part of the energy transfer elements. Therefore, ceramic capacitors are attractive since they have the lowest ESR. However, care should be taken when choosing this type of capacitors. During operation the DC voltage across  $C_{FLY}$  and  $C_{MID}$  is approximately half the  $V_{IN}$  supply, therefore the voltage rating of the capacitors should be greater than that. As a general rule, select the voltage rating of the capacitor to be twice the operating voltage of the capacitor. For the same voltage rating and capacitance, a larger case size will have a lower failure rate.

In addition, the operating temperature of the capacitors needs to be considered. For operating temperature above 85°C, capacitors with the X7R dielectric need to be used while X5R dielectric is adequate for operation below 85°C. For long term reliability of the capacitor, keep

the temperature rise of the capacitor to be below 20°C, preferably 10°C. The temperature rise of the capacitor is dependent on the amount of RMS current through the capacitor and the operating frequency.

Ceramic capacitors also have a large voltage coefficient, losing close to half their capacitance when the DC bias across a given capacitor is half its rated voltage. The DC bias effect on a capacitor is greater when the case size is smaller. Factor in these effects when deciding on the capacitance.

The ripple voltage on  $C_{FLY}$  and  $C_{MID}$  is given by Equation 6.

$$V_{RIPPLE} = \frac{I_{OUT}}{C_{BANK} \cdot f_{SW}} \frac{2V_{OUT}}{V_{IN}}$$

(6)

where  $C_{BANK}$  is either  $C_{FLY}$  or  $C_{MID}$ ,  $I_{OUT}$  is output current and  $f_{SW}$  is the switching frequency.

Ripple voltage on  $C_{FLY}$  and  $C_{MID}$  contributes significantly to the power dissipated in LTM4660 (see Efficiency figures in Typical Performance Characteristics section). As a good starting point, select enough capacitance such that the ripple on each capacitor is less than 1% of the DC bias voltage of the capacitor. For example, if the DC bias voltage of the capacitor is 24V, keep the ripple to be less than 240mV. To achieve lowest loss in LTM4660, select the capacitance of  $C_{MID}$  to be same as that of  $C_{FLY}$ .

LTM4660 is designed to deliver 300W of output power at  $12V_{OUT}$ . For maximum efficiency at 300W, use eight to twelve  $10\mu F$  ceramic capacitors each for  $C_{MID}$  and  $C_{FLY}$ . Considering the voltage derating of ceramic capacitors, for bus voltages in range of  $48V_{IN}$  to  $54V_{IN}$ , choose ceramic capacitors rated to at least 50V.

### **Timer and Hysteresis**

The LTM4660  $\mu$ Module uses a switched capacitor hybrid topology where the switched capacitor stage consists of C<sub>FLY</sub> and C<sub>MID</sub> capacitor banks connected alternately in series or in parallel through the power switches inside LTM4660. During start-up, C<sub>FLY</sub> and C<sub>MID</sub> capacitors are completely discharged. Starting switching with the capacitors discharged may lead to undesirably high currents through the power switches. To circumvent this phenomenon, LTM4660 uses a patented technology to balance the charge across the C<sub>FLY</sub> and C<sub>MID</sub> to half of V<sub>IN</sub> during start-up.

Capacitor connected at TIMER pin to SGND defines the time-period during which LTM4660 enters capacitor balancing phase. An internal current source at the pin charges the TIMER capacitor generating a voltage ramp. Capacitor balancing is initiated when the voltage at this pin is between 0.5V and 1.2V. Choose this capacitor based on the maximum input voltage and the capacitance of capacitor banks  $C_{FLY}$  and  $C_{MID}$ . Higher input voltage and higher capacitance indicates more time necessary for LTM4660 to complete capacitor balancing, hence requiring a larger TIMER capacitor. Choosing a smaller TIMER capacitor leads to LTM4660 using multiple TIMER cycles to complete capacitor charge balancing leading to longer start-up times.

A TIMER capacitor of  $1\mu F$  is sufficient for  $V_{IN}$  of up to 60V and  $C_{MID} = C_{FIY} = 10\mu F \cdot 12$ .

### **HYS\_PRGM Voltage**

The voltage on the HYS\_PRGM pin sets a window centered on  $V_{IN}/2$  for fault protection purposes. During operation, if the voltage at MID\_SNS deviates beyond this window, a fault is indicated, and capacitor balancing begins. Therefore, setting the correct window is important as it adds another layer to of protection to LTM4660 application circuit.

During normal operation, voltage at MID may settle to a voltage less than  $V_{IN}/2$  depending on the impedance looking into MID and output current. In general, higher the  $I_{OUT}$ , higher would be the deviation of MID from  $V_{IN}/2$ . Similarly, lower the  $C_{MID}$  and switching frequency, higher the impedance looking into MID. In addition to the DC offset of MID relative to  $V_{IN}/2$ , the AC ripple on  $C_{MID}$  is also to be considered (Refer to Equation 6 in  $C_{FLY}$  and  $C_{MID}$  Selection section) when choosing the HYS PRGM window.

For most LTM4660 applications, a hysteresis window of 1V is sufficient to ensure proper operation. To set the window to 1V, connect a 100k resistor from HYS\_PRGM to SGND.

### **Output Voltage Setting**

The LTM4660 uses its internal reference of 0.8V when EXT\_REF is tied to  $INTV_{CC}$ . The output voltage is

given by Equation 7. Always set  $V_{OUT}$  to be less than half of the minimum expected input voltage.

$$V_{OUT} = 0.8V \cdot \left(1 + \frac{60.4k}{R1}\right)$$

(7)

Applying a voltage on EXT\_REF pin between 0.45V and 0.9V allows LTM4660's output to track the EXT\_REF voltage, indicated by the characteristic in Figure 9.

Figure 9. Output Voltage Set by EXT\_REF Pin

Due to its unique architecture, the optimal efficiency for the LTM4660 is when  $V_{OUT} = V_{IN}/4$ . Efficiency for stepdown ratios higher or lower than 4:1 may be lower. For applications that demand optimal efficiency within a range of  $V_{IN}$ , EXT\_REF could be used to track this  $V_{IN}$  variation while maintaining a 4:1 step down ratio at the output. In this type of setup, the output voltage will also change with the input. Figure 10 shows a 48V to 12V setup that accounts for  $V_{IN}$  variation between 36V to 60V.

Figure 10. Output Voltage to Track V<sub>IN</sub> in 4:1 Ratio

#### **Minimum On-Time Considerations**

Minimum on-time  $t_{ON(MIN)}$  is the smallest time duration that LTM4660 is able to turn on its power switches. Low duty cycle applications may approach minimum on-time limit and care should be taken to ensure Equation 8.

$$\frac{2V_{OUT}}{V_{IN}} \bullet \frac{1}{f_{SW}} > t_{ON(MIN)}$$

(8)

If duty cycle falls below what can be accommodated by the minimum on-time, the LTM4660 will begin to skip cycles. Output voltage will continue to be regulated but ripple voltage and current will increase.  $t_{ON(MIN)}$  for LTM4660 is 210ns for 4:1 step-down ratios and it linearly increases for higher step-down ratios. To avoid running into minimum on-time of LTM4660 switching, it is recommended that switching frequency be reduced to 200kHz to 400kHz for input output step down ratios greater than 6:1.

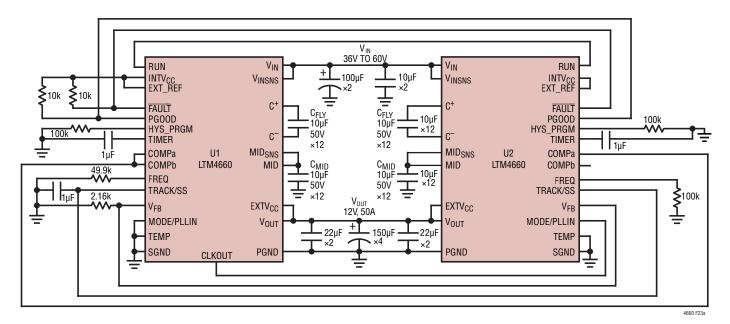

#### **Dual Phase Operation**

For higher output power applications, two LTM4660s can be easily paralleled to create a dual phase single output configuration. Figure 23 shows the key signal connections between the two LTM4660s.

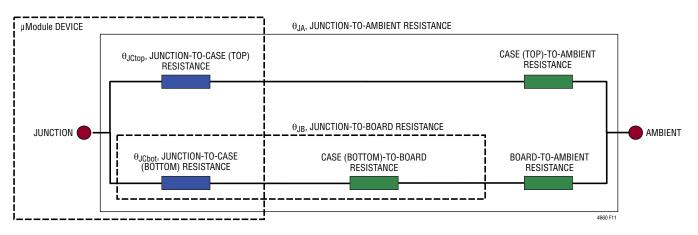

#### **Thermal Considerations**

The thermal resistances reported in the Pin Configuration section are consistent with those parameters defined by JESD 51-9 and are intended for use with finite element analysis (FEA) software modeling tools that leverage the outcome of thermal modeling, simulation, and correlation to hardware evaluation performed on a µModule package mounted to a hardware test board—also defined by JESD 51-9 ("Test Boards for Area Array Surface Mount Package Thermal Measurements"). The motivation for providing these thermal coefficients is found in JESD 51-12 ("Guidelines for Reporting and Using Electronic Package Thermal Information").

Many designers may opt to use laboratory equipment and a test vehicle such as the demo board to anticipate the  $\mu$ Module regulator's thermal performance in their application at various electrical and environmental operating conditions to compliment any FEA activities. Without FEA software, the thermal resistances reported in the Pin Configuration section are in-and-of themselves not relevant to providing guidance of thermal performance; instead, the derating curves provided in the data sheet can be used in a manner that yields insight and guidance pertaining to one's application-usage and can be adapted to correlate thermal performance to one's own application.

The Pin Configuration section typically gives four thermal coefficients explicitly defined in JESD 51-12; these coefficients are quoted or paraphrased below:

- 1.  $\theta_{JA}$ , the thermal resistance from junction to ambient, is the natural convection junction-to-ambient air thermal resistance measured in a one cubic foot sealed enclosure. This environment is sometimes referred to as "still air" although natural convection causes the air to move. This value is determined with the part mounted to a JESD 51-9 defined test board, which does not reflect an actual application or viable operating condition.

- 2.  $\theta_{JCbottom}$ , the thermal resistance from junction to the bottom of the product case, is the junction-to-board thermal resistance with all of the component power dissipation flowing through the bottom of the package. In the typical  $\mu$ Module, the bulk of the heat flows out the bottom of the package, but there is always heat flow out into the ambient environment. As a result, this thermal resistance value may be useful for comparing packages, but the test conditions don't generally match the user's application.

- 3.  $\theta_{JCtop}$ , the thermal resistance from junction to top of the product case, is determined with nearly all of the component power dissipation flowing through the top of the package. As the electrical connections of the typical µModule are on the bottom of the package, it is rare for an application to operate such that most of the heat flows from the junction to the top of the part. As in the case of  $\theta_{JCbottom}$ , this value may be useful for comparing packages, but the test conditions don't generally match the user's application.

- 4.  $\theta_{JB}$ , the thermal resistance from junction to the printed circuit board, is the junction-to-board thermal resistance where almost all of the heat flows through the bottom of the  $\mu$ Module and into the board and is really the sum of the  $\theta_{JCbottom}$  and the thermal resistance of the bottom of the part through the solder joints and through a portion of the board.

A graphical representation of the aforementioned thermal resistances is given in Figure 11; blue resistances are

contained within the  $\mu$ Module regulator, whereas green resistances are external to the  $\mu$ Module.

As a practical matter, it should be clear to the reader that no individual or sub-group of the four thermal resistance parameters defined by JESD 51-12 or provided in the Pin Configuration section replicates or conveys normal operating conditions of a  $\mu$ Module. For example, in normal board-mounted applications, never does 100% of the device's total power loss (heat) thermally conduct exclusively through the top or exclusively through bottom of the  $\mu$ Module—as the standard defines for  $\theta_{JCtop}$  and  $\theta_{JCbottom}$ , respectively. In practice, power loss is thermally dissipated in both directions away from the package granted, in the absence of a heat sink and airflow, a majority of the heat flow is into the board.

Within a SIP (system-in-package) module, be aware there are multiple power devices and components dissipating power, with a consequence that the thermal resistances relative to different junctions of components or die are not exactly linear with respect to total package power loss. To reconcile this complication without sacrificing modeling simplicity—but also, not ignoring practical realities—an approach has been taken using FEA software modeling along with laboratory testing in a controlled-environment chamber to reasonably define and correlate the thermal resistance values supplied in this data sheet: (1) Initially, FEA software is used to accurately build the mechanical geometry of the  $\mu$ Module and the specified PCB with all of the correct material coefficients along with accurate power loss source definitions; (2) this model simulates

a software-defined JEDEC environment consistent with JSED 51-9 to predict power loss heat flow.

The LTM4660 package has been designed such that inductor on top also doubles as a heat sink, removing heat from the power switches below. The bottom substrate material has very low thermal resistance to the printed circuit board. An external heat sink can be applied to the top of the device for excellent heat sinking with airflow.

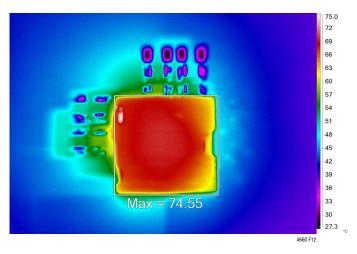

Figure 12 shows a thermal capture of LTM4660 with 48V input, 12V output at 25A without heat sink and 200LFM airflow condition.

#### **Recommended PCB footprint**

The high integration of LTM4660 makes the PCB board layout very simple and easy. However, to optimize its electrical and thermal performance, some layout considerations are still necessary.

- Use large PCB copper areas for high current paths, including V<sub>IN</sub>, GND, V<sub>OUT</sub>. It helps to minimize the PCB conduction loss and thermal stress.

- Place high frequency ceramic input and output capacitors next to the V<sub>IN</sub>, MID, GND and V<sub>OUT</sub> pins to minimize high frequency noise.

- Use short loops to route C<sub>FLY</sub> capacitors from C<sup>+</sup> to C<sup>-</sup>.

Reduce the parasitic trace inductance and resistance in this loop.

Figure 11. Graphical Representation of Thermal Coefficients, Including JESD51-12 Terms

Figure 12. Thermal Image 48V to 12V, 25A; 200LFM Airflow; No Heat Sink (Based on 6-Layer PCB with 2oz Copper on All Layers)

- Place a dedicated power ground layer underneath the unit.

- To minimize the via conduction loss and reduce module thermal stress, use multiple vias for interconnection between top layer and other power layers.

- Do not put via directly on the pad unless they are capped or plated over.

- Use a separated SGND ground copper area for components connected to signal pins. SGND is connected to GND internal to the module.

- For parallel modules, tie the V<sub>OUT</sub>, V<sub>FB</sub>, and COMP pins together. Use an internal layer to closely connect these pins together. The TRACK pin can be tied a common capacitor for regulator soft-start.

- Bring out test points on the signal pins for monitoring.

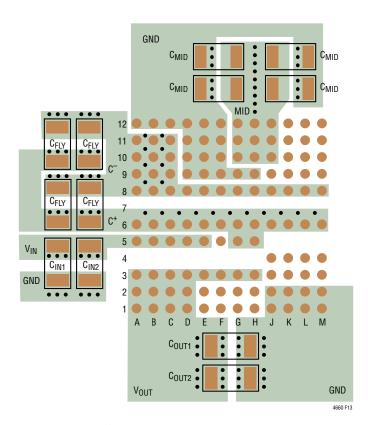

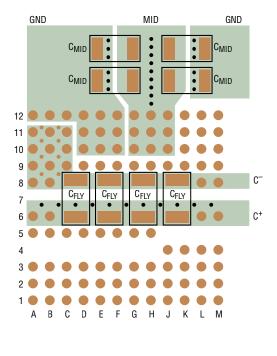

Figure 13 gives a good example of the recommended layout for input, output,  $C_{FLY}$  and  $C_{MID}$  capacitors on the top layer. Pinout of LTM4660 is designed such that  $C_{FLY}$  capacitors can be conveniently placed on the bottom layer right underneath the module, with minimal impact to total PCB area. (See Figure 14 for example of bottom layer layout).

Figure 13. Recommended Layout for Top Layer

Figure 14. Recommended Layout for Bottom Layer

4660 F14