One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# ADF7030-1 Software Reference Manual

### SCOPE

This manual provides a detailed description of how to control the ADF7030-1 transceiver from the host microcontroller. It is intended as a resource for the firmware (FW) engineer developing host microcontroller firmware to communicate with the ADF7030-1.

#### ABOUT THE ADF7030-1

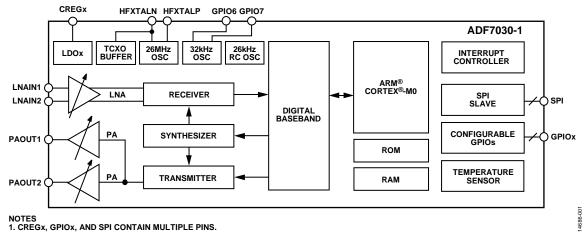

The ADF7030-1 is a low power, high performance, integrated radio transceiver supporting narrow-band and wideband operation in the <1 GHz industrial, scientific, and medical (ISM) bands. The ADF7030-1 features an on-chip Arm<sup>®</sup> Cortex<sup>®</sup>-M0 processor that performs radio control and packet management.

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. ADF7030-1 Functional Block Diagram

# TABLE OF CONTENTS

| Scope 1                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| About the ADF7030-11                                                                                                                                                                                                                                                                                    |

| Functional Block Diagram 1                                                                                                                                                                                                                                                                              |

| Revision History                                                                                                                                                                                                                                                                                        |

| Introduction                                                                                                                                                                                                                                                                                            |

| ADF7030-1 Operation                                                                                                                                                                                                                                                                                     |

| ADF7030-1 Memory Architecture                                                                                                                                                                                                                                                                           |

| Development Support                                                                                                                                                                                                                                                                                     |

| Design Package                                                                                                                                                                                                                                                                                          |

| Documentation7                                                                                                                                                                                                                                                                                          |

| Evaluation Kits                                                                                                                                                                                                                                                                                         |

| Evaluation Software7                                                                                                                                                                                                                                                                                    |

| Sample Driver7                                                                                                                                                                                                                                                                                          |

| ADF7030-1 State Machine                                                                                                                                                                                                                                                                                 |

| Introduction                                                                                                                                                                                                                                                                                            |

| ADF7030-1 States                                                                                                                                                                                                                                                                                        |

| State Transition Timing11                                                                                                                                                                                                                                                                               |

| ADF7030-1 SPI 12                                                                                                                                                                                                                                                                                        |

| Introduction12                                                                                                                                                                                                                                                                                          |

| SPI Pins12                                                                                                                                                                                                                                                                                              |

| Host Initialization of ADF7030-1 SPI12                                                                                                                                                                                                                                                                  |

| SPI Transactions                                                                                                                                                                                                                                                                                        |

| ADF7030-1 SPI Communication14                                                                                                                                                                                                                                                                           |

| Command Byte14                                                                                                                                                                                                                                                                                          |

| Radio Commands14                                                                                                                                                                                                                                                                                        |

| Radio Commands for External Hardware Triggered<br>Transitions                                                                                                                                                                                                                                           |

| Radio Command for a System Reset                                                                                                                                                                                                                                                                        |

| Accessing the ADF7030-1 Memory                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                         |

| -                                                                                                                                                                                                                                                                                                       |

| Introducton                                                                                                                                                                                                                                                                                             |

| Introducton                                                                                                                                                                                                                                                                                             |

| Introducton                                                                                                                                                                                                                                                                                             |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19                                                                                                                                                                        |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120                                                                                                                                             |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120Initial Configuration20                                                                                                                      |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120Initial Configuration20Modifying Configuration at Run Time20                                                                                 |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120Initial Configuration20Modifying Configuration at Run Time20Applying the ADF7030-1 Configuration File22                                      |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120Initial Configuration20Modifying Configuration at Run Time20Applying the ADF7030-1 Configuration File22ADF7030-1 Configuration File Format22 |

| Introducton18Summary and Recommendations18Format of Memory Access Command18Configuring the Pointers for Pointer Based Accesses19Configuring the ADF7030-120Initial Configuration20Modifying Configuration at Run Time20Applying the ADF7030-1 Configuration File22                                      |

| How to Run the Radio Calibration                     | 24 |

|------------------------------------------------------|----|

| Restoring Saved Calibration Results to the ADF7030-1 | 25 |

| Temperature Sensor                                   | 26 |

| Example Conversion                                   | 26 |

| Transmitting and Receiving Packets                   | 27 |

| Overview                                             | 27 |

| Packet Memory                                        | 27 |

| Packet Formats                                       | 27 |

| Generic Packet Format                                | 28 |

| IEEE 802.15.4g-2012 Packet Format                    | 33 |

| Automatic Frequency Control (AFC) Reporting          | 36 |

| Rolling Buffers Mode                                 | 36 |

| Autoturnaround                                       | 37 |

| Modulation Modes and Line Encoding                   | 37 |

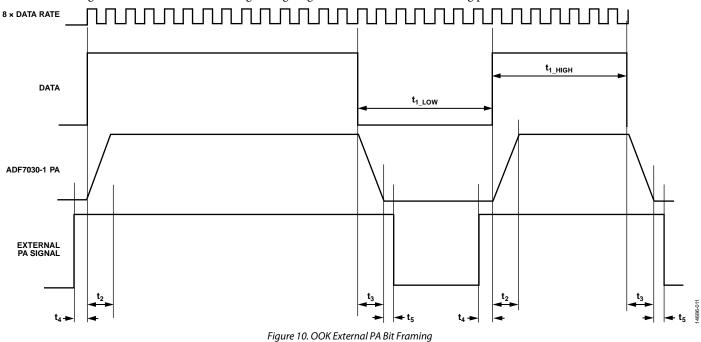

| External PA and LNA Control                          | 39 |

| Test Modes                                           | 39 |

| RSSI, CCA, and Autoturnaround                        | 41 |

| RSSI During Packet Reception                         | 41 |

| CCA                                                  | 41 |

| CCA Detection Time                                   | 41 |

| RSSI Offset Calibration                              | 42 |

| Low Power Modes                                      | 43 |

| PHY_SLEEP                                            | 43 |

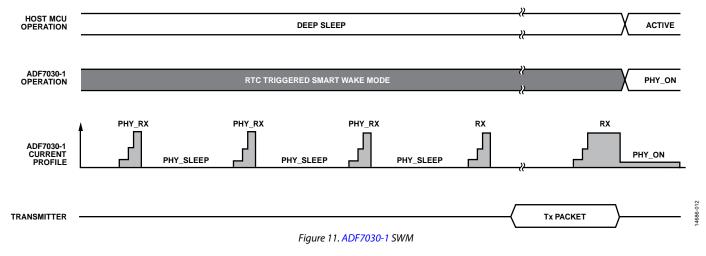

| Smart Wake Mode (SWM)                                | 44 |

| ADF7030-1 Interrupts                                 | 45 |

| Rx and Tx Packet Related Events                      | 45 |

| State Machine Events                                 | 45 |

| Rolling Buffer Events                                | 45 |

| Clearing Interrupts                                  | 45 |

| Mapping Interrupt Outputs onto GPIOs                 | 45 |

| GPIO                                                 | 46 |

| General                                              | 46 |

| Interrupt Outputs                                    | 46 |

| Interrupt Inputs                                     | 46 |

| Using External PA or LNA                             | 46 |

| Host to ADF7030-1 Memory Access Modes                | 47 |

| Note on Endianness                                   | 47 |

| Modes                                                | 47 |

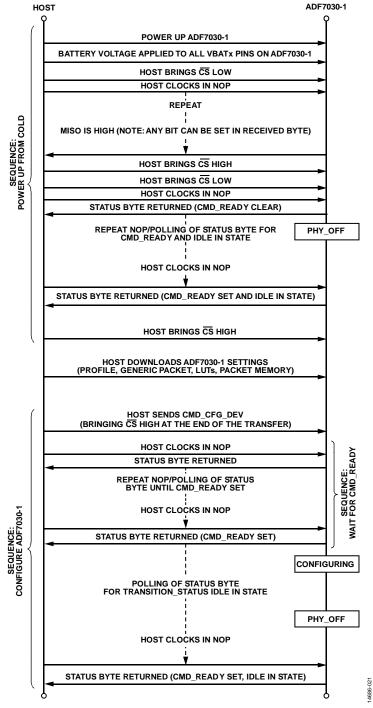

| Host to ADF7030-1 Message Sequence Charts            | 52 |

| Writing the ADF7030-1 Radio Profile from Power-On    | 52 |

|                                                      |    |

ADF7030-1 Software Reference Manual

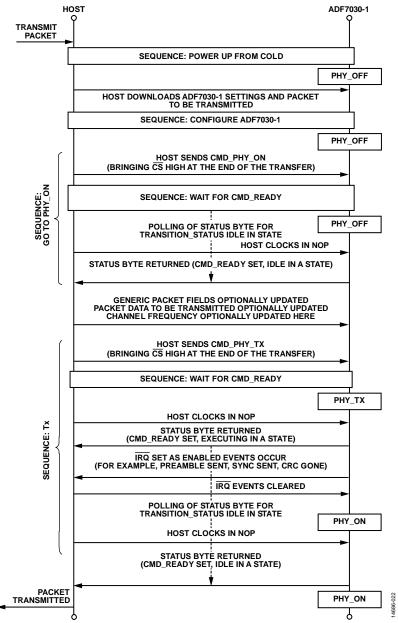

|   | Transmitting a Single Packet from Power-Off                               | .53 |

|---|---------------------------------------------------------------------------|-----|

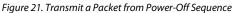

|   | Receiving a Single Packet from Power-Off                                  | .54 |

|   | Calibration Firmware Module, Host Saving ADF7030-1<br>Calibration Results | .55 |

|   | Rx Immediately Following Calibration                                      | .55 |

|   | Rx with Cached Calibration Data                                           | .56 |

| R | egister Summary: ADF7030-1                                                | .57 |

| R | egister Details: ADF7030-1                                                | .61 |

|   | State Machine Wake Source                                                 | .61 |

|   | State Machine Command Triggered by IRQ_IN0 Register                       | .61 |

|   | State Machine Command Triggered by IRQ_IN1 Register                       | .61 |

|   | State Machine Control for Calibration                                     | .61 |

|   | Reference Clock Configuration Register                                    | .61 |

|   | RF Channel Frequency Register                                             | .62 |

|   | Packet Handler Configuration Register                                     | .62 |

|   | Radio Mode Configuration Register                                         | .62 |

|   | Tx Configuration 0 Register                                               | .63 |

|   | Tx Configuration 1 Register                                               | .63 |

|   | Tx Configuration 2 Register                                               | .64 |

|   | AFC Configuration Register 2                                              | .64 |

|   | Calibration Configuration 0 Register                                      | .64 |

|   | Calibration Configuration 1 Register                                      | .65 |

|   | RSSI Configuration Register                                               | .65 |

|   | CCA Configuration Register                                                | .65 |

|   | CCA Readback Register                                                     | .66 |

|   | Low Power Mode Configuration Register                                     | .66 |

|   | RTC Configuration Register                                                | .67 |

|   | Monitor Readback Register                                                 | .67 |

|   | GPIO0 to GPIO3 Pin Functionality Selection Register                       | .67 |

|   | GPIO4 to GPIO7 Pin Functionality Selection Register                       | .68 |

|   | Radio Calibration Results 0 Register                                      | .69 |

|   | Radio Calibration Results 1 Register                                      | .69 |

|   | Radio Calibration Results 2 Register                                      | .69 |

|   | Radio Calibration Results 3 Register                                      | .69 |

|   | Radio Calibration Results 4 Register                                      | .69 |

| Radio Calibration Results 5 Register70              |

|-----------------------------------------------------|

| Radio Calibration Results 6 Register70              |

| Radio Calibration Results 7 Register70              |

| Radio Calibration Results 8 Register70              |

| Transmit/Receive Buffer Configuration 0 Register70  |

| Transmit/Receive Buffer Configuration 1 Register71  |

| Generic Packet Frame Configuration 0 Register71     |

| Generic Packet Frame Configuration 1 Register72     |

| Generic Packet Frame Configuration 2 Register73     |

| Generic Packet Frame Configuration 3 Register73     |

| Generic Packet Frame Configuration 5 Register73     |

| Sync Word 0 Register74                              |

| Sync Word 1 Register74                              |

| CRC Polynomial Register74                           |

| CRC Initial Seed Register74                         |

| CRC XOR Value Register74                            |

| RSSI Configuration Register74                       |

| RX Link Quality Readback Register75                 |

| Low Power Mode Configuration Register75             |

| Test Mode Configuration 0 Register75                |

| Gateway for Software Keyed Instructions Register76  |

| PMU Clock Control Register76                        |

| SPI Slave Pointer 0 Register76                      |

| SPI Slave Pointer 1 Register76                      |

| SPI Slave Pointer 2 Register76                      |

| Mask for External Interrupt 0 (IRQ_OUT0) Register76 |

| Mask for External Interrupt 1 (IRQ_OUT1) Register77 |

| External Interrupt 0 (IRQ_OUT0) Status Register77   |

| External Interrupt 1 (IRQ_OUT1) Status Register78   |

| AFC Configration Register79                         |

| AFC Frequency Error Readback Register79             |

| Processor Clock Enable Register79                   |

| Firmware Status and Debug Register79                |

# UG-1002

# ADF7030-1 Software Reference Manual

# **REVISION HISTORY**

| 6/2018—Rev. A to Rev. B                                     |     |

|-------------------------------------------------------------|-----|

| Changed IEEE802.15.4g to IEEE802.15.4g-2012 Univer          | sal |

| Changes to the ADF7030-1 Operation Section                  | 5   |

| Added Sample Driver Section                                 | 7   |

| Changes to PHY_SLEEP Section                                | 9   |

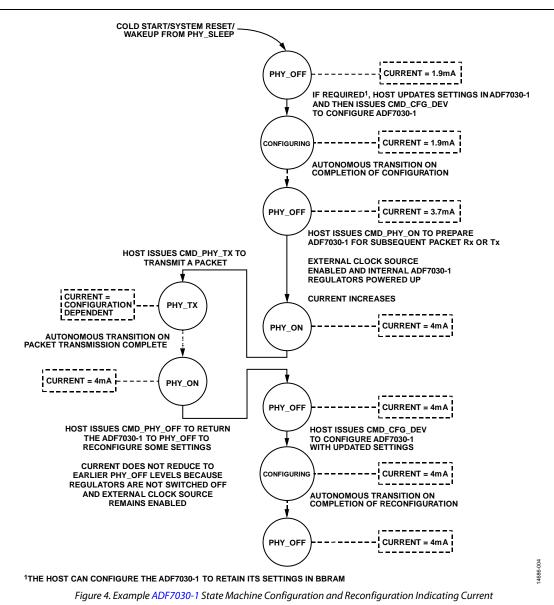

| Changes to Figure 4                                         | 10  |

| Change to Bit 3 Column, Table 6 and Table 7                 | 15  |

| Changes to Bits[31:24] Column, Table 8, Bits[23:14] Column, |     |

| Table 8, and Radio Commands for External Hardware Trigger   | ed  |

| Transitions Section                                         | 16  |

| Changes to Table 10                                         | 17  |

| Changes to Configuring the ADF7030-1 Section                | 20  |

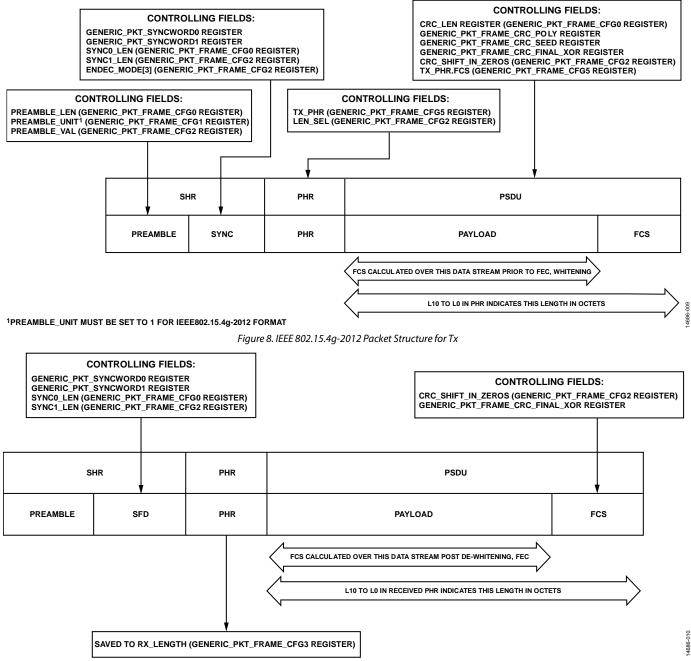

| Changes to IEEE 802.15.4G-2012 Packet Format Section and    |     |

| Figure 8                                                    | 33  |

| Changes to Start Frame Delimiter (SFD) Section and PHY      |     |

| Header (PHR) Section                                        | 34  |

| Added Bit Ordering Over the Air for Transmission Section    |     |

| Changes to Preamble Section, SFD Section, PHR Section, and  | l   |

| PSDU—Payload and FCS Section                                | 35  |

| Changes to Rx to Tx Autoturnaround Section and Tx to Rx     |     |

| Autoturnaround Section                                      |     |

| Changes to External LNA Section and External PA Section     |     |

| Changes to Receive Test Modes Section                       |     |

| Added Packet Error Rate Section                             |     |

| Changes to RSSI During Packet Reception Section             |     |

| Changes to Using External PA or LNA Section                 |     |

| Changes to Figure 22 Caption                                |     |

| Changes to TX_GAUSSIAN_BT Bit Settings and Description      |     |

| Table 36                                                    |     |

| Changes to BIT2AIR Bit Description, Table 59                |     |

| Changes to Table 62                                         |     |

| Changes to LEN_SEL Bit Description, Table 63                |     |

| Change to Address: 0x40003804, Name: IRQ_CTRL_MASK1         |     |

| Section                                                     |     |

| Changes to Table 82                                         | 77  |

| Changes to Table 83                          | 78 |

|----------------------------------------------|----|

| Added ERR_CODE, Bits[31:24], Table 87        |    |

| Changed GENERATED, Bits[31:14] to GENERATED, |    |

| Bits[23:14], Table 87                        | 79 |

# 1/2017—Rev. 0 to Rev. A

| Changes to Figure 26                                         |

|--------------------------------------------------------------|

| Changes to Figure 3                                          |

| Changes to Radio Commands for External Hardware Triggered    |

| Transitions Section and Table 10 16                          |

| Changes to Example of GPIO Triggered Transitions Section and |

| Radio Command for a System Reset Section 17                  |

| Changes to Applying the ADF7030-1 Configuration File         |

| Section and ADF7030-1 Configuration File Format Section 22   |

| Changes to External PA Section, Transmission (Tx) Test Modes |

| Section, and Table 22 39                                     |

| Added Table 23; Renumbered Sequentially 39                   |

| Changes to RSSI Offset Calibration Section                   |

| Changes to Enabling the RTC Section                          |

| Added Determining the Source of a Wake Event after Sleep     |

| Section                                                      |

| Changes to Rolling Buffer Events Section 45                  |

| Added 0x200000E4 Address, Table 26 57                        |

| Added 0x40000C08 Address, Table 27 60                        |

| Added State Machine Wake Source Section and Table 28 61      |

| Changes to Table 35 63                                       |

| Changes to Table 41 65                                       |

| Changes to Table 45 66                                       |

| Changes to Table 48 67                                       |

| Changes to Table 49 68                                       |

| Changes to Table 62 and Table 63 73                          |

| Changes to Table 7476                                        |

| Added PMU Clock Control Register Section and Table 76 76     |

6/2016—Revision 0: Initial Version

# INTRODUCTION

# ADF7030-1 OPERATION

The ADF7030-1 is a very low power, high performance, highly integrated 2FSK/2GFSK/4FSK/4GFSK transceiver designed for operation in the 169.4 MHz to 169.6 MHz, 426 MHz to 470 MHz, and 863 MHz to 960 MHz frequency bands.

The ADF7030-1 supports the multirate frequency shift keying (MR-FSK) physical layer (PHY) 802.15.4g specified in IEEE 802.15.4g<sup>∞</sup>-2012 standard with forward error correction (FEC), whitening, and interleaving at data rates of up to 150 kbps. The ADF7030-1 also supports a proprietary generic packet format. In addition, the ADF7030-1 supports a raw packet format that allows a host to perform packet parsing as data octets are received.

The ADF7030-1 is highly configurable. Begin by generating a configuration for the use case with the ADF7030-1 design center, which can be downloaded from the Analog Devices, Inc., website. Settings that can be altered at run time are described in this document.

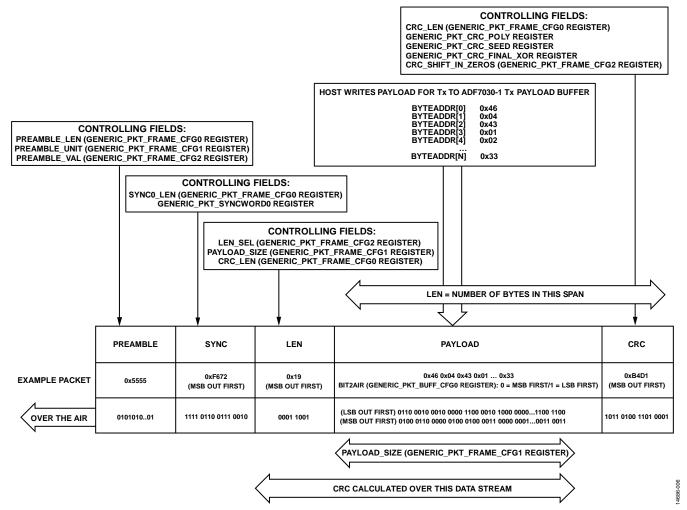

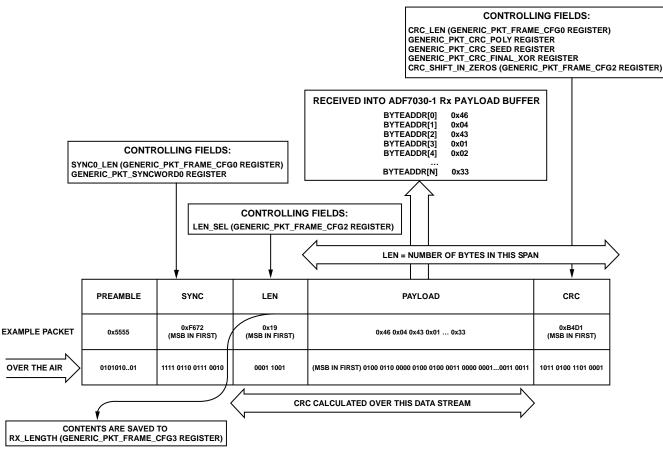

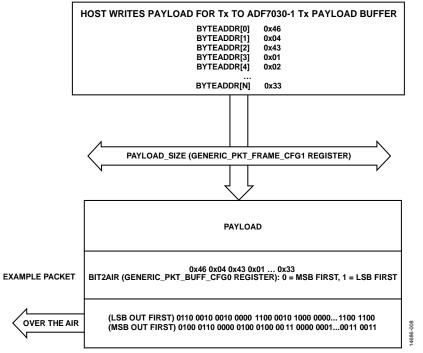

In generic packet transmit (Tx) mode, the ADF7030-1 can be configured to add preamble, sync word, and cyclic redundancy check (CRC) to the payload data stored in the packet memory. The number of preamble bits and sync bits is programmable, and an optional length field can be added to allow packet length decoding at the receiver. In generic packet receive (Rx) mode, the ADF7030-1 can detect, and be configured to interrupt the host processor on, various packet related events (for example, preamble detected, sync word match, and valid CRC) and store the received payload to the packet memory. The CRC polynomial and length are fully programmable in generic packet mode.

Smart wake mode (SWM) allows the ADF7030-1 to wake up autonomously from sleep using the internal real-time clock (RTC) without intervention from the host processor. For systems requiring very accurate wake-up timing, an external 32 kHz oscillator can be used to drive the RTC. Alternatively, the internal resistor/capacitor (RC) oscillator can be used, which consumes less current in sleep. The host can trigger a wakeup from sleep using external signals. Contact Analog Devices for support on SWM.

The ADF7030-1 operates a radio state machine that presents a simple programming model to the host, comprising defined radio states that can be traversed by host commands to the radio. Following application of power to the radio, the ADF7030-1 autonomously enters the PHY\_OFF state. The host must configure the ADF7030-1 with memory writes through the ADF7030-1 serial peripheral interface (SPI). After the host has configured the ADF7030-1, the host can then command the ADF7030-1 into other radio states using single-byte commands that trigger transitions. The host typically issues these commands over the SPI. However, the radio can also be configured to respond to an external interrupt as if it is a specified command.

# ADF7030-1 MEMORY ARCHITECTURE

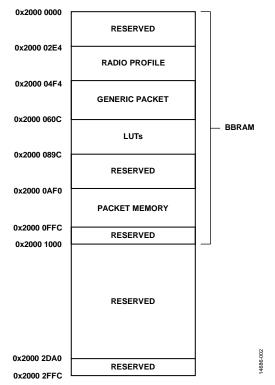

The ADF7030-1 contains 12 kB of random access memory (RAM), 4 kB of which is battery backed random access memory (BBRAM). The RAM starts at Address 0x2000 0000 within the memory map of the ARM Cortex-M0 microprocessor that is at the core of the ADF7030-1. The BBRAM stores the settings of the ADF7030-1 and this configuration is accessible by the host over the ADF7030-1 SPI. The BBRAM of the ADF7030-1 is partitioned into several regions. The ADF7030-1 stores radio settings such as channel frequency, data rate, and filter coefficients in the radio profile and lookup tables (LUTs) regions. The ADF7030-1 stores packet related settings such as packet format, payload length, and sync word in the generic packet region. The host writes packet data for transmission to the packet memory region, and the host reads received packet data from the packet memory region. The other regions within the ADF7030-1 memory are reserved for internal use, including space reserved for firmware modules that Analog Devices supplies to extend the functionality of the ADF7030-1. Several ADF7030-1 hardware registers are also accessible over the SPI to allow the host to control features such as controlling selected ADF7030-1 external interrupts. These registers are not shown in the memory map in Figure 2. Volatile RAM is reserved for potential firmware patches to enable additional functionality.

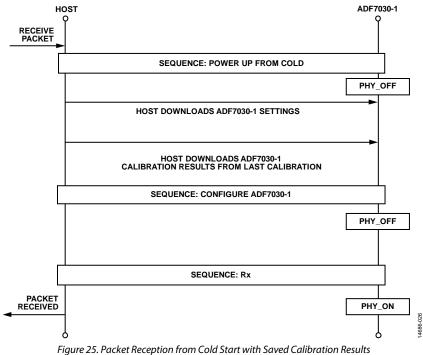

When powered up from cold (that is, battery applied), some default settings are initialized within the ADF7030-1 memory regions. However, these settings do not constitute a full configuration and, therefore, it is the responsibility of the host to initialize the ADF7030-1 settings to the desired values for the application.

# **DEVELOPMENT SUPPORT**

# **DESIGN PACKAGE**

The ADF7030-1 design resource package is a complete documentation and resource package for the ADF7030-1. It is recommended to download this package as a starting point for evaluation and development from the ADF7030-1 product page. It contains manuals, application notes, hardware information, and firmware modules.

# DOCUMENTATION

# ADF7030-1 Data Sheet

The ADF7030-1 data sheet contains the complete specifications and typical performance characteristics for the ADF7030-1. Consult the data sheet in conjunction with this reference manual.

#### ADF7030-1 Software Reference Manual (UG-1002)

The ADF7030-1 Software Reference Manual is the detailed programming guide for the device. The ADF7030-1 Hardware Reference Manual provides a description of the ADF7030-1 hardware features and application circuit requirements.

#### ADF7030-1 Hardware Reference Manual (UG-957)

The ADF7030-1 Hardware Reference Manual provides a description of the ADF7030-1 radio functionality, hardware features, and application circuit requirements. It is intended as a resource for a hardware engineer designing a printed circuit board (PCB) that includes the ADF7030-1.

# **EVALUATION KITS**

Evaluation and development kits are available that include the ADF7030-1 radio daughter boards. The ADF7030-1 EZ-KIT<sup>®</sup> is an evaluation and development system for the ADF7030-1 high performance, sub-GHz, radio frequency (RF) transceiver, and includes four models. These kits are listed in Table 1.

#### Table 1. ADF7030-1 EZ-KIT Models

| Model             | Frequency (MHz) |

|-------------------|-----------------|

| ADF70301-915EZKIT | 902 to 928      |

| ADF70301-868EZKIT | 863 to 876      |

| ADF70301-433EZKIT | 433 to 434      |

| ADF70301-169EZKIT | 169             |

A selection of individual daughter boards is also available covering various frequency bands and matching topologies.

#### **EVALUATION SOFTWARE**

The ADF7030-1 design center can be used for configuring the ADF7030-1, evaluating transmit and receive operation, and transmitting and receiving packets. This ADF7030-1 design center allows the user to rapidly prototype different configurations with the ADF7030-1 and simplifies the migration to host code development.

#### **SAMPLE DRIVER**

A device driver for the ADF7030-1 is available on the ADF7030-1 page on the Analog Devices website under Software & Systems Requirements. Examples are included for the ADF7030-1 EZ-KIT based evaluation platform.

# **ADF7030-1 STATE MACHINE**

# INTRODUCTION

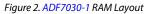

The ADF7030-1 implements a state machine that the host controls via commands. The ADF7030-1 executes a transition from the current state to the next state in response to a command received from the host. These transitions are shown as solid lines in Figure 3. The ADF7030-1 also executes autonomous transitions, shown as dotted lines in Figure 3.

# ADF7030-1 STATES

# PHY\_OFF

The PHY\_OFF state is the default state entered by the ADF7030-1 following a cold start, system reset, or when exiting from the PHY\_SLEEP state. In the PHY\_OFF state, the ADF7030-1 is running using its own internal oscillator clock. The ADF7030-1 transitions into the PHY\_OFF state from the PHY\_SLEEP state on a wake-up event (RTC alarm, GPIO2 and GPIO4 if configured as interrupt request (IRQ) inputs, or an SPI active low chip select ( $\overline{\text{CS}}$ ) low to high transition). In addition, the PHY\_OFF state can be entered from the PHY\_ON state and is entered autonomously from the configuring state. It is recommended that some of the ADF7030-1 settings be changed only when in the PHY\_OFF state. The ADF7030-1 current in the PHY\_OFF state is typically 1.9 mA and this increases to 3.7 mA if there has been a transition to PHY\_ON and back to PHY\_OFF.

# PHY\_SLEEP

The PHY\_SLEEP state is the lowest current state of the ADF7030-1. In the PHY\_SLEEP state, the ADF7030-1 memory regions are not accessible by the host (they are accessible by the host in all other states). The GPIOx configuration (direction and values) is retained while the ADF7030-1 is in the PHY\_SLEEP state.

The host commands the ADF7030-1 to enter the PHY\_SLEEP state from the PHY\_OFF or PHY\_ON state. When the host issues the CMD\_PHY\_SLEEP command in either of these two states, the ADF7030-1 turns off its internal regulators. The host enables ADF7030-1 BBRAM retention by setting the RETAIN\_SRAM and enable bit in Register PROFILE\_LPM\_CFG0 before entering PHY\_SLEEP. The host can also configure RTC related settings of the ADF7030-1 such that power is maintained to the ADF7030-1 internal RTC during the PHY\_SLEEP state. The RTC can be configured to generate a periodic wake-up event to trigger an autonomous exit from the PHY\_SLEEP state into the PHY\_OFF state. The host must set the RETAIN\_SRAM and enable fields before issuing a CMD\_CFG\_DEV command for the settings to take effect on entry into PHY\_SLEEP.

To enable the retention of the ADF7030-1 BBRAM for a subsequent PHY\_SLEEP transition, the host must set the RETAIN\_SRAM and enable bit in Register PROFILE\_LPM\_CFG0 prior to issuing the CMD\_CFG\_DEV command.

# Configuring

When in the PHY\_OFF state, the host can update the ADF7030-1 configuration over the SPI by writing to memory regions and issuing the CMD\_CFG\_DEV command afterward. The ADF7030-1 state machine automatically returns from the configuring state to the PHY\_OFF state when this configuration has completed. The CMD\_CFG\_DEV command must only be issued in the PHY\_OFF state. The current in the configuring state is the same as the current in the PHY\_OFF state prior to the host issuing the CMD\_CFG\_DEV command.

#### PHY\_ON

In the PHY\_ON state, the radio can quickly transition to PHY\_RX to receive a packet or PHY\_TX to transmit a packet. On its first transition from the PHY\_OFF state to the PHY\_ON state following a power cycle, system reset, or exit from PHY\_SLEEP, the ADF7030-1 switches from using its internal oscillator to the external reference clock source, an external crystal (XTAL), or thermally compensated crystal oscillator (TCXO), as configured. The ADF7030-1 also powers up internal regulators in this first transition from PHY\_OFF to PHY\_ON.

The host must not issue a command to enter PHY\_ON unless the ADF7030-1 has been configured using the CMD\_CFG\_DEV command since the last power cycle, system reset, or exit from PHY\_SLEEP.

The host can change some ADF7030-1 settings in the PHY\_ON state without the need to update the ADF7030-1 configuration via a CMD\_CFG\_DEV command. These settings include channel frequency and all packet related settings. The ADF7030-1 dynamically applies these settings to the hardware during the transition from PHY\_ON to the PHY\_CCA, PHY\_TX, and PHY\_RX states, without the need for an intervening CMD\_CFG\_DEV command from the host.

The ADF7030-1 current in the PHY\_ON state is typically 3.7 mA.

# UG-1002

# РНҮ ТХ

In the PHY\_TX state, the ADF7030-1 transmits the packet data. The ADF7030-1 can be configured to autonomously transition from the PHY\_TX state to the PHY\_ON state once the ADF7030-1 has fully transmitted the packet. This autonomous transition is labeled TX\_EOF in Figure 3. However, the ADF7030-1 can also be configured to autonomously transition from the PHY\_TX state to the PHY\_RX state (called Tx to Rx autoturnaround) after the ADF7030-1 has fully transmitted the packet. This autonomous transition is labeled TX\_TO\_RX\_AUTO\_TURNAROUND in Figure 3. The ADF7030-1 also supports transmission test modes including continuous carrier wave (CW) and pseudorandom binary sequence (PRBS) transmission. The host can command the ADF7030-1 to return to the PHY\_ON state by issuing a CMD\_PHY\_ON command in the PHY\_TX state. Any packet being transmitted at that time is aborted. The host can also command the ADF7030-1 to enter the PHY\_RX state by issuing a CMD\_PHY\_RX command. Any packet being transmitted at that time is aborted. The ADF7030-1 current in the PHY\_TX state depends on ADF7030-1 settings, such as transmission power and data rate. See the Transmitting and Receiving Packets section for more details on packet transmission.

# PHY\_RX

In the PHY\_RX state, the ADF7030-1 receives packets. The ADF7030-1 can be configured to autonomously transition from the PHY\_RX state to the PHY\_ON state after the ADF7030-1 has received a packet (even if the received packet has an error such as CRC failure). This autonomous transition is labeled RX\_EOF in Figure 3. The ADF7030-1 can also be configured to autonomously transition from the PHY\_RX state to the PHY\_TX state (called Rx to Tx autoturnaround) after the ADF7030-1 has received a packet without error. If the programmed CRC length, CRC\_LEN in the GENERIC\_PKT\_FRAME\_CFG0 register, is 0, a received packet is assumed to be valid. This autonomous transition is labeled RX\_TO\_TX\_AUTO\_TURNAROUND in Figure 3. The host can command a transition from the PHY\_RX state to the PHY\_ON state without having to wait for the ADF7030-1 to receive a packet by issuing a CMD\_PHY\_ON command. Any packet being received at that time is aborted. The ADF7030-1 current in the PHY\_RX state depends on configuration settings such as data rate and packet format. See the Transmitting and Receiving Packets section for more details on packet reception.

# Clear Channel Assessment (CCA)

In the CCA state, the ADF7030-1 continually measures the received signal strength indicator (RSSI) level and compares it against a configurable RSSI threshold, until the expiration of a configurable time interval. On the expiration of the time interval, the ADF7030-1 autonomously transitions from the CCA state to the PHY\_TX state if the measured RSSI did not exceed the threshold at any instant during the time interval. If, however, the measured RSSI did exceed the threshold at any instant during the time interval, the ADF7030-1 returns to the PHY\_ON state, when the time interval expires. These autonomous transitions are labeled clear channel and busy channel, respectively, in Figure 3. The result of the comparison is available for the host to interrogate. This functionality can be used by the host to support CCA functionality as specified in the IEEE 802.15.4g-2012 standard (Part 15.4) for MR-FSK. Note that packet reception is not possible during PHY\_CCA.

# Calibrating

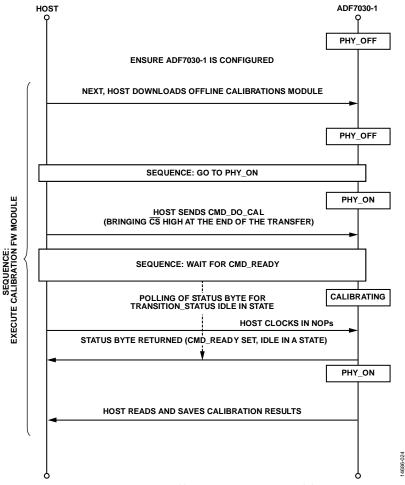

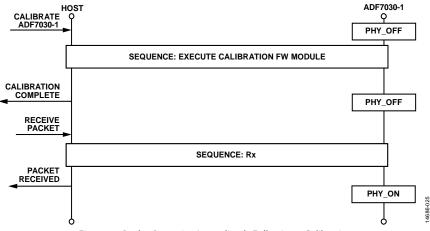

The ADF7030-1 requires a system calibration that can be applied by downloading a firmware module supplied by Analog Devices. This is called the **OfflineCalibrations.cfg** module. The host must download this firmware module when the ADF7030-1 is in the PHY\_OFF state. When the firmware is downloaded, the host can execute a system calibration by issuing the CMD\_DO\_CAL command from the PHY\_ON state. The ADF7030-1 autonomously returns to the PHY\_ON state after the system calibration is complete.

Following the autonomous return to PHY\_ON, the host can read back specific values from the profile memory region that contains system settings optimized as a result of the system calibration. The host can write these values back to the profile memory region when the ADF7030-1 is in the PHY\_OFF state, which reapplies the results of the previous system calibration without the need to issue a CMD\_DO\_CAL command.

Note that the **OfflineCalibrations.cfg** firmware module is not stored in battery backed up memory and, therefore, is not retained if the ADF7030-1 undergoes a power cycle, system reset, or exits the PHY\_SLEEP state. In these instances, the host must reload the **OfflineCalibrations.cfg** firmware module in the PHY\_OFF state before it can issue a CMD\_DO\_CAL command.

# Monitoring

The host issues the CMD\_MON command to the ADF7030-1 to measure and report the ADF7030-1 temperature in the PHY\_ON state. The ADF7030-1 autonomously returns to the PHY\_ON state on completion. The ADF7030-1 reports the temperature as a signed number in units of 0.0625°C.

# STATE TRANSITION TIMING

Consult the ADF7030-1 data sheet for state transition timing information.

# **ADF7030-1 SPI**

# INTRODUCTION

The ADF7030-1 provides an SPI to facilitate configuration and control by a host. The host uses the SPI to read and write ADF7030-1 memory and registers, to issue commands, track the status of the state machine, and to wake up the ADF7030-1 from PHY\_SLEEP. The ADF7030-1 operates as an SPI slave.

# **SPI PINS**

The SPI connections between the host and ADF7030-1 are as shown in Table 2.

| Table 2 | . Host | Interface | Connections |

|---------|--------|-----------|-------------|

|---------|--------|-----------|-------------|

| Generic SPI Signal Name               | Description                                                              | ADF7030-1 Pin Name | Direction            |  |

|---------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------|--|

| SPI Chip Select Enable                | Host brings this line low to select the SPI slave for SPI data exchange  | <u>cs</u>          | Host to<br>ADF7030-1 |  |

| SPI Clock                             | Host drives this signal to clock serial data in and out of the SPI slave | SCLK               | Host to<br>ADF7030-1 |  |

| SPI Master Output, Slave Input (MOSI) | Serial data sent from the SPI master to the SPI slave                    | MOSI               | Host to<br>ADF7030-1 |  |

| SPI Master Input, Slave Output (MISO) | Serial data sent from the SPI slave to the SPI master                    | MISO               | ADF7030-1 to<br>host |  |

# SPI Chip Select Enable

The host must connect its SPI slave enable signal to the  $\overline{CS}$  input of the ADF7030-1. To initiate an SPI transaction, the host drives  $\overline{CS}$  low before the first SCLK rising edge and drives it high again after the last SCLK falling edge. The ADF7030-1 ignores the SPI SCLK and MOSI signals while its  $\overline{CS}$  input is high.

#### SPI SCLK

SCLK is the serial clock driven by the host to the ADF7030-1.

#### SPI MOSI and SPI MISO

MOSI is the data input line driven from the host to the ADF7030-1, and MISO is the data output from the ADF7030-1 to the host. MOSI and MISO are launched on the falling edge of SCLK and sampled on the rising edge of SCLK by the host and the ADF7030-1, respectively. MOSI carries the data from the host to the ADF7030-1. MISO carries the returning read data fields from the ADF7030-1 to the host during a read transaction. If a valid logic state on MISO is required at all times by the host, an external weak pull-up/pull-down resistor must be added on the PCB.

# HOST INITIALIZATION OF ADF7030-1 SPI

On cold start system reset or wakeup from PHY\_SLEEP, the host must wait until the ADF7030-1 SPI is ready for a SPI command transfer. The sequence the host must follow to issue the first SPI command is as follows (refer to the digital timing specifications in the ADF7030-1 data sheet for details of exact sequence):

- 1. The host brings  $\overline{\text{CS}}$  low (if the ADF7030-1 is in PHY\_SLEEP, this wakes up the device).

- 2. The host must monitor MISO and wait until it goes high. No SPI clock is needed for this to occur.

- 3. The host brings  $\overline{CS}$  high. The SPI is now ready for an SPI command.

# SPI TRANSACTIONS

The host is the master of the SPI and the following requirements must be met:

- When  $\overline{\text{CS}}$  is brought low for an SPI transfer, a multiple of eight clock cycles must be generated by the host. Partial or fragmented transfers (for example, 33 clocks) are not supported.

- In every octet, the MSB (Bit 7) is transmitted or received first. This bit is followed by the next MSB (Bit 6), and so on (Bit 7, Bit 6, Bit 5, Bit 4, Bit 3, Bit 2, Bit 1, and Bit 0).

- If the  $\overline{CS}$  line is brought high at any time by the host, the ADF7030-1 is ready to accept a new SPI transaction when  $\overline{CS}$  is brought low again by the host.

- Data transfers consisting of multiple bytes can be achieved without having to deassert and reassert  $\overline{\text{CS}}$  at any stage during the transfer (contingent on the first requirement of the clock cycles being in multiples of 8). This feature allows the host to design a SPI driver that does not require repeated configuration and restarting, as is typically necessary, making a host-based direct memory access (DMA) solution ideal.

### SPI Transaction Timings

See the ADF7030-1 data sheet for SPI interface timing specifications.

**UG-1002**

# ADF7030-1 SPI COMMUNICATION

# **COMMAND BYTE**

The host controls the ADF7030-1 over the SPI interface. The ADF7030-1 implements a simple protocol to which the host must conform. The first byte of MOSI data in an SPI transaction (defined as data transferred when  $\overline{CS}$  is active low) is the command. The ADF7030-1 uses the CNM bit of the command to differentiate between a radio command and a memory command. Table 3 shows the format of the command.

#### Table 3. Command Format

| Bit 7 | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------------------------|-------|-------|-------|-------|-------|-------|

| CNM   | Command dependent fields |       |       |       |       |       |       |

# **RADIO COMMANDS**

The host controls the ADF7030-1 by issuing radio commands over the SPI.

A radio command triggers the ADF7030-1 to execute an immediate transition from the current state to a commanded state. The host also uses a radio command to configure the ADF7030-1 to execute a state machine transition in response to a signal on a configurable GPIOx pin. The host can also trigger an ADF7030-1 system reset by issuing a radio command.

In response to a radio command from a host, the ADF7030-1 sets a CMD\_READY bit that indicates that the command has been received. When set, this bit also indicates that the host can issue another command (for example, to abort the current transition). Finally, when set, this bit indicates to the host that it can read a specific ADF7030-1 register that reflects the state of the ADF7030-1 state machine.

The ADF7030-1 makes the CMD\_READY bit available over the SPI. The host can configure the ADF7030-1 to generate an interrupt when CMD\_READY goes high.

#### Radio Commands to Trigger a State Machine Transition

The format of a radio command that triggers the ADF7030-1 to execute a transition between states is shown in Table 4. The host sets the desired destination state in Bits[4:0]. The host must guarantee that the transition between the current state and the requested state is supported as shown in Figure 3. If an unsupported transition is commanded, the ADF7030-1 remains in the current state.

#### Table 4. Radio Command Format for State Machine Control

| Bit 7   | Bit 6       | Bit 5        | Bit 4                           | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------------|--------------|---------------------------------|-------|-------|-------|-------|

| CNM = 1 | SPCNTRN = 0 | Reserved = 0 | Destination state (see Table 5) |       |       |       |       |

| Command       | Destination State | Description of ADF7030-1 Action                                                               |

|---------------|-------------------|-----------------------------------------------------------------------------------------------|

| CMD_PHY_SLEEP | 0x00              | Performs a transition of the device into the PHY_SLEEP state                                  |

| CMD_PHY_OFF   | 0x01              | Performs a transition of the device into the PHY_OFF state                                    |

| CMD_PHY_ON    | 0x02              | Performs a transition of the device into the PHY_ON state                                     |

| CMD_PHY_RX    | 0x03              | Performs a transition of the device into the PHY_RX state to receive a packet                 |

| CMD_PHY_TX    | 0x04              | Performs a transition of the device into the PHY_TX state to transmit a packet                |

| CMD_CFG_DEV   | 0x05              | Configures the ADF7030-1                                                                      |

| CMD_CCA       | 0x06              | Performs CCA                                                                                  |

| CMD_DO_CAL    | 0x09              | Executes device calibration (requires the OffLineCalibrations.cfg FW module)                  |

| CMD_GPCLK     | 0x10              | A nonreturnable state where a programmable clock is generated on the selectable GPIOx pin     |

| CMD_MON       | 0x0A              | Measures and reports the ADF7030-1 temperature                                                |

| CMD_LFRC_CAL  | 0x0C              | Performs low frequency RC (LFRC) oscillator calibration for the internal 26 kHz RC oscillator |

#### Table 5. State Machine Radio Commands

### Tracking State Machine Transitions

The ADF7030-1 provides several methods by which a host can track its state machine transitions.

#### Using the CMD\_READY Event

The ADF7030-1 generates a CMD\_READY event when it has started the transition to the commanded state. This event can be configured to generate an interrupt to the host (see the Clearing Interrupts section). This event also indicates that the host can read the MISC\_FW register that contains the current state of the ADF7030-1 state machine. Additionally, this event indicates that the host can send another radio command to abort the current transition.

#### Using the SM\_IDLE Event

The ADF7030-1 generates the SM\_IDLE event to indicate when the ADF7030-1 has completed the commanded transition. This event can be configured to generate an interrupt to the host (see the Clearing Interrupts section). As an example of its use, if the current state of the ADF7030-1 is PHY\_OFF and the host commands a transition to the PHY\_ON state (command = 0x82), the ADF7030-1 generates the SM\_IDLE event when the transition to PHY\_ON has completed.

#### **Autonomous Transitions**

The ADF7030-1 executes some transitions autonomously. For example, when the ADF7030-1 is in the PHY\_ON state and the host commands a transition to the PHY\_TX state (command = 0x84), the ADF7030-1 does not generate the SM\_IDLE event until the ADF7030-1 has completed the autonomous transition back to PHY\_ON state after the packet transmission has completed. In this case, the SM\_IDLE event indicates the ADF7030-1 has completed a chain of transitions initiated by a single radio command.

#### Using the ADF7030-1 Status over SPI

The ADF7030-1 also reports status via a status byte. The ADF7030-1 returns this byte on the SPI MISO pin in response to a no operation (NOP), 0xFF, on the SPI MOSI. The format of the status byte is shown in Table 6.

This status byte contains the CMD\_READY in Bit 5. The status byte also contains the TRANSITION\_STATUS field. This field reflects the phases of a transition of the ADF7030-1 state machine.

#### Table 6. ADF7030-1 Status Byte Format

| Bit 7    | Bit 6    | Bit 5     | Bit 4    | Bit 3 | Bit 2     | Bit 1    | Bit 0    |

|----------|----------|-----------|----------|-------|-----------|----------|----------|

| Reserved | Reserved | CMD_READY | Reserved | ERR   | TRANSITIO | N_STATUS | Reserved |

#### Table 7. ADF7030-1 Status Byte Descriptions

| Bit No. | Bit Name          | Description                                                                                                                                          |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | Reserved          | Unused                                                                                                                                               |

| 6       | Reserved          | Unused                                                                                                                                               |

| 5       | CMD_READY         | 0: the radio controller is not ready to receive a radio controller command<br>1: the radio controller is ready to receive a radio controller command |

| 4       | Reserved          | Unused                                                                                                                                               |

| 3       | ERR               | Error code, indicating an error has occurred.                                                                                                        |

| [2:1]   | TRANSITION_STATUS | 0: transition in progress<br>1: executing in a state<br>2: idle in a state                                                                           |

| 0       | Reserved          | Unused                                                                                                                                               |

#### Using the MISC\_FW Register

The ADF7030-1 updates an internal register called MISC\_FW that reflects the current state of the ADF7030-1 state machine. The encoding of the CURR\_STATE field of the MISC\_FW register of the ADF7030-1 matches that of the destination state field in Table 4. This register also contains the transition status field that is available in the SPI status byte. It is recommended that the host read the MISC\_FW register only after the CMD\_READY bit has gone high following a radio command.

The format of the MISC\_FW register is shown in Table 8.

#### Table 8. MISC\_FW Format

| Bits[31:24]           | Bits[23:14] | Bits[13:8]                | Bits[7:2] | Bits[1:0]                       |

|-----------------------|-------------|---------------------------|-----------|---------------------------------|

| ERR_CODE <sup>1</sup> | Reserved    | CURR_STATE (see Table 87) | Reserved  | TRANSITION_STATUS (see Table 6) |

<sup>1</sup> ERR\_CODE is the readback of the error code description.

#### Issuing a Radio Command over the SPI

In response to receiving a radio command from the host, the ADF7030-1 clears the CMD\_READY bit. Clearing this bit indicates to the host that the ADF7030-1 is not yet ready to receive another radio command. While CMD\_READY is low, the host must not write another radio command to the SPI slave.

The ADF7030-1 sets CMD\_READY high to indicate to the host that it can send another radio command. Note that this does not indicate that the ADF7030-1 has completed the required actions associated with the radio command (for example, a state machine transition). Instead, it indicates that the radio command has been received and that the required actions associated with the radio command are in progress. The host can abort those actions by issuing another radio command any time after CMD\_READY is high.

For example, having issued a CMD\_PHY\_TX command, the host, subsequent to seeing CMD\_READY go high but before seeing the packet has finished transmitting, can issue CMD\_PHY\_ON to abort the transmission and return the ADF7030-1 state machine to the PHY\_ON state.

# **RADIO COMMANDS FOR EXTERNAL HARDWARE TRIGGERED TRANSITIONS**

The ADF7030-1 SPI protocol also supports radio commands that do not trigger a state machine transition. Using these configuration radio commands, the host can configure the ADF7030-1 to execute a transition in response to a signal from two of its GPIOx pins. This functionality is useful when it is desirable to configure the ADF7030-1 to execute a transition in response to periodically generated hardware events.

The host must only send these configuration radio commands when the ADF7030-1 is in the PHY\_OFF or PHY\_ON state. See Table 9 for the format of the command.

The ADF7030-1 supports two interrupt inputs, IRQ\_IN0 and IRQ\_IN1. The host can map these interrupt inputs onto any of the ADF7030-1 GPIOx pins (see the ADF7030-1 Interrupts section).

To use the interrupt inputs, the host first configures which transition the ADF7030-1 must execute if a rising signal is applied to IRQ\_IN0 or IRQ\_IN1 by writing a byte to the SM\_CONFIG\_GPIO\_CMD\_0 register or the SM\_CONFIG\_GPIO\_CMD\_1 register, respectively. The byte value written must be the same 8-bit radio command that generates the desired transition if it is sent over the SPI. Next, the host sends the radio command to enable the IRQ\_IN0 interrupt or the IRQ\_IN1 interrupt (see Table 9). The ADF7030-1 then executes the preconfigured radio command whenever a rising edge appears on the general-purpose input/output (GPIO) configured for IRQ\_IN0 or IRQ\_IN1.

#### Table 9. Configuration Radio Command Structure

| Bit 7 | Bit 6   | Bit 5                            | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|---------|----------------------------------|-------|-------|-------|-------|-------|

| CNM   | SPCNTRN | Configuration command identifier |       |       |       |       |       |

| 1     | 1       | See Table 10                     |       |       |       |       |       |

| Command               | Configuration Command Identifier | Description of ADF7030-1 Action                                               |

|-----------------------|----------------------------------|-------------------------------------------------------------------------------|

| CMD_IRQ1_DIS_IRQ0_DIS | 0x0C                             | Disable hardware triggered transition                                         |

| CMD_IRQ1_DIS_IRQ0_EN  | 0x0D                             | Disable IRQ_IN1 and enable IRQ_IN0 for triggering preloaded radio commands    |

| CMD_IRQ1_EN_IRQ0_DIS  | 0x0E                             | Enable IRQ_IN1 and disable IRQ_IN0 for triggering preloaded radio<br>commands |

| CMD_IRQ1_EN_IRQ0_EN1  | 0x0F                             | Enable IRQ_IN1 and IRQ_IN0 for triggering preloaded radio commands            |

#### Table 10. Configuration Radio Command Identifier

<sup>1</sup> In addition to (and subsequent to) the Radio Command 0x8F enabling both interrupts, the host must write a value of 0x0808 to the 16-bit data word at Address 0x40003818.

# **Example of GPIO Triggered Transitions**

For the host to trigger a PHY\_ON to PHY\_TX transition using a low to high transition on a GPIOx pin and a PHY\_ON to PHY\_OFF state transition using a low to high transition on a separate GPIOx pin, follow these steps:

- 1. Configure the selected GPIOs as interrupt inputs, IRQ\_IN0 and IRQ\_IN1 (see the ADF7030-1 Interrupts section).

- 2. Preload the commands.

- a. The host writes the command value for CMD\_PHY\_TX (0x84) into the 8-bit location at SM\_CONFIG\_GPIO\_CMD\_0.

- b. The host writes the command value for CMD\_PHY\_OFF (0x81) into the 8-bit location at SM\_CONFIG\_GPIO\_CMD\_1.

- 3. Enable the interrupt inputs.

The host enables the ADF7030-1 to execute the preloaded command in response to a rising edge on the IRQ\_IN0 or IRQ\_IN1 input, respectively, by sending the CMD\_IRQ1\_EN\_IRQ0\_EN (0xCF) configuration radio command to the ADF7030-1 over the SPI.

As a result, the ADF7030-1 is configured so that a rising edge on the ADF7030-1 GPIOx pin configured as IRQ\_IN0 is equivalent to sending a CMD\_PHY\_TX command over the SPI to the ADF7030-1.

Similarly, the ADF7030-1 is configured so that a rising edge on a GPIOx pin configured as IRQ\_IN1 is equivalent to sending a CMD\_PHY\_OFF command over the SPI to the ADF7030-1.

The host can track the transition triggered with this method in the same manner as if the radio command was sent over the SPI.

# **RADIO COMMAND FOR A SYSTEM RESET**

The host can reset the ADF7030-1 over the SPI using the following sequence:

- 1. Set Bit 15 and Bit 22 of the CRMGT\_PROC\_CLK\_EN register to 1. Read the register and then write the new value using a 32-bit SPI write (see the Accessing the ADF7030-1 Memory section).

- 2. Write 0x27 to the SW\_KEY bit of the PMU\_KEY register using a 32-bit SPI write.

- 3. Immediately write 0x1 to the HFRC\_PD\_N bit of the PMU\_CLOCKS register using a 32-bit SPI write.

- 4. Issue the 0xC7 radio reset command to perform a full system reset of the radio.

# ACCESSING THE ADF7030-1 MEMORY

# INTRODUCTON

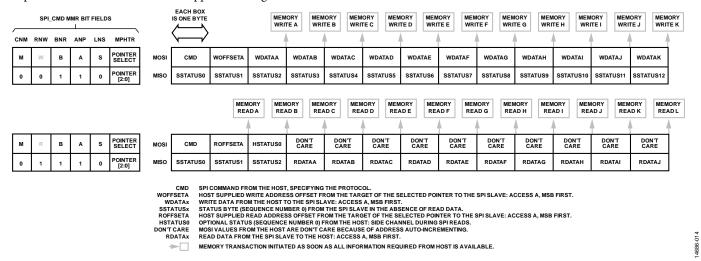

The ADF7030-1 SPI supports a flexible memory access protocol that allows the host to access the ADF7030-1 memory efficiently. The protocol supports auto-incrementing addressing for reading or writing blocks of data, base plus offset addressing using three dedicated base address pointers in the ADF7030-1, and individual byte and 4-byte word transfers. See the Host to ADF7030-1 Memory Access Modes section for information about the order of the SPI MISO and SPI MOSI data for each memory protocol. The host is free to choose the protocol that best suits the design of the host SPI.

The host uses the SPI memory access protocols to read and write the memory regions of the ADF7030-1. The format of the SPI transaction starts with a command word with the CNM bit = 0.

The host does not need to monitor the CMD\_READY bit before it can read or write ADF7030-1 memory.

All ADF7030-1 RAM can be accessed using byte wide accesses. However, some ADF7030-1 registers must only be accessed using a 32-bit data protocol. This restriction is detailed where relevant.

# SUMMARY AND RECOMMENDATIONS

There are eight different memory access modes (see Table 11).

#### Table 11. Access Modes

| Address Mode                                                                | Recommended for Accessing                                                        |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Memory Write/Read, Block, No Pointer, Long Address                          | One block of 4-byte words written or read once                                   |

| Memory Write/Read, Block, Pointer Base with Offset Address, Short Address   | Different subblocks of bytes written or read often within a larger block of data |

| Memory Write/Read, Block, Pointer, Long Address                             | One block of 4-byte words written or read often                                  |

| Memory Write/Read, Block, Pointer, Short Address                            | One block of bytes written or read often                                         |

| Memory Write/Read, Random, No Pointer, Long Address                         | One 4-byte word written or read once                                             |

| Memory Write/Read, Random, Pointer Base with Offset Supplied, Short Address | Different single bytes written or read from within a block                       |

| Memory Write/Read, Random, Pointer, Long Address                            | One 4-byte word written or read often                                            |

| Memory Write/Read, Random, Pointer, Short Address                           | One byte written or read often                                                   |

# FORMAT OF MEMORY ACCESS COMMAND

The format of the command byte for memory accesses command is shown in Table 12. See Table 13 for the bit descriptions.

#### Table 12. Memory Access Command

| Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| CNM = 0 | RNW   | BNR   | ANP   | LNS   |       | MPTR  |       |

#### Table 13. Memory Access Command Bit Descriptions

| Bit No. | Bit Name | Description                                                                                                                                               |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6       | RNW      | Read, not write.                                                                                                                                          |

|         |          | 0: writes for the duration of the current $\overline{CS}$ active low time.                                                                                |

|         |          | 1: reads for the duration of the current $\overline{CS}$ active low time.                                                                                 |

| 5       | BNR      | Block (burst), not random, auto-incrementing address indicator for memory transfers.                                                                      |

|         |          | 0: execute random memory accesses whose address has no connection with any foregoing transfer during the same CS low time.                                |

|         |          | 1: block (burst) memory accesses, whereby each access has its address auto-incremented from the immediately foregoing access during the same CS low time. |

| 4       | ANP      | Address, not pointer, address source indicator for memory transfers.                                                                                      |

|         |          | 0: no address information is supplied by the host for either long or short format memory transfers. Exclusively pointer-based addresses are used instead. |

|         |          | 1: host supplies a full address for long format memory transfers and a pointer address offset for short format memory transfers.                          |

| 3       | LNS      | Long, not short, memory transfer width format.                                                                                                            |

|         |          | 0: issue a short format, pointer-based, optionally offset, byte wide, byte aligned memory transfer.                                                       |

|         |          | 1: issue a long format, 32-bit, word aligned, host specified memory transfer.                                                                             |

| Bit No. | Bit Name | Description                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------|

| [2:0]   | MPNTR    | Base address selection for pointer-based memory accesses.                                  |

|         |          | 000: used to set up Pointer 0, Pointer 1, and Pointer 2.                                   |

|         |          | 001: reserved.                                                                             |

|         |          | 010: reserved.                                                                             |

|         |          | 011: reserved.                                                                             |

|         |          | 100: reserved.                                                                             |

|         |          | 101: use the contents of Pointer 0 as the base address for pointer-based memory transfers. |

|         |          | 110: use the contents of Pointer 1 as the base address for pointer-based memory transfers. |

|         |          | 111: use the contents of Pointer 2 as the base address for pointer-based memory transfers. |

# CONFIGURING THE POINTERS FOR POINTER BASED ACCESSES

The host can configure each of the three ADF7030-1 pointers with a 32-bit address for pointer-based addressing. The SPI command used to write to the pointers is 0x28: memory access (CNM = 0), write (RNW = 0), block (BNR = 1), pointer (ANP = 0), long format (LNS = 1), access pointers themselves (MPNTR = 000). See the Memory, Block, Pointer, Long Address section for more information.

# **CONFIGURING THE ADF7030-1**

The ADF7030-1 transceiver can be configured for different frequency bands, data rates, frequency deviations, and packet formats. From a user perspective, configuring the ADF7030-1 entails writing register settings to the BBRAM section of the radio memory over the SPI. The layout of the radio memory is described in the ADF7030-1 Memory Architecture section. See Figure 2 for an overview of the memory layout.

From a user perspective, the ADF7030-1 has the following three sections in memory used for configuring the radio:

- The radio profile area, PROFILE, stores the radio RF settings. This area includes the channel frequency, CCA settings, low power mode configuration, and GPIO configuration.

- The packet area, GENERIC\_PACKET, stores packet configuration settings for both the generic packet format and IEEE 802.15.4g-2012 packet format. This area includes the packet length, payload location, sync word or PHY header (PHR) length, and value and CRC/frame check sequence (FCS) configurations.

- Various lookup tables (LUTs) are stored in memory. These LUTs are used for configuring internal radio blocks and running and storing the results from calibrations.

As shown in the ADF7030-1 register map, the contents of the lookup tables and many of the fields in the profile and generic packet sections are labeled as generated. These fields are generated by the ADF7030-1 design center graphical user interface (GUI) based on the RF and packet settings of the user. This ADF7030-1 design center is part of the EZ-KIT\* design suite, a set of tools for configuring and evaluating Analog Devices low power integrated transceiver products. The ADF7030-1 design center generates a **Radio Configuration** tab that allows a user to enter their desired RF and packet settings. The ADF7030-1 design center generates a corresponding configuration (CFG) file for these settings, containing all required radio settings, including the appropriate LUTs, that can then be written to the device by the user.

The first step in using the ADF7030-1, called the initial configuration, is applying the settings generated by the ADF7030-1 design center to the device. After this configuration step, a user can optionally choose to modify some settings while the device is running.

# **INITIAL CONFIGURATION**

The following steps are required to set up the ADF7030-1 upon a cold startup:

Generate the user settings in the ADF7030-1 design center. Enter the desired RF and packet settings in the Radio Configuration tab of the ADF7030-1 design center. This produces an ADF7030-1 configuration file to write to the radio. This file contains memory radio and packet configuration and the appropriate

LUTs. See the ADF7030-1 Configuration File Format section for a detailed explanation of the configuration file format.Write/download the user settings to the ADF7030-1.

The contents of the ADF7030-1 configuration file are written to the ADF7030-1 in PHY\_OFF over the SPI. See the Host Initialization of ADF7030-1 SPI section for instructions on issuing a SPI command after a cold start or wakeup from sleep. See the Applying the ADF7030-1 Configuration section for a detailed explanation of how to interpret the configuration file and write it to the radio.

3. Apply the user settings.

The host microcontroller sends a CMD\_CFG\_DEV command. The radio returns to PHY\_OFF. See the Configuring section for more information.

# **MODIFYING CONFIGURATION AT RUN TIME**

Some radio and packet settings can be modified after the initial configuration step.

The ADF7030-1 settings can be subdivided into two categories, generated settings and run-time settings.

#### **Generated Settings**

These settings cannot be calculated by the user. They are generated by the ADF7030-1 design center and must not be overwritten by the user. Change these values only when a new, full configuration file is applied to the device. These private fields can be single or multiple bit fields in a register, marked as generated in the register map, or a full 32-bit register. Examples of a fully generated register include the PROFILE\_OCL\_CFG0 register.

## **Run-Time Settings**

Run-time settings can be changed after the initial configuration by the user.

These fields are documented and public. They include fields from the radio profile, such as channel frequency, which can be changed in PHY\_ON, for example, between an Rx and a Tx transfer. Another example is the power amplifier (PA) power and PA selection.

All packet configuration settings can be changed in PHY\_OFF and PHY\_ON, including, for example, the sync word and the payload length.

The interrupt source and pin output configuration can be reconfigured in PHY\_OFF and PHY\_ON, by changing, for example, the IRQ mask for IRQ\_OUT0 to enable an interrupt on the preamble found interrupt.

GPIO functionality can be altered by the user at run time, by enabling, for example, the transmit or receive clock, SPORT\_TRXCLK, on a selected pin. A CMD\_CFG\_DEV command is required for these changes to take effect.

The RTC period can also be changed, requiring a CMD\_CFG\_DEV command.

# **APPLYING THE ADF7030-1 CONFIGURATION FILE**

An ADF7030-1 configuration file is a standardized file format for representing memory writes to the ADF7030-1. The ADF7030-1 configuration file format is used to store and apply radio settings, packet settings, lookup tables, and packet payload data generated by the ADF7030-1 design center to the radio. Firmware modules, such as the OfflineCalibration.cfg firmware module, are also supplied as configuration files.

# **ADF7030-1 CONFIGURATION FILE FORMAT**

An ADF7030-1 configuration file is an ASCII text file. At the top of the file, a C99 ISO/IEC 9899:1999 standard compliant multilevel comment describes the content of the file and provides a version or time stamp.

There can be one or more blocks in an ADF7030-1 configuration file. A block represents a single SPI transaction and is formatted as a sequence of bytes separated by commas, that is, integers between 0 and 255, written in two-digit wide hexadecimal notation, for example, 0x2E. A block may be preceded by an additional C style comment. Each block starts with a framing header of three bytes, which contains the length of the block, including the length of the frame itself. The length header byte order is MSB first. For example, a block length of 300 bytes starts with a sequence of 0x00, 0x01, 0x2C, where 0x00012C is 300 in hexadecimal.

#### Table 14. ADF7030-1 Configuration File Block Format

| Length Header          | SPI Command Sequence |

|------------------------|----------------------|

| Three Bytes, MSB First | Sequence of Bytes    |

#### Table 15. Example of an ADF7030-1 Configuration File Block Format, Showing a Block Write to Address 0x2000060C

| Length Header                                                                               |                         | SF                                    | Pl Commands                                          |