# USB Type-C Port Controller with USB-PD

#### Description

The FUSB308B targets system designers looking to implement up to four USB Type-C port controllers (TCPC) with USB-PD capabilities.

This solution provides integrated Type–C Rev 1.3 detection circuitry enabling manual attach/detach detection. Time critical Power Delivery functionality is handled autonomously, offloading the  $\mu$ Processor or Type–C Port Manager (TCPM).

The FUSB308B complies with the USB–PD Interface Specification Rev 1.0 as a TCPC for a standardized interface with TCPM.

#### Features

- USB-PD Interface Specification Rev 1.0 Ver. 1.2 Compatible

- USB Type-C Rev 1.3 Compatible

- USB-PD Rev3.0 Ver. 1.2 Compatible

- Sink Transmit

- Extended Data Messages (Chunked)

- Dual–Role Functionality

- ◆ Manual Type-C Detection

- Automatic DRP Toggling

- USB-PD Interface Specification Support

- Automatic GoodCRC Packet Response

- Automatic Retries of Sending Packet

- All SOP\* Types Supported

- 2 VBUS Sources Control

- Integrated 3 W Capable VCONN to CCx Switch

- 10-bit VBUS ADC

- Programmable GPIOs

- 4 Selectable I<sup>2</sup>C Addresses

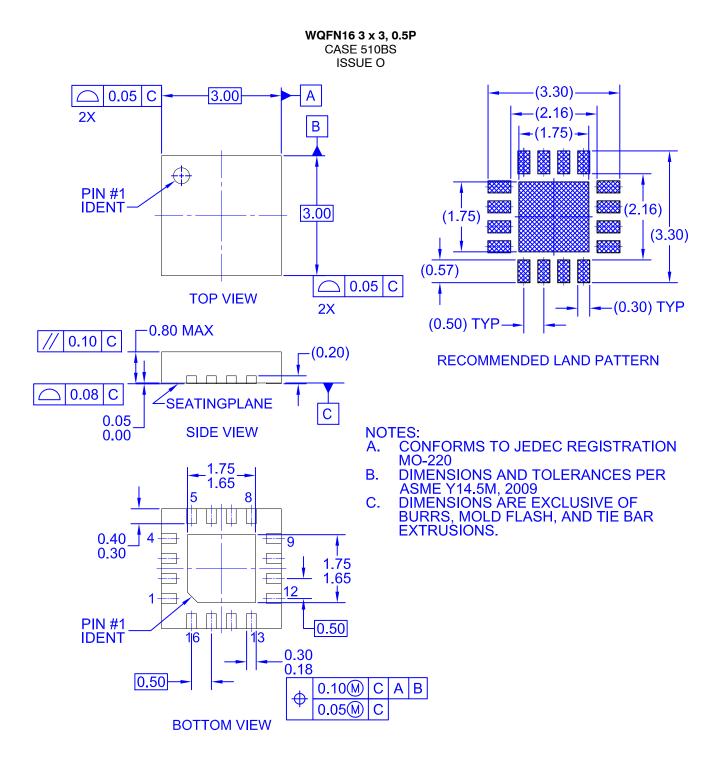

- Packaging: 16 Pin QFN

## Applications

- Desktops

- Wall Adapters

- Automotive

# **ON Semiconductor®**

#### www.onsemi.com

LL = Assembly Lot Code

#### **PIN ASSIGNMENT**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 3 of this data sheet.

1

| Table of Contents                                |   |

|--------------------------------------------------|---|

| Description                                      |   |

| Features                                         |   |

| Applications                                     |   |

| Typical Application                              | 3 |

| Block Diagram                                    | ŀ |

| Pin Configurations                               | ŀ |

| Pin Descriptions                                 | 5 |

| Power Up, Initialization and Reset               | 5 |

| Dead Battery Power–up                            | 5 |

| Programmable GPIOx                               | 5 |

| Standard Outputs                                 | 3 |

| I <sup>2</sup> C Interface                       | 3 |

| I <sup>2</sup> C Address Selection               | 3 |

| Interrupt Operation                              | 3 |

| I <sup>2</sup> C Idle Mode                       | 7 |

| VCONN Control                                    | 3 |

| Type–C Manual Mode Detection                     | 7 |

| BMC Power Delivery                               | 7 |

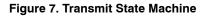

| Transmit State Machine                           | 3 |

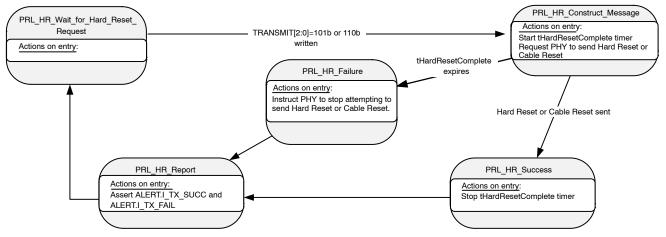

| Hard Reset/ Cable Reset State Machine            | ) |

| Automatic GoodCRC Response                       | ) |

| BIST Mode                                        |   |

| VBUS Source and Sink Control                     |   |

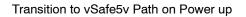

| Voltage Transitions                              |   |

| VBUS Monitoring and Measurement                  | 5 |

| VBUS Discharge                                   |   |

| Automatic Source Discharge after a Disconnect 15 | 5 |

| Automatic Sink Discharge after a Disconnect 15   | 5 |

| Watchdog Timer                                   | 3 |

| USB-PD Rev 3.0 Features                          | 7 |

| DC and Transient Characteristics                 | 3 |

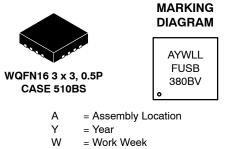

#### Table 1. ORDERING INFORMATION

| Part Number  | Top Marking   | Operating<br>Temperature Range | Package                                                            | Packing Method† |

|--------------|---------------|--------------------------------|--------------------------------------------------------------------|-----------------|

| FUSB308BVMPX | FUSB<br>308BV | Automotive<br>–40 to 105°C     | 16-Lead Molded Leadless Package<br>(QFN) JEDEC, ML220, 3 mm Square | Tape and Reel   |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

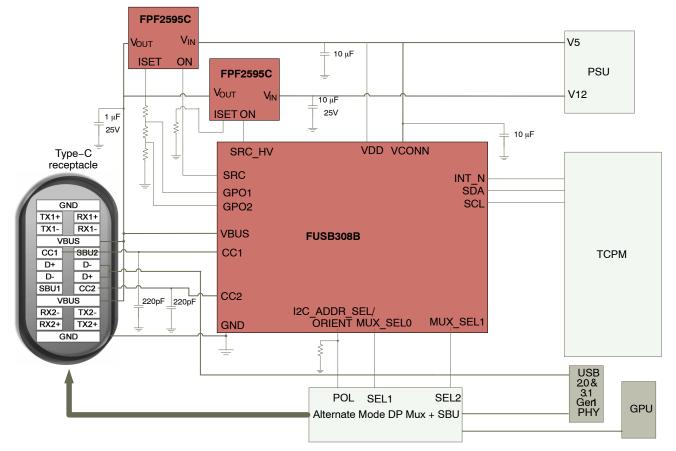

# **Typical Application**

Figure 1. FUSB308B Typical Typical Desktop Computing Application

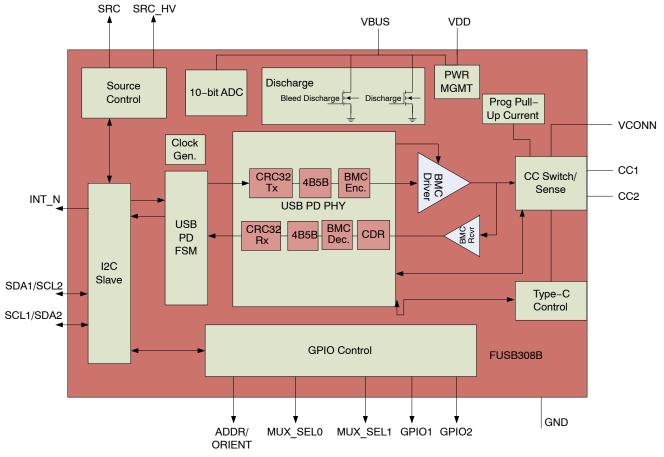

# **Block Diagram**

Figure 2. FUSB308B Block Diagram

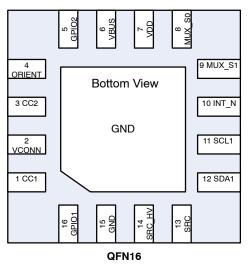

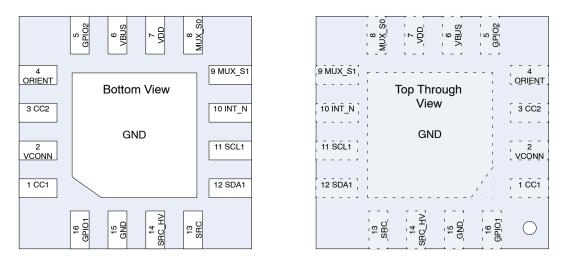

# Pin Configurations

Figure 3. Pin Assignment QFN (FUSB308B)

#### **Pin Descriptions**

#### Table 2. PIN DESCRIPTION

| Name                         | Туре                | Description                                                                                                                                                                                                                                                                                                                                        |

|------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB TYPE-C CONNECT           | OR INTERFACE        | •                                                                                                                                                                                                                                                                                                                                                  |

| CC1                          | I/O                 | Type-C connector Configuration Channel (CC) pins. Initially used to determine<br>when an attach has occurred and what the orientation of the insertion is. Function-<br>ality after attach depends on mode of operation detected.<br>Operating as a host:<br>- Sets the allowable charging current for VBUS to be sensed by the attached<br>device |

| CC2                          | I/O                 | <ul> <li>Used to communicate with devices using USB BMC Power Delivery</li> <li>Used to detect when a detach has occurred</li> <li>Operating as a device:</li> <li>Indicates what the allowable sink current is from the attached host</li> <li>Used to communicate with devices using USB BMC Power Delivery</li> </ul>                           |

| GND                          | Ground              | Ground                                                                                                                                                                                                                                                                                                                                             |

| VBUS                         | Power               | VBUS supply pin for attach and detach detection when operating as an upstream facing port (Device)                                                                                                                                                                                                                                                 |

| POWER INTERFACE              |                     |                                                                                                                                                                                                                                                                                                                                                    |

| VDD                          | Power               | Input supply voltage                                                                                                                                                                                                                                                                                                                               |

| GPIO2                        | 3-State CMOS I/O    | General Purpose I/O                                                                                                                                                                                                                                                                                                                                |

| VCONN                        | Power Switch        | Regulated input to be switched to correct CC pin as VCONN to power USB3.1 fully featured cables, powered accessories or dongles bridging Type C to other video or audio connectors                                                                                                                                                                 |

| SIGNAL INTERFACE             |                     |                                                                                                                                                                                                                                                                                                                                                    |

| SCL1/SDA2 (Note 1)           | Open-Drain I/O      | I <sup>2</sup> C serial clock/data signal to be connected to the I <sup>2</sup> C master                                                                                                                                                                                                                                                           |

| SDA1/SCL2 (Note 1)           | Open-Drain I/O      | I <sup>2</sup> C serial clock/data signal to be connected to the I <sup>2</sup> C master                                                                                                                                                                                                                                                           |

| INT_N                        | Open-Drain Output   | Active LOW open drain interrupt output used to prompt the processor to read the I <sup>2</sup> C register bits                                                                                                                                                                                                                                     |

| ORIENT/I2C_<br>ADDR (Note 1) | 3-State CMOS Output | Selects I <sup>2</sup> C Address on Power up and then becomes a General Purpose CMOS<br>Output                                                                                                                                                                                                                                                     |

| MUX_SEL0                     | 3-State CMOS Output | MUX Selection Output 0                                                                                                                                                                                                                                                                                                                             |

| MUX_SEL1                     | 3-State CMOS I/O    | MUX Selection Output 1                                                                                                                                                                                                                                                                                                                             |

| GPIO1                        | 3-State CMOS I/O    | General Purpose I/O                                                                                                                                                                                                                                                                                                                                |

| VBUS SOURCE INTERF           | ACE                 |                                                                                                                                                                                                                                                                                                                                                    |

| SRC_HV                       | CMOS Output         | Controls High Voltage Source Path Load Switch (Active High)                                                                                                                                                                                                                                                                                        |

|                              |                     |                                                                                                                                                                                                                                                                                                                                                    |

| SRC_HV | CMOS Output | Controls High Voltage Source Path Load Switch (Active High)     |  |  |

|--------|-------------|-----------------------------------------------------------------|--|--|

| SRC    | CMOS Output | Controls external VBUS Source Load Switch on/off. (Active High) |  |  |

|        |             |                                                                 |  |  |

1. A different I2C address is used depending on which SDA and SCL are used and the state of ORIENT/I2C\_ADDR at power up.

#### Power Up, Initialization and Reset

When power is first applied to VDD or VBUS, the FUSB308B goes through its POR sequence to load up all the default values in the register map, read all the fuses so that the trimmed values are available when VDD or VBUS is in its valid range. A software reset can be executed by writing SW\_RES to 1 in RESET Register.

This executes a full reset of the FUSB308B similar to POR where all the I2C registers go to their default state.

When powered down, the FUSB308B will present an Open on both CC lines.

The FUSB308B will present Rp, ROLECTRL= 0x05 when VDD is present

#### **Programmable GPIOx**

The FUSB308B has two programmable GPIOs. These can be programmed to be Inputs, CMOS Outputs or Open Drain Outputs. To configure them, the TCPM writes to GPIO1\_CFG and GPIO2\_CFG. If the GPIO is configured as an input, its logic value can be read in GPIO\_STAT and ALERT\_VD registers.

## **Standard Outputs**

The FUSB308B implements the Orientation and DP Mux Selection Standard Outputs as indicated in STD OUT CAP register.

To configure the Orientation, and Mux selection, the TCPM writes to STD OUT CFG.

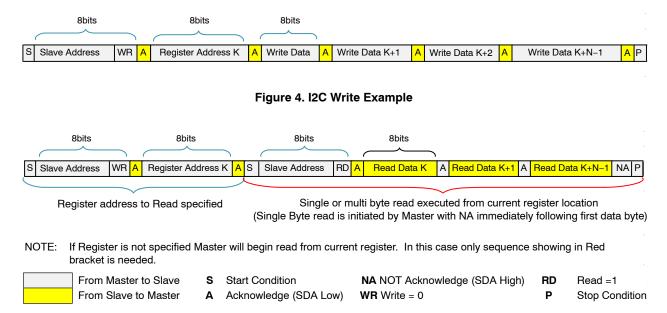

## I<sup>2</sup>C Interface

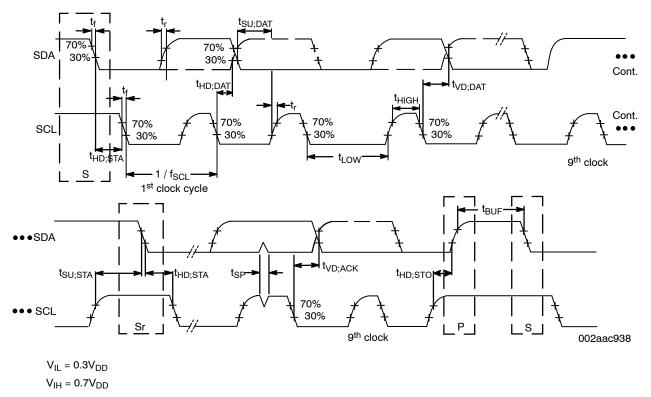

The FUSB308B includes a full I<sup>2</sup>C slave controller. The I2C slave fully complies with the I2C specification version 6 requirements. This block is designed for fast mode plus signals.

Examples of an I<sup>2</sup>C write and read sequence are shown in Figure 4 and Figure 5 respectively.

#### Figure 5. I2C Read Example

#### I<sup>2</sup>C Address Selection

I2C Slave addresses can be changed by configuring the I2C ADDR GPO input on power up with a pull-up or pull-down resistor and routing the SCL and SDA lines according to Table 3.

#### Interrupt Operation

The INT N pin is an active low, open drain output which indicates to the host processor that an interrupt has occurred in the FUSB308B which needs attention. The INT\_N pin is asserted after power-up or device reset RESET.SW RES

set to 1b (due to ALERTL.I PORT PWR PWRSTAT.TCPC INIT). When an interruptible event occurs, INT N is driven low

and

and is high-Z again when the processor clears the interrupt by writing a 1 to the corresponding interrupt bit position. Writing a 0 to an interrupt bit has no effect.

A processor firmware has additional control of INT N through individual event mask bits which can be set or cleared to enable or disable INT N from being driven low when each event occurs.

|          |           |       | Slave Address |       |       |       |       |       |       |

|----------|-----------|-------|---------------|-------|-------|-------|-------|-------|-------|

| I2C_ADDR | SCLx/SDAx | Bit 7 | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 0        | SCL1/SDA1 | 1     | 0             | 1     | 0     | 0     | 0     | 0     | R/W   |

| 1        | SCL1/SDA1 | 1     | 0             | 1     | 0     | 0     | 0     | 1     | R/W   |

| 0        | SCL2/SDA2 | 1     | 0             | 1     | 0     | 0     | 1     | 0     | R/W   |

| 1        | SCL2/SDA2 | 1     | 0             | 1     | 0     | 0     | 1     | 1     | R/W   |

#### Table 3, I<sup>2</sup>C ADDRESSES

## I<sup>2</sup>C Idle Mode

#### Entering I<sup>2</sup>C Idle Mode

The FUSB308B does not need to enter I<sup>2</sup>C Idle Mode in order to save power. Entering this mode has no effect on I<sup>2</sup>C function. The FUSB308B can enter idle mode if 0xFF is written to the COMMAND register. Once in Idle mode, the FUSB308B will not set the PWRSTAT.TCPC\_INIT to one.

#### Exiting I<sup>2</sup>C Idle Mode

The FUSB308B will exit I<sup>2</sup>C Idle mode when any I<sup>2</sup>C communication is addressed to the slave. The ALERTL.I\_PRT\_PWR interrupt will be set and no PWRSTAT bits will be set.

The device's I<sup>2</sup>C block is always on without power penalties.

## **VCONN Control**

The FUSB308B integrates a CCx to VCONN switch with programmable OCP capability via the VCONN\_OCP register. If PWRCTRL.VCONN\_PWR is set to 0, the standard VCONN current limit is used (210.5 mA). If PWRCTRL.VCONN\_PWR is set to 1, the programmable VCONN\_OCP is used.

The VCONN switch can be enabled via the PWRCTRL register bits EN\_VCONN and TCPC\_CTRL.ORIENT bits (for CC1/2 selection).

A VCONN valid voltage is monitored and reported on PWRSTAT.VCONN\_VAL. The valid voltage threshold is fixed at 2.4 V.

## Type-C Manual Mode Detection

The CC pull up (Rp) or pull down (Rd) resistors and DRP toggle are setup via the ROLECTRL register. If a TCPM wishes to control Rp/Rd directly, it can write ROLECTRL.DRP = 0b and the desired ROLECTRL bits [3:0] (CC1/CC2).

The FUSB308B can autonomously toggle the Rp/Rd by setting ROLECTRL.DRP = 1b and the starting value of Rp/Rd in ROLECTRL.bits [3:0]. DRP toggling starts by writing to the COMMAND register

If ROLECTRL.DRP = 1b, the only allowed values for CC1/CC2 in ROLECTRL bits [3:0] are Rp/Rp or Rd/Rd.

When ROLECTRL bits 3:0 are set to Open and ROLECTRL.DRP = 0b, the PHY and CC comparators are powered down.

The FUSB308B updates the CCSTAT register on a Connect, Disconnect, a change in ROLECTRL.DRP or a change (tTCPCFilter debounced) on the CC1 or CC2 wire.

The TCPM reads CCSTAT upon detecting an interrupt and seeing the ALERTL.I\_CCSTAT = 1. The FUSB308B indicates the DRP status, the DRP result, and the current CC status in this register.

The FUSB308B will set CCSTAT.LOOK4CON = 0b when it has stopped toggling as a DRP.

The TCPM reads the CCSTAT.LOOK4CON to determine if the FUSB308B is toggling Rp/Rd when operating as a DRP, it then reads CCSTAT.CON\_RES to determine if the FUSB308B is presenting an Rp or Rd and read the CCSTAT.CC1\_STAT and CCSTAT.CC2\_STAT to determine the CC1 and CC2 states.

The FUSB308B debounces the CC lines for tTCPCfilter before reporting the status on CCSTAT. The TCPM must complete the debounce as defined in Type–C Specification.

## **BMC Power Delivery**

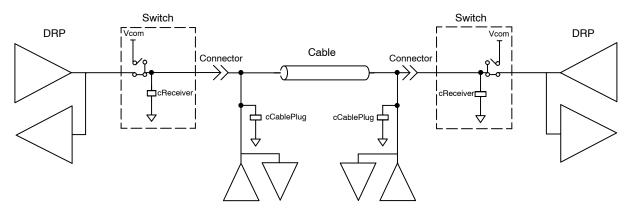

The Type–C connector allows USB Power Delivery (PD) to be communicated over the connected CC pin between two ports. The communication method is the BMC Power Delivery protocol and is used for many different reasons with the Type–C connector. Possible uses are outlined below.

- Negotiating and controlling charging power levels

- Alternative Interfaces such as MHL, Display Port

- Vendor specific interfaces for use with custom docks or accessories

- Role swap for dual-role ports that want to switch who is the host or device

- Communication with USB3.1 full featured cables

The FUSB308B integrates a thin BMC PD client which includes the BMC physical layer and packet buffers which allows packets to be sent and received by the host software through  $I^2C$  accesses.

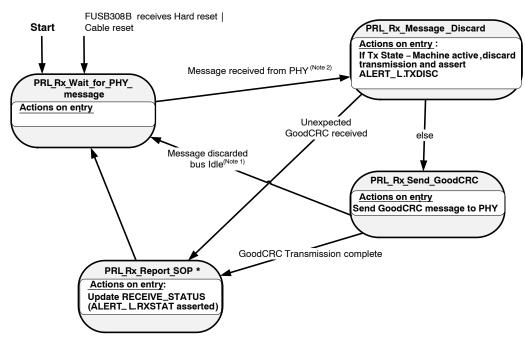

#### **Receive State Machine**

The TCPM can setup the desired types of messages to be received by the FUSB308B via the RXDETECT register. This register defaults to 0x00 (Receiver disabled) upon power up, reset, Hard Reset transmission and reception, and upon detecting a cable disconnect. A message is not received unless it is first enabled. Figure 6 shows the FUSB308B receive state machine.

Upon a successfully transmitting GoodCRC, the RXSTAT register is updated with the type of message received and the TCPM is alerted via ALERTL.I\_RXSTAT bit (see transition from PRL\_Rx\_Send\_GoodCRC to PRL\_Rx\_Report\_SOP\* in Figure 6). The total number of bytes in the receive buffer RXDATA is stored in RXBYTECNT This number includes the header bytes that are stored in RXHEADL and RXHEADH and the RXSTAT register.

The RXBYTECNT, RXSTAT registers and the internal receive buffer will be cleared after the ALERTL.I\_RXSTAT bit is cleared.

The FUSB308B will automatically transmit a GoodCRC message for valid enabled messages within tTransmit.

A received message is valid when:

- It is not a GoodCRC message

- The calculated CRC is correct

- The SOP\* type is enabled

The makeup of the GoodCRC message is formed by the received SOP\* type and the contents of MSGHEADR register.

When an expected GoodCRC message or a Hard Reset signaling is received, they will not be replied with a

GoodCRC message (see Note 2 in Figure 6). If a GoodCRC message received was not expected due to the SOP\* type or mismatched Message ID, the receive state machine will not send a GoodCRC message and will transition to PRL\_Rx\_Report SOP\* to inform the TCPM.

If a Hard Reset message is received, the FUSB308B will reset the RXDETECT preventing the reception of future messages until the TCPM re-enables it.

- 2. This indication is sent by the PHY when a message has been discarded due to CC being busy, and after CC becomes idle again (see USB PD Spec).

- Messages do not include Hard Reset or Cable Reset signals or expected GoodCRC messages (GoodCRC messages are only expected after the FUSB308B PHY has received the tx message and the FUSB308B Tx state-machine is in the PRL\_Tx\_Wait\_for\_PHY\_response state).

#### Figure 6. Receive State Machine

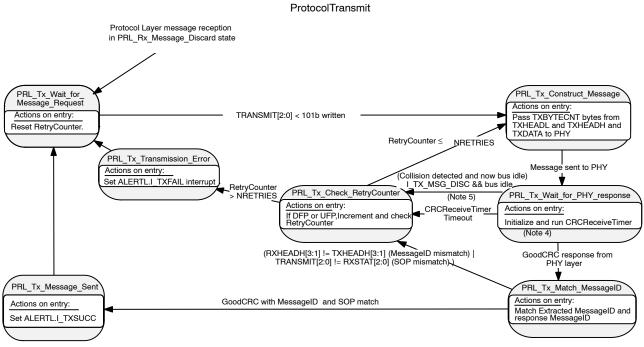

#### **Transmit State Machine**

To transmit a message, the TCPM must first write the entire message in the following registers: TXHEADL, TXHEADH, TXBYTECNT and the TXDATA.

The actual transmission starts when the TCPM writes the TRANSMIT register.

The TRANSMIT register is where the message selection is done and it must be written once per transmission.

The TRANSMIT and TXBYTECNT will be reset after executing a successful or failed transmission.

If the TRANSMIT.RETRY\_CNT is set to a number greater than 0, the FUSB308B will automatically retry sending the same message if a GoodCRC is not received

within tCRCReceiveTimer. An automatic retry is not performed when sending Hard–Resets, Cable–Resets, or BIST Carrier Mode 2 signaling.

The TCPM must not write the TRANSMIT register again until ALERTL.I\_TXSUCC, I\_TXFAIL, I\_TX\_DISC have been asserted and cleared.

The TCPM will not write the TRANSMIT register to request a transmission other than a Hard reset until it has cleared all received message alerts. If a TRANSMIT is written when ALERTL.I\_RXSTAT = 1 or ALERTL. I\_RXHRDRST = 1, the transmit request is discarded and ALERTL.I\_TX\_DISC is asserted.

- 4. The CRCReceiveTimer is only started after the FUSB305 has sent the message. If the message is not sent due to a busy channel then the CRCReceiveTimer will not be started.

- 5. This Indication is sent by the PHY layer when a message has been discarded due to CC being busy, and after CC becomes idle again. The CRCReceiveTimer is not running in this case since no message has been sent.

### Hard Reset/ Cable Reset State Machine

The TCPM will write the TRANSMIT register to initiate the Hard Reset/Cable Reset state machine, see Figure 8. If a the FUSB308B is in the middle of a transmission when instructed to send a Hard or Cable reset, it will set the ALERTL.I\_TXDISC bit and send the hard reset signaling as soon as possible. The FUSB308B implements the HardResetCompleteTimer. A Hard Reset or Cable Reset will be attempted until the HardResetCompleteTimer times out. After a successful transmission or timeout, the FUSB308B will indicate that a Hard Reset or Cable Reset has been sent by asserting both ALERTL.I\_TXSUCC and ALERTL.I\_TXFAIL registers simultaneously. The bits in RXDETECT and RXBYTECNT will be reset to disable PD message passing after a Hard Reset is received or transmitted.

Figure 8. Hard Reset and Cable Reset State Machine

#### Automatic GoodCRC Response

Power Delivery packets require a GoodCRC acknowledge packet to be sent for each received packet where the calculated CRC is the correct value. This calculation is done by the FUSB308B.

The FUSB308B will automatically send the GoodCRC control packet in response to alleviate the local processor from responding quickly to the received packet. Once the GoodCRC packet is sent the FUSB308B will trigger the ALERTL.I\_RXSTAT interrupt.

The following sequence of events occur internally within the FUSB308B without processor intervention when it is determined that the receive message has the correct CRC. If the host processor attempts a packet transmission during an Automatic GoodCRC response, the FUSB308B will set the ALERTL.I\_TXDISC bit interrupting the processor. The processor should only transmit a new packet once ALERTL.I\_TXSUCC or ALERTL.I\_TX\_FAIL has been received.

It is assumed that the processor will set the PWRCTRL.ORIENT to specify which channel USB-PD traffic will be transmitted or received.

#### **BIST Mode**

#### **Bist Transmit**

The FUSB308B will transmit Bist Carrier Mode 2 signaling when directed by the TCPM via TRANSMIT

register. The FUSB308B will exit Bist Mode after tBISTContMode timer expires.

#### **Bist Receive**

When the FUSB308B is in Bist receive mode via TCPC\_CTRL register, it will acknowledge these packets with a GoodCRC and automatically flush the buffer to allow for thousands of packets to be received without filling the receive buffer. Bist Receive mode will exit on a cable disconnect or a Hard Reset received.

#### **VBUS Source Control**

The FUSB308B has two source path controls (SRC and SRC\_HV). The secondary Source path control will be used to provide higher voltages on VBUS after a PD contract has been established. The primary source path is used for sourcing vsafe5V only.

The TCPM will initiate the transition from SRC to SRC\_HV by writing 1000\_1000b to the COMMAND register. The FUSB308B will enable SRC\_HV and then disable the SRC I/O.

When transitioning from a high voltage source to vsafe5V, the TCPM will write 0111\_0111b to the COMMAND register.

# **Voltage Transitions**

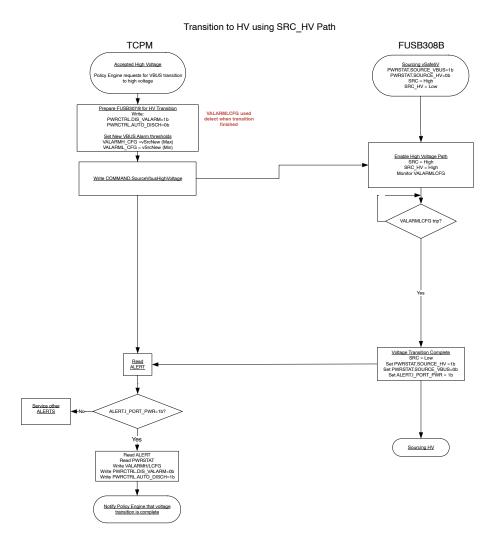

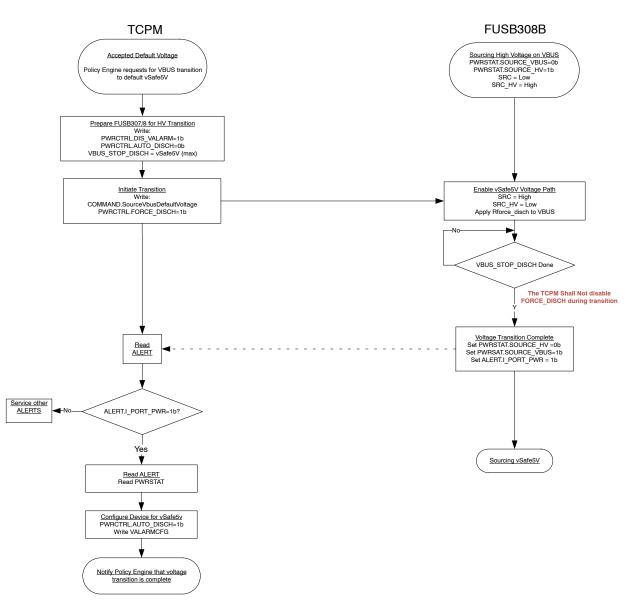

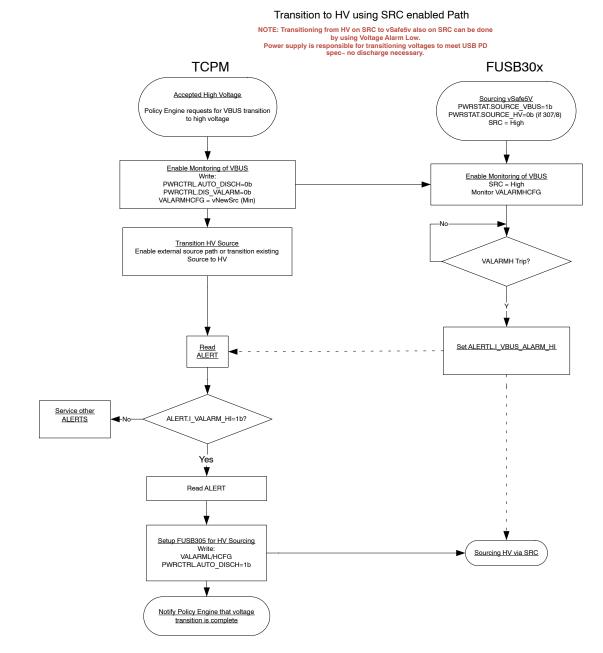

The FUSB308B has two source control ports: SRC and SRC\_HV. There are two ways to transition between SRC and SRC\_HV as seen in Figure 9 through Figure 12.

Figure 9. Transition to vSafe5V on Power Up

Figure 10. Transition to High Voltage Sourcing using SRC\_HV Controlled Path (FUSB308B)

Transition to vSafe5V using SRC\_HV Path

Figure 11. Transition to vSafe5V from SRC\_HV Controlled Path (FUSB308B)

Figure 12. Transition to High Voltage using SRC Controlled Path VBUS

#### **VBUS Monitoring and Measurement**

The FUSB308B can monitor the presence of VBUS and will report it on PWRSTAT.VBUS\_VAL and interrupt ALERT.I PORT PWR.

VBUS\_VAL is set according to VBUS thresholds in *vVBUSthr*.

The FUSB308B also supports a more precise voltage measurement via an on-board ADC. The voltage on VBUS is measured at a rate of tVBUSsample and it is reported on VBUS\_VOLTAGE\_L/H register. The precision of the measurement is +/2% with a resolution of 25 mV LSB.

In addition to providing the  $\mu$ Processor an accurate measurement of VBUS, the measurement in VBUS\_VOLTAGE will be used when monitoring various user defined thresholds:

- Voltage alarms in registers VALARMLCFG and VALARMHCFG

- VBUS Disconnect Threshold in registers VBUS\_SNK\_DISC and VBUS\_SNK\_DISC

- VBUS Stop Discharge Threshold in registers VBUS\_STOP\_DISC and VBUS\_STOP\_DISC

The FUSB308B implements Low and High VBUS Voltage Alarms that can be programmable via VALARMLCFG and VALARMHCFGL respectively. If the High or the Low thresholds are crossed, the FUSB308B will signal an interrupt on ALERTL.I\_VBUS\_ALRM\_HI or ALERTH.I\_VBUS\_ALRM\_LO respectively. These alarms can be disabled by writing PWRCTRL.DIS\_VALARM to one.

ALERTL.I\_PORT\_PWR is asserted if the bit-wise AND of PWRSTAT and PWRSTAMSK results in any bits that have the value 1.

## VBUS Discharge

#### Manual Discharge

There are two types of manual discharge circuits implemented: A bleed discharge for low current and a force discharge. The bleed discharge can be manually enabled by register bit writing а one to PWRCTRL.EN BLEED DISCH. When enabled, the bleed discharge provides a low current load on VBUS of 7 KW (max.) via RBLEED. The force discharge is used to quickly discharge VBUS to vSafe0V by applying a dynamic load to VBUS via RFULL\_DISCH. The force discharge can be manually enabled by writing a one to register bit PWRCTRL.FORCE\_DISCH. When RFULL\_DISCH is applied, the maximum slew rate allowed for discharging VBUS does not exceed vSrcSlewNeg 30 mV/µs as it is specified in the USB-PD spec.

Automatic discharge bit PWRCTRL. AUTO\_DISCH must be disabled before enabling force discharge.

#### Automatic Source Discharge after a Disconnect

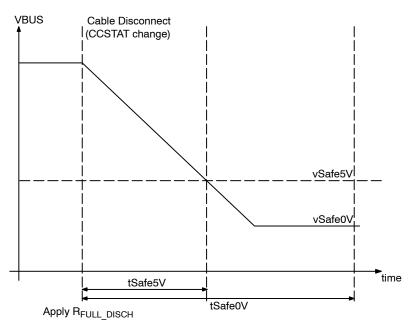

Automatic discharge can be enabled by setting PWRCTRL. AUTO\_DISC register bit. When in Source mode the FUSB308B will fully discharge VBUS to vSafe5V (max.) within tSafe5V and to vSafe0V within tSafe0V when a Disconnect occurs. The FUSB308B is in Source mode when the SRC output is asserted.

The FUSB308B in Source mode will detect a Disconnect if the CCSTAT.CCx\_STAT field for the monitored CC pin indicates SRC.Open and enable the FULL Discharge pull-down device. The monitored CC pin is specified by TCPC\_CTRL.ORIENT.

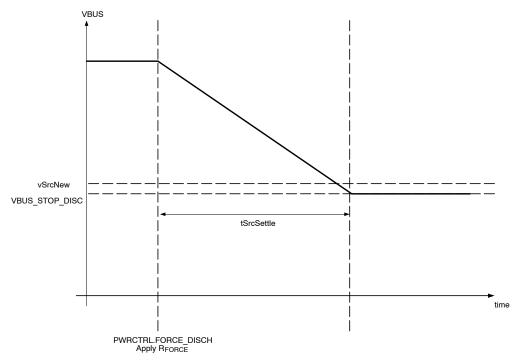

Figure 13. VBUS Auto Discharge as Source

### **Discharge during a Connection**

The discharge functions can be manually activated via the PWRCTRL.FORCE\_DISCH register. The discharge

pull-down is specified by  $R_{FULL\_DISCH}$ . The FUSB308B will automatically disable discharge when VBUS reaches VBUS\_STOP\_DISC threshold.

Figure 14. Source Discharge During a Connection

#### Watchdog Timer

The watchdog timer functionality is enabled whenever TCPC\_CTRL.EN\_WATCHDOG is set to 1b. The watchdog timer should only be enabled after an attach when the device is in Attached.Src, Attached.Snk or Apply.ROLECONTROL states. The watchdog timer starts when any of the interrupts that are not masked in the Alert register are set or when the INTB pin is asserted. The watchdog timer is cleared on an I2C access by the TCPM (either read or write). If the INTB pin is still asserted after this I2C access, the watchdog timer will reinitialize and start monitoring again until all of the Alerts are cleared or until the INTB pin is de-asserted.

When the watchdog timer expires, the FUSB308B will immediately disconnect the CC terminations by setting ROLE\_CONTROL bits 3..0 to 1111b, disable all SRC/SRC\_HV or SNK outputs, discharge VBUS to vSafe0V, and set FAULT\_STATUS.I2CInterfaceError.

#### **USB-PD Rev 3.0 Features**

#### **Extended Data Messages**

Extended Data Messages is only supported via Chunking where large messages are broken into 2 or more 26 byte chunks.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Para                                       | ameter                     | Min  | Мах  | Unit |

|-----------------------------------|--------------------------------------------|----------------------------|------|------|------|

| V <sub>DDAMR</sub>                | Supply Voltage from VDD                    | -0.5                       | 6.0  | V    |      |

| V <sub>CC_HDDRP</sub><br>(Note 6) | CC pins when configured as Ho              | -0.5                       | 6.0  | V    |      |

| V <sub>VBUS</sub>                 | VBUS Supply Voltage                        | -0.5                       | 28.0 | V    |      |

| T <sub>STORAGE</sub>              | Storage Temperature Range                  | -65                        | +150 | С    |      |

| TJ                                | Maximum Junction Temperature               | 9                          |      | +150 | С    |

| ΤL                                | Lead Temperature (Soldering, 1             | 0 seconds)                 |      | +260 | С    |

| ESD                               | Human Body Model, JEDEC                    | Connector Pins (VBUS, CCx) | 4    |      | kV   |

|                                   | JESD22-A114                                | Others                     | 2    |      | kV   |

|                                   | Charged Device Model,<br>JEDEC LESD22-C101 | All Pins                   | 1    |      | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 6. As host, device drives CC, VConn.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol            | Parameter                       | Min          | Тур | Max  | Unit |

|-------------------|---------------------------------|--------------|-----|------|------|

| V <sub>BUS</sub>  | VBUS Supply Voltage (Note 7)    | 4.0          | 5.0 | 21.5 | V    |

| V <sub>DD</sub>   | VDD Supply Voltage              | 2.8 (Note 8) | 3.3 | 5.5  | V    |

| V <sub>CONN</sub> | VCONN Supply Voltage (Note 9)   | 2.7          |     | 5.5  | V    |

| ICONN             | VCONN Supply Current            |              |     | 560  | mA   |

| T <sub>A</sub>    | Operating Temperature           | -40          |     | +85  | С    |

| T <sub>A</sub>    | Operating Temperature (Note 10) | -40          |     | +105 | С    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

7. 20 V PD + 5% Tolerance per spec + 0.5 V Load Transition.

8. This is for functional operation only and isn't the lowest limit for all subsequent electrical specifications below. All electrical parameters have a minimum of 3 V operation.

9. For powered accessories Vconn minimum is 2.7 V.

10. Automotive part only, FUSB308BVMPX.

## **DC and Transient Characteristics**

Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25^{\circ}C$  and  $V_{DD} = 3.3 V$  unless otherwise specified.

#### **CURRENT CONSUMPTION**

|          |                                   |     | T <sub>A</sub> = -40 to +85°C<br>T <sub>A</sub> = -40 to +105°C (Note 15)<br>T <sub>J</sub> = -40 to +125°C |     |      |  |  |

|----------|-----------------------------------|-----|-------------------------------------------------------------------------------------------------------------|-----|------|--|--|

| Symbol   | Parameter                         | Min | Тур                                                                                                         | Max | Unit |  |  |

| IDISABLE | Disable Current (ROLECTRL = 0x0F) |     |                                                                                                             | 10  | μA   |  |  |

|          | Unattached DRP or Source          |     | 7                                                                                                           | 20  | μA   |  |  |

|          | Attached as Source (No PD)        |     | 12                                                                                                          | 22  | μA   |  |  |

#### BASEBAND PD

|        |               | T <sub>A</sub> = -40 to +85°C<br>T <sub>A</sub> = -40 to +105°C (Note 15)<br>T <sub>J</sub> = -40 to +125°C |      |      |      |

|--------|---------------|-------------------------------------------------------------------------------------------------------------|------|------|------|

| Symbol | Parameter     | Min                                                                                                         | Тур  | Мах  | Unit |

| UI     | Unit Interval | 3.03                                                                                                        | 3.33 | 3.70 | μs   |

## TRANSMITTER

| zDriver        | TX output impedance at 750 kHz with an external 220 pF or equivalent load                                | 33  | 75  | Ω  |

|----------------|----------------------------------------------------------------------------------------------------------|-----|-----|----|

| tEndDriveBMC   | Time to cease driving the line after the end of the last bit of the Frame                                |     | 2   | UI |

| tHoldLowBMC    | Time to cease driving the line after the final high-to-low transition                                    | 1   |     | μs |

| tStartDrive    | Time before the start of the first bit of the preamble when the transmitter shall start driving the line | -1  | 1   | μs |

| tBISTContMode  | Time a BIST Carrier Mode 2 transmission is performed                                                     | 30  | 60  | ms |

| tBUFFER2CC     | Time from I2C Stop from writing to TRANSMIT register to<br>first bit of Preamble transmitted             |     | 195 | μs |

| t <sub>R</sub> | Rise Time                                                                                                | 300 |     | ns |

| t <sub>F</sub> | Fall Time                                                                                                | 300 |     | ns |

RECEIVER

| CReceiver (Note 11) | Receiver capacitance when driver isn't turned on     |     | 25 |    | pF    |

|---------------------|------------------------------------------------------|-----|----|----|-------|

| zBmcRx              | Receiver Input Impedance                             | 1   |    |    | MΩ    |

| tCC2BUFFER          | Time between last bit of EOP to I_RXSTAT             |     |    | 50 | μs    |

| tRxFilter           | Rx bandwidth limiting filter (Note 11)               | 100 |    |    | ns    |

| nTransitionCount    | Transitions count in a time window of 20 $\mu s$ max | 3   |    |    | Edges |

| tTransitionWindow   | Time window for detecting non-idle                   | 12  |    | 20 | μs    |

11. Guaranteed by characterization and/or design. Not production tested.

Figure 15. Transmitter Test Load

#### **USB-PD R3.0 SPECIFIC PARAMETERS**

|                |                                                                                                 | $T_A = -40 \text{ to } +85^{\circ}\text{C}$<br>$T_A = -40 \text{ to } +105^{\circ}\text{C} \text{ (Note 15)}$<br>$T_J = -40 \text{ to } +125^{\circ}\text{C}$ |     |      |    |  |  |

|----------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----|--|--|

| Symbol         | Parameter                                                                                       | Min Typ Max                                                                                                                                                   |     | Unit |    |  |  |

| TRANSMITTER    |                                                                                                 |                                                                                                                                                               |     |      |    |  |  |

| rFRSwapTx      | Fast Role Swap request transmit driver resistance Measured from $V_{CCx}$ = 0 to vFRSwapCableTx |                                                                                                                                                               |     | 5    | Ω  |  |  |

| tFRSwapTx      | Fast Role Swap request transmit duration                                                        | 60                                                                                                                                                            |     | 120  | μs |  |  |

| RECEIVER       |                                                                                                 |                                                                                                                                                               |     |      |    |  |  |

| tFRSwapRx      | Fast Role Swap request detection time                                                           | 30                                                                                                                                                            |     | 50   | μs |  |  |

| vFRSwapCableTx | Fast Role Swap request voltage detection threshold                                              | 490                                                                                                                                                           | 520 | 550  | mV |  |  |

#### **TYPE C SPECIFIC PARAMETERS**

|                        |                                                                                                                               | T <sub>A</sub> :<br>T <sub>A</sub> = -40<br>T <sub>J</sub> = |      |      |      |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|

| Symbol                 | Parameter                                                                                                                     | Min                                                          | Тур  | Max  | Unit |

| R <sub>SW_CCx</sub>    | R <sub>DSON</sub> for VCONN to CC1 or VCONN to CC2                                                                            |                                                              | 0.4  | 1.0  | Ω    |

| lsw_ccx                | Over Current Protection (OCP) limit at which VCONN switch<br>shuts off over the entire VCONN voltage range<br>VCONN_OCP = 0Fh | 600                                                          | 800  | 1000 | mA   |

| t <sub>SoftStart</sub> | Time taken for the VCONN switch to turn on during which Over-<br>Current Protection is disabled                               |                                                              | 1.5  |      | ms   |

| I <sub>80_CCX</sub>    | DFP 80 µA CC Current (Default) ROLECTRL = 05h                                                                                 | 64                                                           | 80   | 96   | μA   |

| I <sub>180_CCX</sub>   | DFP 180 μA CC Current (1.5 A) ROLECTRL = 15h                                                                                  | 166                                                          | 180  | 194  | μA   |

| I <sub>330_CCX</sub>   | DFP 330 µA CC Current (3 A) ROLECTRL = 25h                                                                                    | 304                                                          | 330  | 356  | μA   |

| R <sub>DEVICE</sub>    | Device pull-down resistance (Note 12)                                                                                         | 4.6                                                          | 5.1  | 5.6  | kΩ   |

| Ra                     | Powered Accessory Termination                                                                                                 | 800                                                          |      | 1200 | Ω    |

| vRa-SRCdef             | Ra Detection Threshold for CC Pin for Source for Default Current on VBUS                                                      | 0.15                                                         | 0.20 | 0.25 | V    |

| vRa-SRC1.5A            | Ra Detection Threshold for CC Pin for Source for 1.5 A Current on VBUS                                                        | 0.35                                                         | 0.40 | 0.45 | V    |

| vRa-SRC3A              | Ra Detection Threshold for CC Pin for Source for 3 A<br>Current on VBUS                                                       | 0.75                                                         | 0.80 | 0.85 | V    |

#### TYPE C SPECIFIC PARAMETERS (continued)

| Symbol          | Para                                                               | Min                     | Тур  | Max  | Unit |    |

|-----------------|--------------------------------------------------------------------|-------------------------|------|------|------|----|

| vRd-SRCdef      | Rd Detection Threshold for Sour<br>(HOST_CUR1/0 = 01)              | rce for Default Current | 1.50 | 1.60 | 1.65 | V  |

| vRd-SRC1.5A     | Rd Detection Threshold for Sour<br>(HOST_CUR1/0 = 10)              | rce for 1.5 A Current   | 1.50 | 1.60 | 1.65 | V  |

| vRd-SRC3A       | Rd Detection Threshold for Sour<br>(HOST_CUR1/0 = 11)              | 2.45                    | 2.60 | 2.75 | V    |    |

| vRa-SNK         | Ra Detection Threshold for CC I                                    | 0.15                    | 0.20 | 0.25 | V    |    |

| vRd-def         | Rd Default Current Detection Th                                    | 0.61                    | 0.66 | 0.70 | V    |    |

| vRd-1.5A        | Rd 1.5 A Current Detection Thre                                    | 1.16                    | 1.23 | 1.31 | V    |    |

| vRd-3.0A        | Rd 3 A Current Detection Thresh                                    | 2.04                    | 2.11 | 2.18 | V    |    |

| zOPEN           | CC resistance for disabled state                                   | 126                     |      |      | kΩ   |    |

| vVCONNthr       | Valid VCONN Voltage<br>Assumes PWRCTRL.EN_VCON                     |                         |      | 2.4  | V    |    |

| tTCPCfilter     | Debounce time on CC lines to p<br>of minor changes in voltage on ( |                         | 4    |      | 500  | μs |

| tCCDebounce     | Debounce Time for CC Attach D                                      | Detection               | 100  | 150  | 200  | ms |

| tSetReg         | Time between CC status change updated                              | e and I2C registers     |      |      | 50   | μs |

| tTCPCSampleRate | CC Sample rate for indicating ch                                   | nanges on CC lines      |      |      | 1    | ms |

| tDRP            | Sum of tToggleSrc and tToggleS                                     | nk timers               | 50   |      | 100  | ms |

| tToggleSrc      | Time Spent in Apply Rp before                                      | DRPTOGGLE = 00          | 15   |      | 30   | ms |

|                 | transitioning to Apply Rd                                          | DRPTOGGLE = 01          | 20   |      | 40   | ms |

|                 |                                                                    | DRPTOGGLE = 10          | 25   |      | 50   | ms |

|                 |                                                                    | DRPTOGGLE = 11          | 30   |      | 60   | ms |

| tToggleSnk      | Time Spent in Apply Rd before                                      | DRPTOGGLE = 00          | 35   |      | 70   | ms |

|                 | transitioning to Apply Rp                                          | DRPTOGGLE = 01          | 30   |      | 60   | ms |

|                 |                                                                    | DRPTOGGLE = 10          | 25   |      | 50   | ms |

|                 |                                                                    | DRPTOGGLE = 11          | 20   |      | 40   | ms |

12. RDEVICE minimum and maximum specifications are only guaranteed when power is applied.

### **VBUS MEASUREMENT CHARACTERISTICS**

|               |                                                                                    |                                                     | $T_A = -40$ | = -40 to +85<br>to +105°C (<br>= -40 to +12 | Note 15) |    |

|---------------|------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|---------------------------------------------|----------|----|

| Symbol        | Parameter                                                                          | Min                                                 | Тур         | Мах                                         | Unit     |    |

| vMDACstepVBUS | VBUS Measure block LSB reported on VB register                                     |                                                     | 25          |                                             | mV       |    |

| pMDACVBUS     | Accuracy of VBUS Voltage Measurement                                               | S Voltage Measurement $T_A = -40$ to $+85^{\circ}C$ |             |                                             | ±2       | %  |

|               |                                                                                    | T <sub>A</sub> = +85 to +105°C<br>(Note 12)         |             |                                             | ±5       | %  |

| tVBUSsample   | Sampling period of VBUS Measurement                                                |                                                     |             | 3                                           |          | ms |

| vVBUSthr      | VBUS threshold at which VBUS_VAL inter<br>Assumes VBUS present detection is enable | 3.5                                                 |             | 4.05                                        | V        |    |

| vVBUShys      | Hysteresis on VBUS Comparator                                                      |                                                     |             | 50                                          |          | mV |

#### VBUS MEASUREMENT CHARACTERISTICS (continued)

|            |                                                                                           | T <sub>A</sub> = -40 to +85°C<br>T <sub>A</sub> = -40 to +105°C (Note 15)<br>T <sub>J</sub> = -40 to +125°C |      |     |    |  |

|------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-----|----|--|

| Symbol     | Parameter                                                                                 | Min                                                                                                         | Unit |     |    |  |

| vSafe0Vthr | Safe Operating Voltage at "Zero Volts" Threshold                                          |                                                                                                             |      | 0.8 | V  |  |

| vSafe0Vhys | vSafe0V Hysteresis                                                                        |                                                                                                             | 40   |     | mV |  |

| VALARMLSB  | LSB of VBUS thresholds for VBUS_SNK_DISCL<br>VBUS_STOP_DISCL VALARMHCFGL VALARMLCFGL      |                                                                                                             | 50   |     | mV |  |

| pALARM     | Accuracy of VBUS thresholds for VBUS_SNK_DISCL<br>VBUS_STOP_DISCL VALARMHCFGL VALARMLCFGL |                                                                                                             | ±5   |     |    |  |

#### SOURCE AND SINK CONTROL SPECIFICATIONS

|                     |                                                                | T <sub>A</sub> = -40 to +85°C<br>T <sub>A</sub> = -40 to +105°C<br>(Note 15)<br>T <sub>J</sub> = -40 to +125°C |     |     |     |       |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Symbol              | 1                                                              | Parameter                                                                                                      | Min | Тур | Max | Unit  |

| R <sub>BLEED</sub>  | Equivalent Resistance for bleed discharging VBUS               | VBUS = 4.0 V to 21.5 V                                                                                         | 4   |     | 7   | kΩ    |

| vSrcSlewNeg         | Maximum slew rate allowed when discharging VBUS                | VBUS = 4.0 V to 21.5 V                                                                                         |     |     | 30  | mV/μs |

| tSafe0V             | Time to reach vSafe0V max                                      |                                                                                                                |     |     | 650 | ms    |

| tSafe5V             | Time to reach vSafe5V max                                      |                                                                                                                |     |     | 275 | ms    |

| tSrcSettle          | Time to discharge to vSrcNew                                   |                                                                                                                |     |     | 275 | ms    |

| tAUTO_DISCH_FAIL    | Time to declare auto discharge failure to discharge to vSafe0V | Device configured as Source.<br>Measure from CCSTAT change to Open                                             | 650 |     |     | ms    |

| tAUTO_DISCH_FAIL_5V | Time to declare auto discharge failure to discharge to vSafe5v | Device configured as Source.<br>Measure from CCSTAT change to Open                                             | 275 |     |     | ms    |

#### **OVER-TEMPERATURE SPECIFICATIONS**

| Symbol            | Parameter                                 | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------|-----|-----|-----|------|

| T <sub>SHUT</sub> | Temp. for VCONN Switch Turn Off           |     | 145 |     | °C   |

| T <sub>HYS</sub>  | Temp. Hysteresis for VCONN Switch Turn On |     | 10  |     | °C   |

#### WATCHDOG TIMER SPECIFICATIONS

| Symbol                  | Parameter                                                                           | Min  | Тур | Max  | Unit |

|-------------------------|-------------------------------------------------------------------------------------|------|-----|------|------|

| T <sub>HVWatchdog</sub> | Time from last I2C transaction or INTB pin as-<br>sertion to entering ErrorRecovery | 1500 |     | 2000 | ms   |

#### **IO SPECIFICATIONS**

|                     |                              |                     |                                                                                        | $\label{eq:T_A = -40 to +85°C} \begin{array}{c} T_A = -40 \ to +85°C \\ T_A = -40 \ to +105°C \ (Note \\ T_J = -40 \ to +125°C \\ \hline \\ $ |  | (Note 15) |      |

|---------------------|------------------------------|---------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------|------|

| Symbol              | Parameter                    | V <sub>DD</sub> (V) | Conditions                                                                             |                                                                                                                                                                                                                               |  | Max       | Unit |

| HOST INTERF         | ACE PINS(INT_N, DBG_N)       |                     |                                                                                        |                                                                                                                                                                                                                               |  |           |      |

| V <sub>OLINTN</sub> | Output Low Voltage           | 3.0 to 5.5          | I <sub>OL</sub> = 4 mA                                                                 |                                                                                                                                                                                                                               |  | 0.4       | V    |

| GPIOS, ORIEN        | IT AND MUX_SEL PINS          |                     |                                                                                        |                                                                                                                                                                                                                               |  |           |      |

| V <sub>IL</sub>     | Low-Level Input Voltage      | 3.0 to 5.5          |                                                                                        |                                                                                                                                                                                                                               |  | 0.4       | V    |

| V <sub>IH</sub>     | High-Level Input<br>Voltage  | 3.0 to 5.5          |                                                                                        | 1.2                                                                                                                                                                                                                           |  |           | V    |

| V <sub>OL</sub>     | Low-Level Output<br>Voltage  | 3.0 to 5.5          | $I_{OL} = 4 \text{ mA}$                                                                |                                                                                                                                                                                                                               |  | 0.4       | V    |

| V <sub>OH</sub>     | High-Level Output<br>Voltage | 3.0 to 5.5          | I <sub>OH</sub> = -2 mA                                                                | 0.7V <sub>DD</sub>                                                                                                                                                                                                            |  |           | V    |

| I <sub>IN</sub>     | Input Leakage                | 3.0 to 5.5          | Input Voltage 0 V to 5.5 V<br>(When GPIO is setup as an<br>input or Tri–Stated output) | -5                                                                                                                                                                                                                            |  | 5         | μA   |

| I <sub>OFF</sub>    | Off Input Leakage            | 0                   | Input Voltage 0 V to 5.5 V                                                             | -5                                                                                                                                                                                                                            |  | 5         | μA   |

| SRC, SNK AN         | D SRC_HV                     |                     |                                                                                        |                                                                                                                                                                                                                               |  |           |      |

| V <sub>OL</sub> Low-Level Output 3.0 to 5.<br>Voltage | I <sub>OL</sub> = 4 mA | 0.4 | V |

|-------------------------------------------------------|------------------------|-----|---|

|-------------------------------------------------------|------------------------|-----|---|

# SPECIEICATIONS (

|                          |                                                                  |                     |                             | $T_{A} = -40$ $T_{J} = -40$ |     |      |      |

|--------------------------|------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----|------|------|

| Symbol                   | Parameter                                                        | V <sub>DD</sub> (V) | Conditions                  | Min                         | Тур | Max  | Unit |

| SRC, SNK AI              | ND SRC_HV                                                        |                     |                             |                             |     |      |      |

| V <sub>OH</sub>          | High–Level Output 3.0 to 5.5<br>Voltage                          |                     | I <sub>OH</sub> = −2 mA     | 0.7V <sub>DD</sub>          |     |      | V    |

| I <sup>2</sup> C INTERFA | CE PINS – STANDARD, FAS                                          | ST OR FAST I        | MODE PLUS SPEED MODE SDA,   | SCL) (Note 1                | 3)  |      |      |

| V <sub>DDEXT</sub>       | External power supply to which SDA and SCL are pulled up         |                     |                             | 1.8                         |     | 3.6  | V    |

| V <sub>ILI2C</sub>       | Low-Level Input Voltage                                          | 3.0 to 5.5          |                             |                             |     | 0.4  | V    |

| V <sub>IHI2C</sub>       | High-Level Input<br>Voltage                                      | 3.0 to 5.5          |                             | 1.2                         |     |      | V    |

| V <sub>HYS</sub>         | Hysteresis of Schmitt<br>Trigger Inputs                          | 3.0 to 5.5          |                             | 0.2                         |     |      | V    |

| I <sub>i2C</sub>         | Input Current of SDA and SCL Pins,                               | 3.0 to 5.5          | Input Voltage 0.26 V to 2 V | -10                         |     | 10   | μA   |

| I <sub>CCTI2C</sub>      | VDD current when SDA<br>or SCL is HIGH                           | 3.0 to 5.5          | Input Voltage 1.8 V         | -10                         |     | 10   | μA   |

| V <sub>OLSDA</sub>       | Low-Level Output<br>Voltage at 2 mA Sink<br>Current (Open-Drain) | 3.0 to 5.5          |                             | 0                           |     | 0.36 | V    |

| I <sub>OLSDA</sub>       | Low-Level Output<br>Current (Open-Drain)                         | 3.0 to 5.5          | V <sub>OLSDA</sub> = 0.4 V  | 20                          |     |      | mA   |

5

pF

13.  $I^2C$  pull up voltage is required to be between 1.71 V and  $V_{\text{DD}}.$

Capacitance for Each I/O Pin

3.0 to 5.5

#### FAST MODE PLUS I<sup>2</sup>C SPECIFICATIONS

C<sub>I</sub> (Note 14)

| 0h.al                    | Damandar                                                          | Fast Mode Plus                     |      |      |  |  |  |

|--------------------------|-------------------------------------------------------------------|------------------------------------|------|------|--|--|--|

| Symbol                   | Parameter                                                         | Min.                               | Max. | Unit |  |  |  |

| f <sub>SCL</sub>         | I2C_SCL Clock Frequency                                           | 0                                  | 1000 | kHz  |  |  |  |

| t <sub>HD;STA</sub>      | Hold Time (Repeated) START Condition                              | 0.26                               |      | μs   |  |  |  |

| t <sub>LOW</sub>         | Low Period of I2C_SCL Clock                                       | 0.5                                |      | μs   |  |  |  |

| t <sub>HIGH</sub>        | High Period of I2C_SCL Clock                                      | 0.26                               |      | μs   |  |  |  |

| t <sub>SU;STA</sub>      | Set-up Time for Repeated START Condition                          | 0.26                               |      | μs   |  |  |  |

| t <sub>HD;DAT</sub>      | Data Hold Time                                                    | 0                                  |      | μs   |  |  |  |

| t <sub>SU;DAT</sub>      | Data Set-up Time                                                  | 50                                 |      | ns   |  |  |  |

| t <sub>r</sub>           | Rise Time of I2C_SDA and I2C_SCL Signals (Note 14)                | $20 \times (V_{DD}/5.5 \text{ V})$ | 120  | ns   |  |  |  |

| T <sub>f</sub> (Note 14) | Fall Time of I2C_SDA and I2C_SCL Signals (Note 14)                | $20 \times (V_{DD}/5.5 \text{ V})$ | 120  | ns   |  |  |  |

| t <sub>SU;STO</sub>      | Set-up Time for STOP Condition                                    | 0.26                               |      | μs   |  |  |  |

| t <sub>BUF</sub>         | Bus-Free Time between STOP and START Conditions (Note 14)         | 0.5                                |      | μs   |  |  |  |

| t <sub>SP</sub>          | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                                  | 50   | ns   |  |  |  |

14. Guaranteed by characterization. Not production tested. 15. Automotive part only, FUSB308BVMPX.

Figure 16. Definition of Timing for Full-Speed Mode Devices on the I2C Bus

#### Table 4. REGISTER DEFINITIONS

| Address | Register<br>Name | Туре | Rst Val    | Bit7                     | Bit6                                    | Bit5                  | Bit4                   | Bit3                | Bit2           | Bit1            | Bit0               |

|---------|------------------|------|------------|--------------------------|-----------------------------------------|-----------------------|------------------------|---------------------|----------------|-----------------|--------------------|

| 00h     | VENDIDL          | R    | 79h        |                          |                                         |                       | Vendor                 | ID Low              |                |                 |                    |

| 01h     | VENDIDH          | R    | 07h        |                          |                                         |                       | Vendor                 | ID High             |                |                 |                    |

| 02h     | PRODIDL          | R    | 34h        |                          |                                         |                       | Product                | t ID Low            |                |                 |                    |

| 03h     | PRODIDH          | R    | 01h        |                          | Product ID High                         |                       |                        |                     |                |                 |                    |

| 04h     | DEVIDL           | R    | 02h        |                          | Device ID Low                           |                       |                        |                     |                |                 |                    |

| 05h     | DEVIDH           | R    | 02h        |                          |                                         |                       | Device                 | ID High             |                |                 |                    |

| 06h     | TYPECREVL        | R    | 12h        |                          |                                         |                       | USB Type-C             | Revision Low        |                |                 |                    |

| 07h     | TYPECREVH        | R    | 00h        |                          |                                         |                       | USB Type-C             | Revision High       |                |                 |                    |

| 08h     | USBPDVER         | R    | 12h        |                          |                                         |                       | USB PD                 | Version             |                |                 |                    |

| 09h     | USBPDREV         | R    | 20h        |                          |                                         |                       | USB PD                 | Revision            |                |                 |                    |

| 0Ah     | PDIFREVL         | R    | 12h        |                          | USB PD Interface Revision Low (Version) |                       |                        |                     |                |                 |                    |

| 0Bh     | PDIFREVH         | R    | 10h        |                          |                                         | USB                   | PD Interface Re        | vision High (Rev    | vision)        |                 |                    |

| 10h     | ALERTL           | R/WC | 00h        | I_VBUS<br>ALRM_HI        | I_TXSUCC                                | I_TXDISC              | I_TXFAIL               | I<br>RXHRDRST       | I_RXSTAT       | I_PORT_<br>PWR  | I_CCSTAT           |

| 11h     | ALERTH           | R/WC | 00h        | I_VD_<br>ALERT           | Reserved                                | Reserved              | Reserved               | I_VBUS_<br>SNK_DISC | I_RX_FULL      | I_FAULT         | I_VBUS_<br>ALRM_LO |

| 12h     | ALERTMSKL        | R/W  | FFh        | M_VBUS_<br>ALRM_HI       | M_TXSUCC                                | M_TX_DISC             | M_TXFAIL               | M<br>RXHRDRST       | M_RXSTAT       | M_PORT_<br>PWR  | M_CCSTAT           |

| 13h     | ALERTMSKH        | R/W  | 0Fh        | M_VD_<br>ALERT           | Reserved                                | Reserved              | Reserved               | M_VBUS_<br>SNK_DISC | M_RX_FULL      | M_FAULT         | M_VBUS_<br>ALRM_LO |

| 14h     | PWRSTATMSK       | R/W  | FFh        | M_DEBUG_<br>ACC          | M_INIT                                  | M_SRC_HV              | M_SRC_<br>VBUS         | M_VBUS_<br>VAL_EN   | M_VBUS_<br>VAL | M_VCONN_<br>VAL | M<br>SNKVBUS       |

| 15h     | FAULTSTATMSK     | R/W  | B3h        | M_ALL_<br>REGS_<br>RESET | Reserved                                | M_AUTO_<br>DISCH_FAIL | M_FORCE_<br>DISCH_FAIL | Reserved            | Reserved       | M_VCONN_<br>OCP | M_I2C_ERR          |

| 16h17h  | Reserved         | R    | 00h        |                          |                                         |                       | Rese                   | erved               |                |                 |                    |

| 18h     | STD_OUT_CFG      | R/W  | 40h        | TRI_STATE                | DEBUG_<br>ACC                           | Reserved              | Reserved               | MUX_                | CTRL           | Reserved        | ORIENT             |

| 19h     | TCPC_CTRL        | R/W  | 00h        | Rese                     | erved                                   | EN_<br>WATCHDOG       | DEBUG_<br>ACC_CTRL     | I2C_CLK_            | STRECTH        | BIST_<br>TMODE  | ORIENT             |

| 1Ah     | ROLECTRL         | R/W  | 0Ah<br>4Ah | Reserved                 | DRP                                     | RP_VAL                |                        | CC2_TERM            |                | CC1_TERM        |                    |

#### Table 4. REGISTER DEFINITIONS (continued)

| Address | Register<br>Name | Туре | Rst Val | Bit7                           | Bit6             | Bit5                | Bit4                 | Bit3                                    | Bit2            | Bit1          | Bit0               |

|---------|------------------|------|---------|--------------------------------|------------------|---------------------|----------------------|-----------------------------------------|-----------------|---------------|--------------------|

| 1Bh     | FAULTCTRL        | R/W  | 00h     |                                | Reserved         |                     | Reserved             | DISCH_<br>TIMER_DIS                     | Reserved        | Reserved      | VCONN_<br>OCP_DIS  |

| 1Ch     | PWRCTRL          | R/W  | 60h     | Reserved                       | VBUS_MON         | DIS_VALRM           | AUTO_<br>DISCH       | EN_BLEED_<br>DISCH                      | FORCE_<br>DISCH | VCONN_<br>PWR | EN_VCONN           |

| 1Dh     | CCSTAT           | R    | 00h/20h | Rese                           | erved            | LOOK4CON            | CON_RES              | CC2_                                    | STAT            | CC1           | STAT               |

| 1Eh     | PWRSTAT          | R    | 08h     | DEBUG_<br>ACC                  | TCPC_INIT        | SOURCE_<br>HV       | SOURCE_<br>VBUS      | VBUS_VAL_<br>EN                         | VBUS_VAL        | VCONN_<br>VAL | SNKVBUS            |

| 1Fh     | FAULTSTAT        | R    | 80h     | ALL_REGS_<br>RESET             | Reserved         | AUTO_<br>DISCH_FAIL | FORCE_<br>DISCH_FAIL | Reserved                                | Reserved        | VCONN_<br>OCP | I2C_ERR            |

| 20h22h  | Reserved         | R    | 00h     |                                |                  |                     | Rese                 | erved                                   | •               |               |                    |

| 23h     | COMMAND          | R    | 00h     |                                |                  |                     | Com                  | mand                                    |                 |               |                    |

| 24h     | DEVCAP1L         | R    | DDh     | R                              | OLES_SUPPOR      | AL                  | ROLES_<br>SUPPORT    | SWITCH_<br>VCONN                        | SNK_VBUS        | SRC_HV        | SRC_VBUS           |

| 25h     | DEVCAP1H         | R    | 1Eh     |                                | Reserved         |                     | BLEED_DIS            | FORCE_DIS VBUS_ RP_SUP<br>MEAS_<br>ALRM |                 |               | IPPORT             |

| 26h     | DEVCAP2L         | R    | D7h     | SNK_DISC_<br>DETECT            | STOP<br>DISCH    | VBUS_A              | LRM_LSB              | VCONN_POWER_CAP                         |                 |               | VCONN<br>FAULT_CAP |

| 27h     | DEVCAP2H         | R    | 01h     |                                |                  |                     | Reserved             | •                                       |                 |               | Watchdog<br>Timer  |

| 28h     | STD_IN_CAP       | R    | 00h     |                                |                  |                     | Rese                 | erved                                   |                 |               |                    |

| 29h     | STD_OUT_CAP      | R    | 41h     | Reserved                       | DEBUG_<br>ACC    |                     | Reserved             |                                         | MUX_CTRL        | Reserved      | ORIENT             |

| 2Ah2Dh  | Reserved         | R    | 00h     |                                |                  |                     | Rese                 | erved                                   |                 | •             | •                  |

| 2Eh     | MSGHEADR         | R/W  | 02h     |                                | Reserved         |                     | Cable Plug           | Data Role                               | USB P           | D Rev         | PWR Role           |

| 2Fh     | RXDETECT         | R/W  | 00h     | Reserved                       | EN_CABLE_<br>RST | EN_HRD_<br>RST      | EN_SOP2_<br>DBG      | EN_SOP1_<br>DBG                         | EN_SOP2         | EN_SOP1       | EN_SOP             |