# 12-Bit Low Power SAR ADC NCD98010, NCD98011

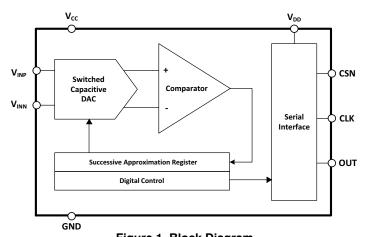

The NCD98010 (unsigned output) and the NCD98011 (signed output) ADC products provide an extremely low power solution for analog to digital conversion applications using a capacitor–based successive–approximation architecture. Optimized for low power and speed, the NCD98010/1 can achieve a sample rate of 2 MSPS while consuming less than 1 mW of power. The device also features a large input voltage range of 1.65 V to 3.3 V for various applications for both analog and digital supplies. The SPI–compatible interface provides a straight–forward data–acquisition method.

#### **Features**

- Nanowatt Power Consumption

- Fully Differential Input

- 2-MSPS Throughput

- Small Package Size

- Pre-Calibrated

- SPI Interface

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

## **Typical Applications**

- Low-Power Data Acquisition

- Battery-powered Equipment

- Level Sensors

- Ultrasonic Flow Meters

- Motor Controls

- Wearable Fitness

- Portable Medical Equipment

- Glucose Meters

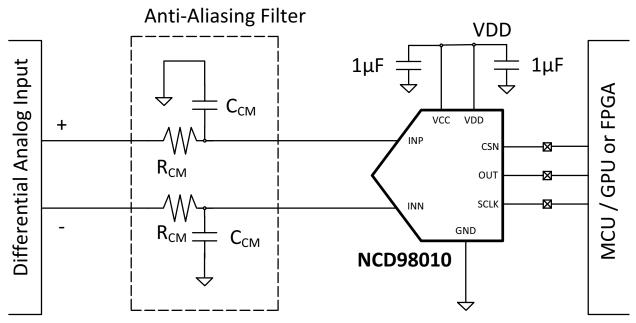

Figure 1. Block Diagram

1

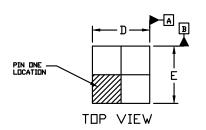

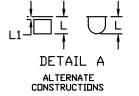

#### MARKING DIAGRAMS

X2QFN8 DP SUFFIX CASE 722AM

XX = Specific Device Code M = Date Code

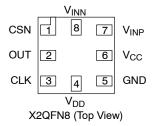

#### **PIN CONFIGURATION**

#### **ORDERING INFORMATION**

| Device         | Package | Shipping <sup>†</sup> |

|----------------|---------|-----------------------|

| NCD98010XMXTAG | X2QFN   | 5000 / Tape &         |

| NCD98011XMXTAG | AZQFN   | Reel                  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **PIN DESCRIPTION**

| X2QFN<br>Pin No. | Name             | Function                                |

|------------------|------------------|-----------------------------------------|

| 1                | CSN              | Chip select (active low)                |

| 2                | OUT              | Data Output (serialized)                |

| 3                | CLK              | Clock                                   |

| 4                | VDD              | Digital I/O supply voltage              |

| 5                | GND              | Common ground for all pins              |

| 6                | VCC              | Analog supply and ADC reference voltage |

| 7                | V <sub>INP</sub> | Analog input, positive signal           |

| 8                | V <sub>INN</sub> | Analog input, negative signal           |

#### **MAXIMUM RATINGS**

| Rating                                        | Symbol             | Value        | Unit |

|-----------------------------------------------|--------------------|--------------|------|

| Supply Voltage Range                          | V <sub>CC</sub>    | -0.3 to 3.63 | V    |

| Supply Voltage Range                          | V <sub>DD</sub>    | -0.3 to 3.63 | V    |

| Input Voltage Range                           | V <sub>INP</sub>   | -0.3 to 3.63 | V    |

| Input Voltage Range                           | V <sub>INN</sub>   | -0.3 to 3.63 | V    |

| Output Voltage Range                          | V <sub>OUT</sub>   | -0.3 to 3.63 | V    |

| CSN Input Voltage Range                       | V <sub>EN</sub>    | -0.3 to 3.63 | V    |

| Storage Temperature Range                     | T <sub>STG</sub>   | -40 to 150   | °C   |

| Lead Temperature, Soldering (10 sec.)         | T <sub>SLD</sub>   | 260          | °C   |

| ESD Capability, Human Body Model (Note 1)     | ESD <sub>HBM</sub> | 2.0          | kV   |

| ESD Capability, Charged Device Model (Note 1) | ESD <sub>CDM</sub> | 500          | V    |

| Latch-up Current Immunity (Note 1)            | LU                 | 100          | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Tested by the following methods @ T<sub>A</sub> = 25°C:

ESD Human Body Model tested per JESD22–A114

ESD Charged Device Model per ESD STM5.3.1

Latch-up Current tested per JESD78.

# **RECOMMENDED OPERATING CONDITIONS**

| Rating                     | Symbol          | Min  | Max | Unit |

|----------------------------|-----------------|------|-----|------|

| Analog Supply Voltage      | V <sub>CC</sub> | 1.65 | 3.6 | V    |

| Digital I/O Supply Voltage | V <sub>DD</sub> | 1.65 | 3.6 | V    |

| Ground                     | GND             |      | 0   | V    |

| Ambient Temperature        | T <sub>A</sub>  | -40  | 120 | °C   |

| Junction Temperature       | TJ              | -40  | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** ( $T_J = 25^{\circ}C$ , $V_{CC} = 3$ V, unless otherwise noted)

| Parameter                                    | Conditions                                      | Symbol               | Min              | Тур    | Max                   | Unit      |

|----------------------------------------------|-------------------------------------------------|----------------------|------------------|--------|-----------------------|-----------|

| POWER SUPPLY REQUIREMENT                     | S                                               |                      |                  |        |                       |           |

| Analog Supply and ADC reference              |                                                 | V <sub>CC</sub>      | 1.65             | 3      | 3.6                   | V         |

| Digital I/O Supply                           |                                                 | $V_{DD}$             | 1.65             | 3      | 3.6                   | V         |

|                                              | 2 MSPS for V <sub>CC</sub> = 3.6 V              |                      |                  | 100    | 150                   | μΑ        |

| Analan Cumalu Cumant                         | 1 MSPS for V <sub>CC</sub> = 3 V                |                      |                  | 50     |                       | μΑ        |

| Analog Supply Current                        | 100 kSPS for V <sub>CC</sub> = 3.6 V            | l <sub>VCC</sub>     |                  | 7.6    | 20                    | μΑ        |

|                                              | 1 MSPS for V <sub>CC</sub> = 1.8 V              | -                    |                  | 30     |                       | μΑ        |

|                                              | 2 MSPS for V <sub>CC</sub> = 3.6 V              |                      |                  | 300    | 540                   | μW        |

| Analag Dawer Dissination                     | 1 MSPS for V <sub>CC</sub> = 3 V                | D                    |                  | 150    |                       | μW        |

| Analog Power Dissipation                     | 100 kSPS for V <sub>CC</sub> = 3.6 V            | P <sub>VCC</sub>     |                  | 15     | 72                    | μW        |

|                                              | 1 MSPS for V <sub>CC</sub> = 1.8 V              | -                    |                  | 54     |                       | μW        |

|                                              | 2 MSPS for V <sub>DD</sub> = 3.6 V              |                      |                  | 852    |                       | μΑ        |

| Digital Supply Current                       | 1 MSPS for V <sub>DD</sub> = 3 V                | 1                    |                  | 425    |                       | μΑ        |

| Dependent on SDO loading (tested with ~7 pF) | 100 kSPS for V <sub>DD</sub> = 3.6 V            | I <sub>VDD</sub>     |                  | 45     |                       | μΑ        |

|                                              | 1 MSPS for V <sub>DD</sub> = 1.8 V              | -                    |                  | 136    |                       | μΑ        |

| Standby current (CSN high)<br>(Note 2)       | V <sub>CC</sub> = 3.6 V                         | I <sub>STNDBY</sub>  |                  | 3.9    | 6                     | μΑ        |

| ANALOG INPUT                                 |                                                 |                      |                  |        |                       |           |

| Full-Scale Voltage Span                      | Common Mode Voltage=V <sub>CC</sub> /2          | $V_{fs}$             | -V <sub>CC</sub> |        | V <sub>CC</sub>       | $V_{ppd}$ |

| Absolute Voltage Range                       | V <sub>inp</sub> to GND                         |                      | -0.2             |        | V <sub>CC</sub> + 0.1 | V         |

|                                              | V <sub>inn</sub> to GND                         |                      | -0.2             |        | V <sub>CC</sub> + 0.1 | V         |

| Sampling Capacitance                         | Measured with 1kHz, 1V Stimuli                  | C <sub>S</sub>       |                  | 2      |                       | pF        |

| SYSTEM PERFORMANCE                           |                                                 | u.                   |                  | •      | <b>u</b>              |           |

| Resolution                                   |                                                 |                      |                  | 12     |                       | Bits      |

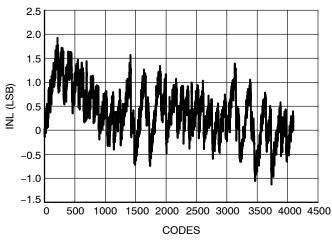

|                                              | V <sub>CC</sub> = 1.8 V                         | INL                  | -2               | 0      | 2                     |           |

| Integral Nonlinearity (Note 3)               | V <sub>CC</sub> = 3.3 V                         |                      | -2               | 0      | 2                     | LSB       |

| D.W                                          | V <sub>CC</sub> = 1.8 V                         | 5                    | -1               | 0      | 1.5                   |           |

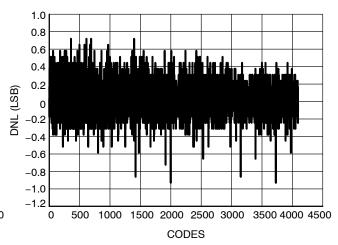

| Differential Nonlinearity (Note 3)           | V <sub>CC</sub> = 3.3 V                         | DNL -                | -1               | 0      | 1.5                   | LSB       |

| 0" . =                                       | V <sub>CC</sub> = 1.8 V                         | _                    |                  | 0      |                       |           |

| Offset Error                                 | V <sub>CC</sub> = 3.3 V                         | E <sub>O</sub>       | -10              | 0      | 10                    | LSB       |

| Effective Noveles and India                  | V <sub>CC</sub> = 1.8 V                         | ENIOD                |                  | 10     |                       |           |

| Effective Number of bits                     | V <sub>CC</sub> = 3.3 V                         | ENOB                 |                  | 11.2   |                       |           |

| Offset error drift with temperature          |                                                 | dV <sub>OS</sub> /dT |                  | 0.02   |                       | ppm/°C    |

| Onia France                                  | V <sub>CC</sub> = 1.8 V                         | _                    | -0.6             | 0.3    | 0.6                   | 0/50      |

| Gain Error                                   | V <sub>CC</sub> = 3.3 V                         | E <sub>G</sub>       |                  | 0.3    |                       | %FS       |

| Gain error drift with temperature            |                                                 |                      |                  | 0.0006 |                       | %FS/°C    |

| Missing Codes                                |                                                 |                      |                  | 0      |                       | Codes     |

| SAMPLING DYNAMICS                            | •                                               | l.                   |                  | •      | •                     |           |

| Acquisition Time                             |                                                 |                      |                  |        | 62.5                  | ns        |

| Maximum throughput rate                      |                                                 |                      |                  | 2      |                       | MSPS      |

| DYNAMIC CHARACTERISTICS                      | +                                               | ļ                    |                  |        | Į.                    | <u> </u>  |

|                                              | f <sub>IN</sub> = 1 kHz V <sub>CC</sub> = 3.3 V | SNR 70 65            |                  |        |                       |           |

| Signal-to-Noise Ratio                        | f <sub>IN</sub> = 1 kHz V <sub>CC</sub> = 1.8 V |                      |                  |        |                       | dB        |

## **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, V<sub>CC</sub> = 3 V, unless otherwise noted)

| Parameter                               | Conditions                                      | Symbol          | Min                     | Тур | Max                  | Unit |

|-----------------------------------------|-------------------------------------------------|-----------------|-------------------------|-----|----------------------|------|

| DYNAMIC CHARACTERISTICS                 |                                                 |                 | 1                       |     |                      |      |

| Total-Harmonic Distortion               | f <sub>IN</sub> = 1 kHz V <sub>CC</sub> = 3.3 V | THD             |                         | -80 |                      | dB   |

|                                         | $f_{IN} = 1 \text{ kHz V}_{CC} = 1.8 \text{ V}$ | עחו             |                         | -80 |                      |      |

| Signal-to-Noise and Distortion (Note 4) | $f_{IN} = 1 \text{ kHz V}_{CC} = 3.3 \text{ V}$ | SINAD           | 68                      | 69  |                      | dB   |

|                                         | $f_{IN} = 1 \text{ kHz V}_{CC} = 1.8 \text{ V}$ | SINAD           |                         | 62  |                      |      |

| Spurious-Free Dynamic Range (Note 4)    | $f_{IN} = 1 \text{ kHz V}_{CC} = 3.3 \text{ V}$ | SFDR            | 69                      | 80  |                      | dB   |

|                                         | $f_{IN} = 1 \text{ kHz V}_{CC} = 1.8 \text{ V}$ | SFUN            |                         | 74  |                      |      |

| DIGITAL INPUT/OUTPUT                    |                                                 |                 | •                       |     | •                    |      |

| High-Level Input Voltage                |                                                 | V <sub>IH</sub> | V <sub>DD</sub> *0.7    |     |                      | V    |

| Low-Level Input Voltage                 |                                                 | V <sub>IL</sub> |                         |     | V <sub>DD</sub> *0.3 | V    |

| High-Level Output Voltage               | 2 mA drive                                      | V <sub>OH</sub> | V <sub>DD</sub> – 0.5 V |     |                      | V    |

| Low-Level Output Voltage                | 2 mA drive                                      | V <sub>OL</sub> |                         |     | GND+0.5              | V    |

|                                         |                                                 |                 |                         |     |                      |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 2. Standby current includes both digital and analog currents.

- 3. INL and DNL parameters were verified via bench testing and are not used for production screening.

- 4. SINAD and SFDR are tested at production and guaranteed by correlation to bench test results.

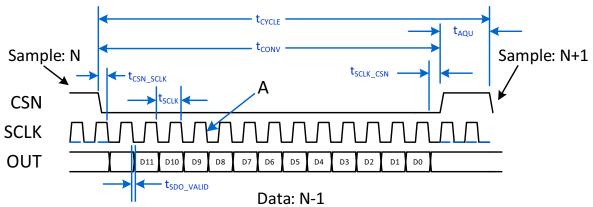

# TIMING CHARACTERISTICS ( $T_J = 25^{\circ}C$ unless otherwise specified)

| Parameter                            | Conditions         | Symbol                 | Min   | Тур | Max   | Unit  |

|--------------------------------------|--------------------|------------------------|-------|-----|-------|-------|

| TIMING SPECIFICATIONS                |                    |                        |       |     |       |       |

| Throughput                           |                    | f <sub>THROUGH</sub>   |       |     | 2     | MSPS  |

| Cycle Time                           |                    | f <sub>CYCLE</sub>     | 0.5   |     |       | μs    |

| Conversion Time                      |                    | f <sub>CONV</sub>      | 437.5 |     |       | ns    |

| Data Delay                           |                    |                        |       | 1   |       | cycle |

| TIMING REQUIREMENTS                  | •                  |                        |       |     |       |       |

| Acquisition Time (CSN high)          |                    | t <sub>ACQ</sub>       | 62.5  |     |       | ns    |

| CLK Frequency                        |                    | f <sub>CLK</sub>       |       |     | 32    | MHz   |

| CLK Period                           |                    | t <sub>CLK</sub>       |       |     | 31.25 | ns    |

| CSN Falling to 1st SCLK falling edge |                    | t <sub>CSN_SCLK</sub>  | 15.75 |     |       | ns    |

| Last SCLK falling edge to CSN rising |                    | t <sub>SCLK_CSN</sub>  | 15.75 |     |       | ns    |

| Falling SCLK to SDO valid (Note 5)   | Assumed 10 pF Load | t <sub>SDO_VALID</sub> |       |     | 30    | ns    |

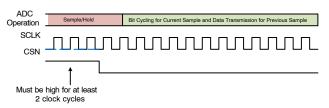

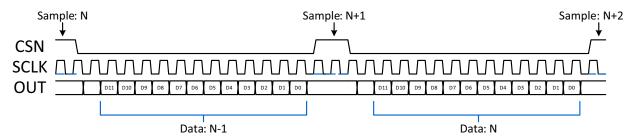

<sup>5.</sup> When SCLK is running at higher frequencies, the t<sub>SDO\_VALID</sub> of 30 ns requires SDO to be sampled on the falling edge of SCLK at the end of the bit width just before SDO changes to the next output. This will ensure acquisition of the correct data. For example, location A shown below would be the best place to sample SDO for the acquisition of bit 9.

Figure 2. Serial Interface Timing

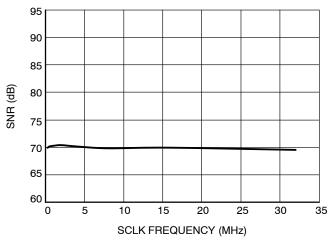

#### **TYPICAL CHARACTERISTICS**

76 THD 75 74 73 SNR (dB) 72 SNR 71 70 SNDR 69 68 67 66 -60 -40 -20 0 20 40 80 100 TEMPERATURE (°C)

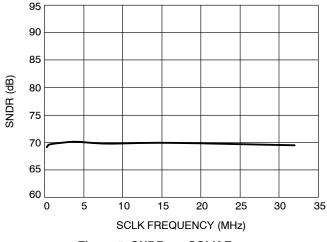

Figure 3. SNR vs. SCLK Frequency

Figure 4. SNR vs. Temperature

Figure 5. SNDR vs. SCLK Frequency

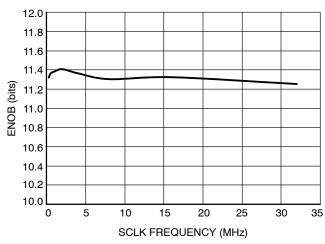

Figure 6. ENOB vs. SCLK Frequency

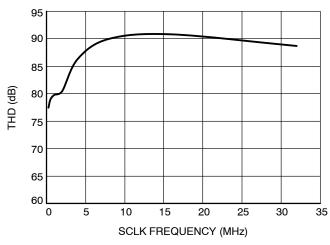

Figure 7. THD vs. SCLK Frequency

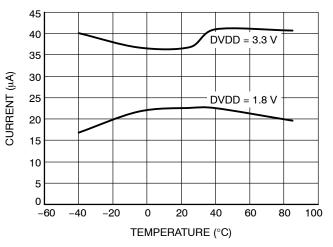

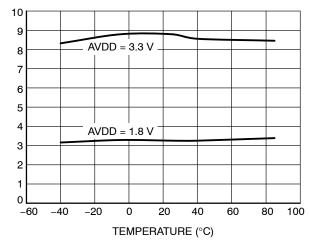

Figure 8. DVDD Current vs. Temperature (SCLK = 2 kHz)

## **TYPICAL CHARACTERISTICS**

CURRENT DRAW (µA)

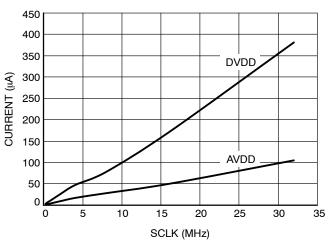

Figure 9. Current vs. SCLK Frequency

Figure 10. AVDD Current vs. Frequency

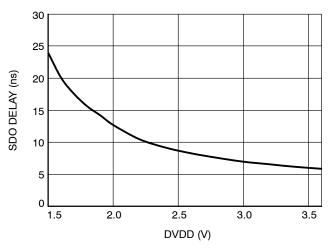

Figure 11. SDO Delay from Falling Edge of SCLK

Figure 12. Typical INL

Figure 13. Typical DNL

#### **TERMINOLOGY**

Understanding how ADC metrics affect application performance is key to obtaining desired performance. Key terminology are defined below and should be used when determining overall system performance when using the NDC98010/1.

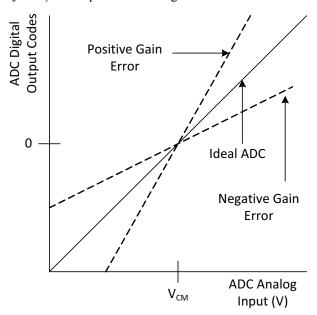

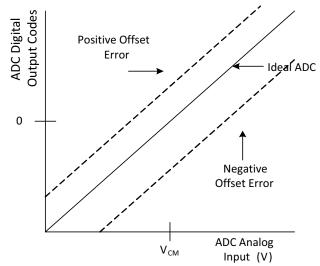

#### Offset and Gain Error

Offset and gain, if characterized, can be calibrated out post digitization. An ideal ADC has a linear transfer function following the equation y = m\*x + b, where m is the gain and b is the offset. Ideally the offset would be 0, and the gain would be

$$m = \frac{(2^{n-1})}{V_{inputRange}}$$

(eq. 1)

Any deviation from an offset of 0 and the ideal gain is considered error. Although these errors can be calibrated out, any initial gain error reduces the ADCs dynamic range. The plots below shows examples of these errors. Calibrating these errors out would be achieved by adding / subtracting codes to get the digitized output to 0 when the inputs are shorted together at  $V_{CM}$ . After the offset (for signed output format) has been calibrated, samples can be taken at both polarities to determine the gain error. The output can be multiplied by a scale factor (after the offset has been adjusted) to compensate for the gain error.

Figure 14. Gain Error Example

Figure 15. Offset Error Example

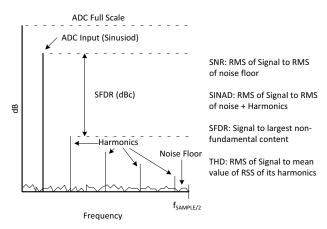

SNR = (6.02N + 1.76) dB, where N is the number of bits. A 12 bit converter has a theoretical SNR of 74 dB.

#### SINAD (or SNDR)

SINAD is the signal to noise and distortion ratio. SINAD is the ratio of the RMS signal amplitude to the mean value of the root sum square (RSS) of all other spectral components, including harmonics, but excluding DC. SINAD is useful because it provides a metric for the ADCs overall dynamic performance, as it includes all components which make up noise and distortion.

#### **SFDR**

SFDR is the Spurious Free Dynamic Range. SFDR is the ratio of the RMS value of the signal to the RMS value of the highest magnitude spurious signal regardless of where it falls in the frequency spectrum. The highest spur might not be a harmonic, though it typically is.

#### **THD**

THD is the total harmonic distortion, defined as ratio of the RMS of the primary signal and the mean of the root sum squared of all the harmonics. Generally only the first 5 harmonics are considered. The figure below shows an example of these AC metrics in the frequency domain.

THD = 20 log

$$\frac{\sqrt{H_2^2 + H_3^2 + H_4^2 + H_5^2}}{H_1}$$

(eq. 2)

Figure 16. Spurious Free Dynamic Range in the Frequency Domain

#### **ENOB**

The effective number of bits describes the dynamic range of the ADC. It quantifies the actual resolution of the ADC taking into account noise and distortion. ENOB typically changes over ADC input frequency, and is an important metric for non–DC applications. It is defined as:

ENOB =

$$\frac{\text{SINAD} - 1.76}{6.02}$$

(eq. 3)

#### THEORY OF OPERATION

The NCD98010/1 uses a successive approximation architecture. Conversion from an analog signal to a digital signal occurs in 2 different stages over 16 clock cycles. The first stage is a differential sample and hold operation, where the input Vinn and Vinp voltages are sampled onto a differential charge re–distribution capacitive array. The second stage implements a binary decision tree, bit cycling through  $1/2^{\rm N}$  divisions of the reference. The internal digital control block steps through each of 12 bits to determine whether that bit in the digital output code is higher or lower than the sampled signal.  $V_{\rm CC}$  acts as the analog supply and the ADC reference. This allows for a maximum input range of 0 V to  $V_{\rm CC}$ .

Figure 17. SAR ADC Internal Operation

#### **ADC TRANSFER FUNCTION**

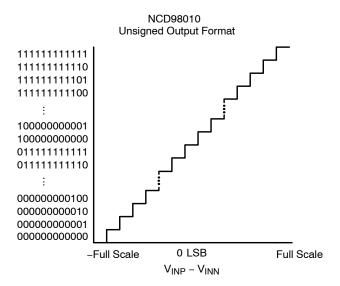

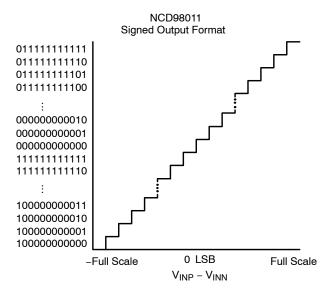

The NCD98010/1 offers a full input range of 0 V to VCC. The format of the digital output is offered in an unsigned format (NCD98010) and a signed format (NCD98011). The output code resulting from  $V_{\rm INN}$  and  $V_{\rm INP}$  tied together and held at VCC/2 is therefore 0h000 for the NCD98011 and 0h100 for the NCD98010. This distinction is shown below in Figures 18 and 19.

Figure 18. NCD98010 Unsigned Output Definition

Figure 19. NCD98011 Signed Output Definition

#### APPLICATION INFORMATION

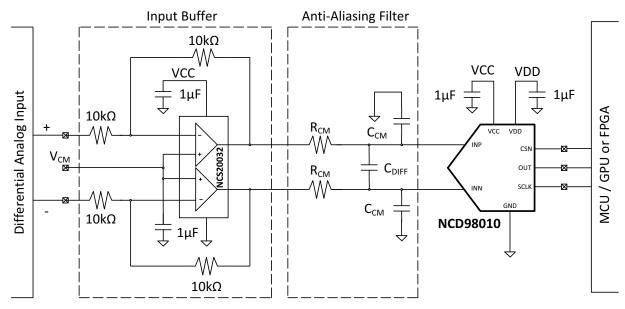

The NCD98010/1 supports many application due to its small size and low power. The typical connection diagram for the NCD98010/1 maximizing performance is shown below in Figure 20.

Figure 20. NCD Connection Diagram

#### **Buffering**

Many applications of the NCD98010/1 benefit by a differential input buffer. A unity gain buffer provides current drive to support the anti–aliasing filter and the 2 pF of ADC input capacitance for applications where very high input impedance is required. Input buffers also allow for control of the common mode voltage to maximize the full scale range of the ADC by setting  $V_{\rm CM}$  to VCC/2. Input buffers are recommended for applications where the source of the differential analog inputs require extremely high input impedance. Noise introduced by the input buffers should be less than the quantization noise of the ADC (74 dB SNR) to avoid becoming the dominant noise source. Use buffers with sufficient bandwidth (> Nyquist:  $F_{\rm SAMPLE}$  / 2) and an offset less than 1/2 LSB to avoid introducing additional noise and offset errors.

#### Anti-Alias Filter

The use of 2 common mode filters in addition to a differential filter is recommended to maintain high common mode rejection. These anti–aliasing filter are built using  $R_{CM}$ ,  $C_{CM}$ , and  $C_{DIFF}$  as shown above in Figure 12 in the Anti–Aliasing Filter box. The equations for determining the cutoff frequencies of each filter are as follows:

$$f_{\text{cutoff\_CM}}(\text{HZ}) = \frac{1}{2\pi \cdot R_{\text{CM}} \cdot C_{\text{CM}}}$$

(eq. 4)

(1) Cutoff frequency for the common mode filters.

$$f_{\text{cutoff\_DIFF}}(\text{HZ}) = \frac{1}{2\pi \cdot 2R_{\text{CM}} \cdot C_{\text{DIFF}}}$$

(eq. 5)

(2) Cutoff frequency for the differential filter.

The common mode filter cutoff frequency should be no greater than the Nyquist frequency ( $F_{SAMPLE}$  / 2). Set the differential cutoff frequency to be one decade less than the common–mode cutoff frequency by increasing the differential capacitor ( $C_{DIFF}$ ) by a factor of 10 over  $C_{CM}$ . This will help to reduce errors caused by common mode filter component mismatch. Selecting the appropriate values for the anti–aliasing filter is important to maintain peak performance. Adding resistors to the signal path will introduce noise. Keeping  $R_{CM}$  as small as possible will mitigate additional noise and error. The thermal noise introduced by the filter resistors can be calculated by:

$$V_n \left( \frac{nV}{\sqrt{Hz}} \right) = \sqrt{4 \cdot k \cdot T \cdot R_{CM}}$$

(eq. 6)

(3) Noise introduced by series anti-aliasing filter.

Where k = 1.38E-23 J/K (Boltzmann's constant) and T is the temperature in degree Kelvin.

Using smaller resistors and larger capacitors to achieve the desired cutoff frequency will help mitigate noise and charge injection. When choosing anti-aliasing filter components, ensure that the settling time is short enough for the input to be within 1/2 LSB of the desired value before the CSN goes low to begin the conversion.

#### **Power Supply Decoupling**

Local ADC supply decoupling is essential for maintaining high power supply rejection ratio. For the NCD98010/1, the analog supply (VCC) is also the reference for the ADC. Any noise or drift greater than 1/2 LSB will affect the DNL and INL of the converter. Use local decoupling capacitors of

$1~\mu F$ . All decoupling capacitors must connect directly to a low impedance ground plane in order to be effective. Short traces or vias are required to minimize additional series inductance. Ceramic capacitors are recommended based on their low ESR and ESL. X7R ceramic capacitors are recommended for applications involving a wide temperature range.

#### **Minimal Component Realization**

For applications where minimizing board space trumps ADC performance, the NCD98010/1 connection diagram can be reduced as shown in Figure 21 below. The removal of the input buffering may be an option depending on the nature of the differential analog input source. Removing the anti-aliasing filter would come at the expense of reduced ENOB due to the digitization of aliased signals.

Figure 21. Reduced Component Connection Diagram

## **Output Timing / Definition**

Figure 22 below shows the NCD98010/1 output format. There is a 1 sample latency associated with the output data. The digital data for analog input sampled are clocked out of the ADC by SCLK one conversion later, as shown in the diagram below.

Figure 22. NCD98010/1 Output Format

#### **Layout Guidelines**

Ideal PCB layouts have a ground plane placed underneath the device and the PCB is partitioned into digital and analog sections supporting the analog inputs to the ADC on one side, and the digital interface on the other side. To avoid the coupling of digital noise into the analog partition, care must be taken not to cross digital signals with the analog input

signals. Keep the analog input signals and the VCC supply / reference signal away from noise digital signals. Recommended bypass capacitances should be places as close as possible to the VCC and VDD pins, and the path to ground needs to be a low inductance low resistance local connection.

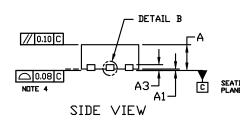

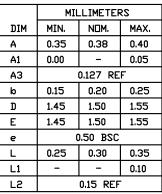

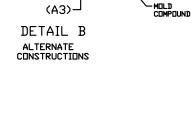

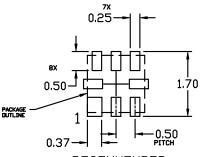

#### **X2QFN8, 1.5x1.5, 0.5P** CASE 722AM ISSUE O

**DATE 20 JUL 2018**

#### NOTES:

EXPOSED COPPER

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 APPLIES TO THE PLATED TERMINALS AND IS MEASURED BETWEEN 0.15 AND 0.20 FROM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

RECOMMENDED MOUNTING FOOTPRINT

# GENERIC MARKING DIAGRAM\*

BOTTOM VIEW

X = Specific Device Code

M = Date Code

= Pb–Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " •", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON94548G           | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | X2QFN8, 1.5x1.5, 0.5P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMi., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative