# **High Speed Quad-Channel Digital Isolator**

# NCID9401, NCID9411, NCID9400, NCID9410

## Description

The NCID9401, NCID9411, NCID9400 and NCID9410 are galvanically isolated high-speed quad-channel digital isolator with output enable. This device supports isolated communications thereby allowing digital signals to communicate between systems without conducting ground loops or hazardous voltages.

It utilizes **onsemi's** patented galvanic off-chip capacitor isolation technology and optimized IC design to achieve high insulation and high noise immunity, characterized by high common mode rejection and power supply rejection specifications. The thick ceramic substrate yields capacitors with ~25 times the thickness of thin film on-chip capacitors and coreless transformers. The result is a combination of the electrical performance benefits that digital isolators offer with the safety reliability of a >0.5 mm insulator barrier similar to what has historically been offered by optocouplers.

The device is housed in a 16-pin wide body small outline package.

#### **Features**

- Off-Chip Capacitive Isolation to Achieve Reliable High Voltage Insulation

- ◆ DTI (Distance Through Insulation):  $\geq$  0.5 mm

- ◆ Maximum Working Insulation Voltage: 2000 V<sub>peak</sub>

- Bi-directional Communication

- 100 kV/µs Minimum Common Mode Rejection

- 8 mm Creepage and Clearance Distance to Achieve Reliable High Voltage Insulation

- Specifications Guaranteed Over 2.5 V to 5.5 V Supply Voltage and -40°C to 125°C Extended Temperature Range

- Over Temperature Detection

- Output Enable Function (Primary and Secondary side)

- NCIV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable (Pending)

- Safety and Regulatory Approvals

- UL1577, 5000 VRMS for 1 Minute

- ◆ DIN EN/IEC 60747-17 (Pending)

#### **Typical Applications**

- Isolated PWM Control

- Industrial Fieldbus Communications

- Microprocessor System Interface (SPI, I<sup>2</sup>C, etc.)

- Programmable Logic Control

- Isolated Data Acquisition System

- Voltage Level Translator

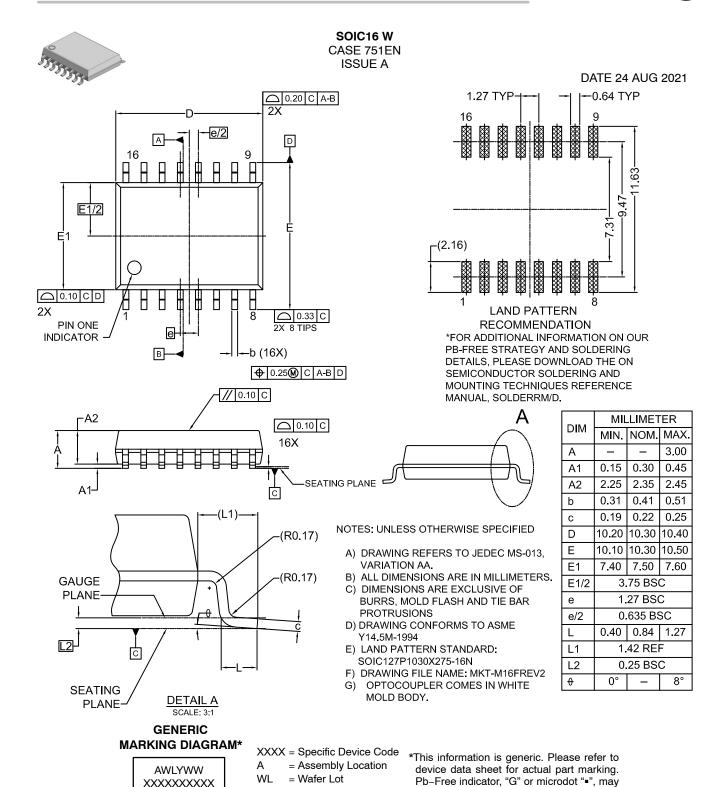

SOIC16 W CASE 751EN

## **MARKING DIAGRAM**

= Assembly Location

WL = Wafer Lot / Assembly Lot

Y = Year

WW = Work Week xx = 00, 01, 10, 11

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 13 of this data sheet.

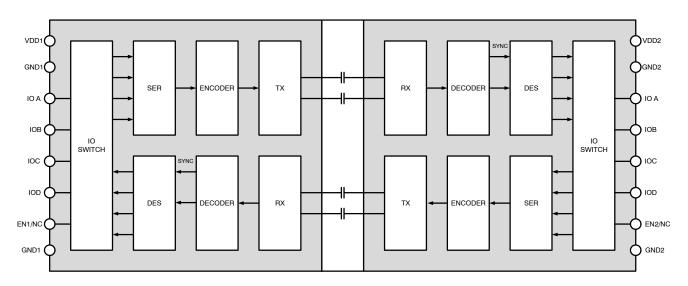

# **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

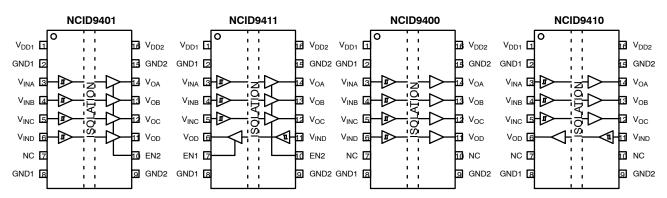

### **PIN CONFIGURATION**

Figure 2. Pin and Channel Configuration

### **PIN DEFINITION**

| Name             | Pin No.<br>NCID9401 | Pin No.<br>NCID9411 | Pin No.<br>NCID9400 | Pin No.<br>NCID9410 | Description                            |

|------------------|---------------------|---------------------|---------------------|---------------------|----------------------------------------|

| V <sub>DD1</sub> | 1                   | 1                   | 1                   | 1                   | Power Supply, Side 1                   |

| GND1             | 2                   | 2                   | 2                   | 2                   | Ground Connection for V <sub>DD1</sub> |

| V <sub>INA</sub> | 3                   | 3                   | 3                   | 3                   | Input, Channel A                       |

| $V_{INB}$        | 4                   | 4                   | 4                   | 4                   | Input, Channel B                       |

| V <sub>INC</sub> | 5                   | 5                   | 5                   | 5                   | Input, Channel C                       |

| V <sub>IND</sub> | 6                   | 11                  | 6                   | 11                  | Input, Channel D                       |

| EN1              | -                   | 7                   | -                   | -                   | Output Enable 1                        |

| NC               | 7                   | -                   | 7                   | 7                   | No Connect                             |

| GND1             | 8                   | 8                   | 8                   | 8                   | Ground Connection for V <sub>DD1</sub> |

| GND2             | 9                   | 9                   | 9                   | 9                   | Ground Connection for V <sub>DD2</sub> |

| NC               | -                   | =                   | 10                  | 10                  | No Connect                             |

| EN2              | 10                  | 10                  | -                   | -                   | Output Enable 2                        |

| V <sub>OD</sub>  | 11                  | 6                   | 11                  | 6                   | Output, Channel D                      |

| V <sub>OC</sub>  | 12                  | 12                  | 12                  | 12                  | Output, Channel C                      |

| V <sub>OB</sub>  | 13                  | 13                  | 13                  | 13                  | Output, Channel B                      |

| V <sub>OA</sub>  | 14                  | 14                  | 14                  | 14                  | Output, Channel A                      |

| GND2             | 15                  | 15                  | 15                  | 15                  | Ground Connection for V <sub>DD2</sub> |

| V <sub>DD2</sub> | 16                  | 16                  | 16                  | 16                  | Power Supply, Side 2                   |

# **SPECIFICATIONS**

# TRUTH TABLE (Note 1)

| V <sub>INX</sub> | EN <sub>X</sub> | V <sub>DDI</sub> | V <sub>DDO</sub> | v <sub>ox</sub>          | Comment                                                                                          |

|------------------|-----------------|------------------|------------------|--------------------------|--------------------------------------------------------------------------------------------------|

| Н                | H/NC            | Power Up         | Power Up         | Н                        | Normal Operation                                                                                 |

| L                | H/NC            | Power Up         | Power Up         | L                        | Normal Operation                                                                                 |

| Х                | L               | Power Up         | Power Up         | Hi–Z                     |                                                                                                  |

| Х                | H/NC            | Power Down       | Power Up         | L                        | Default low; V <sub>OX</sub> return to normal operation when V <sub>DDI</sub> change to Power Up |

| Х                | H/NC            | Power Up         | Power Down       | Undetermined<br>(Note 2) | $V_{OX}$ return to normal operation when $V_{DDO}$ change to Power Up                            |

VINX = Input signal of a given channel (A, B, C or D). EN<sub>X</sub> = Enable pin for primary or secondary side (1 or 2). V<sub>OX</sub> = Output signal of a given channel (A, B, C or D). V<sub>DDI</sub> = Input-side V<sub>DD</sub>. V<sub>DDO</sub> = Output-side V<sub>DD</sub>. X = Irrelevant. H = High level. L = Low level. NC = No Connection.

The outputs are in undetermined state when V<sub>DDO</sub> < V<sub>UVLO</sub>.

#### **SAFETY AND INSULATION RATINGS**

As per DIN EN/IEC 60747-17, this digital isolator is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings must be ensured by means of protective circuits.

| Symbol                | Parameter                                                                                                                                  |                         | Min             | Тур       | Max | Unit              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-----------|-----|-------------------|

|                       | Installation Classifications per DIN VDE 0110/1.89                                                                                         | < 150 V <sub>RMS</sub>  | -               | I–IV      | -   |                   |

|                       | Table 1 Rated Mains Voltage                                                                                                                | < 300 V <sub>RMS</sub>  | -               | I–IV      | -   |                   |

|                       |                                                                                                                                            | < 450 V <sub>RMS</sub>  | -               | I–IV      | -   |                   |

|                       |                                                                                                                                            | < 600 V <sub>RMS</sub>  | -               | I–IV      | -   |                   |

|                       |                                                                                                                                            | < 1000 V <sub>RMS</sub> | -               | I–III     | -   |                   |

|                       | Climatic Classification                                                                                                                    |                         | -               | 40/125/21 | -   |                   |

|                       | Pollution Degree (DIN VDE 0110/1.89)                                                                                                       |                         | -               | 2         | -   |                   |

| CTI                   | Comparative Tracking Index (DIN IEC 112/VDE 0303                                                                                           | Part 1)                 | 600             | =         | -   |                   |

| V <sub>PR</sub>       | Input–to–Output Test Voltage, Method b, $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1$ s, Partial Discharge < 5 pC |                         | 3750            | -         | -   | V <sub>peak</sub> |

|                       | Input-to-Output Test Voltage, Method a, $V_{IORM} \times 1.6$ and Sample Test with $t_m = 10$ s, Partial Discharge < 5                     |                         | 3200            | -         | -   | V <sub>peak</sub> |

| V <sub>IORM</sub>     | Maximum Working Insulation Voltage                                                                                                         |                         | 2000            | _         | -   | V <sub>peak</sub> |

| V <sub>IOTM</sub>     | Highest Allowable Over Voltage                                                                                                             |                         | 8000            | -         | -   | V <sub>peak</sub> |

| E <sub>CR</sub>       | External Creepage                                                                                                                          |                         | 8.0             | -         | -   | mm                |

| E <sub>CL</sub>       | External Clearance                                                                                                                         |                         | 8.0             | -         | -   | mm                |

| DTI                   | Insulation Thickness                                                                                                                       | Insulation Thickness    |                 | -         | -   | mm                |

| T <sub>Case</sub>     | Safety Limit Values – Maximum Values in Failure; Case Temperature                                                                          |                         | 150             | -         | -   | °C                |

| P <sub>S,INPUT</sub>  | Safety Limit Values – Maximum Values in Failure; Input Power                                                                               |                         | 100             | -         | -   | mW                |

| P <sub>S,OUTPUT</sub> | Safety Limit Values – Maximum Values in Failure; Output Power                                                                              |                         | 600             | -         | -   | mW                |

| R <sub>IO</sub>       | Insulation Resistance at TS, V <sub>IO</sub> = 500 V                                                                                       |                         | 10 <sup>9</sup> | -         | -   | Ω                 |

### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol           | Parameter                                                     | Value        | Unit |

|------------------|---------------------------------------------------------------|--------------|------|

| T <sub>STG</sub> | Storage Temperature                                           | -55 to +150  | °C   |

| T <sub>OPR</sub> | Operating Temperature                                         | -40 to +125  | °C   |

| T <sub>J</sub>   | Junction Temperature                                          | -40 to +150  | °C   |

| T <sub>SOL</sub> | Lead Solder Temperature (Refer to Reflow Temperature Profile) | 260 for 10 s | °C   |

| $V_{DD}$         | Supply Voltage (V <sub>DDx</sub> )                            | -0.5 to 6    | V    |

| V                | Voltage (V <sub>INx</sub> , V <sub>Ox</sub> , ENx)            | -0.5 to 6    | V    |

| Io               | Average Output Current                                        | 10           | mA   |

| PD               | Power Dissipation                                             | 210          | mW   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### **RECOMMENDED OPERATING RANGES**

| Symbol                            | Parameter                             | Min                  | Max                  | Unit |

|-----------------------------------|---------------------------------------|----------------------|----------------------|------|

| T <sub>A</sub>                    | Ambient Operating Temperature         | -40                  | +125                 | °C   |

| V <sub>DD1</sub> V <sub>DD2</sub> | Supply Voltage (Notes 3, 4)           | 2.5                  | 5.5                  | V    |

| V <sub>INH</sub>                  | High Level Input Voltage              | $0.7 \times V_{DDI}$ | $V_{\mathrm{DDI}}$   | V    |

| V <sub>INL</sub>                  | Low Level Input Voltage               | 0                    | $0.1 \times V_{DDI}$ | V    |

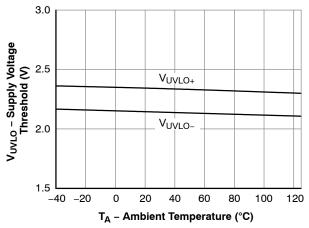

| $V_{\text{UVLO}+}$                | Supply Voltage UVLO Rising Threshold  | 2.2                  | -                    | V    |

| V <sub>UVLO</sub> _               | Supply Voltage UVLO Falling Threshold | 2.0                  | -                    | V    |

| UVLO <sub>HYS</sub>               | Supply Voltage UVLO Hysteresis        | 0.1                  | -                    | V    |

| I <sub>OH</sub>                   | High Level Output Current             | -2                   | -                    | mA   |

| I <sub>OL</sub>                   | Low Level Output Current              | _                    | 2                    | mA   |

| DR                                | Signaling Rate                        | 0                    | 10                   | Mbps |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ISOLATION CHARACTERISTICS**

Apply over all recommended conditions. All typical values are measured at  $T_A = 25$ °C.

| Symbol           | Parameter                         | Conditions                                                                                                    | Min  | Тур              | Max | Unit             |

|------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------|------|------------------|-----|------------------|

| V <sub>ISO</sub> | Input-Output Isolation<br>Voltage | $T_A=25^{\circ}C$ , Relative Humidity < 50%, t = 1.0 minute, $I_{I-O}\leq$ 10 $\mu A$ , 50 Hz (Notes 5, 6, 7) | 5000 | 1                | 1   | V <sub>RMS</sub> |

| R <sub>ISO</sub> | Isolation Resistance              | V <sub>I-O</sub> = 500 V (Note 5)                                                                             | ı    | 10 <sup>11</sup> | ı   |                  |

| C <sub>ISO</sub> | Isolation Capacitance             | V <sub>I-O</sub> = 0 V, Frequency = 1.0 MHz<br>(Note 5)                                                       | _    | 1                | -   | pF               |

<sup>5.</sup> Device is considered a two-terminal device: pins 1 to 8 are shorted together and pins 9 to 16 are shorted together.

<sup>3.</sup> During power up or down, ensure that both the input and output supply voltages reach the proper recommended operating voltages to avoid any momentary instability at the output state.

<sup>4.</sup> For reliable operation at recommended operating conditions, V<sub>DD</sub> supply pins require at least a pair of external bypass capacitors, placed within 2 mm from V<sub>DD</sub> pins 1 and 16 and GND pins 2 and 15. Recommended values are 0.1 μF and 1 μF.

<sup>6. 5,000</sup> V<sub>RMS</sub> for 1-minute duration is equivalent to 6,000 V<sub>RMS</sub> for 1-second duration.

<sup>7.</sup> The input-output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input-output continuous voltage rating. For the continuous working voltage rating, refer to equipment-level safety specification or DIN EN/IEC 60747-17 Safety and Insulation Ratings Table on page 4.

# **ELECTRICAL CHARACTERISTICS**

Apply over all recommended conditions,  $T_A = -40$ °C to +125°C,  $V_{DD1} = V_{DD2} = 2.5$  V to 5.5 V, unless otherwise specified. All typical values are measured at  $T_A = 25$ °C.

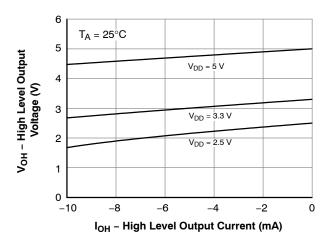

| Symbol                | Parameter                             | Conditions                                                                                                                                 | Min                  | Тур                  | Max                  | Unit  | Figure |

|-----------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------|--------|

| V <sub>OH</sub>       | High Level Output                     | $V_{DD} = 5 \text{ V}, I_{OH} = -4 \text{ mA}$                                                                                             | 4.4                  | 4.8                  | -                    | V     | 11     |

|                       | Voltage                               | $V_{DD} = 3.3 \text{ V}, I_{OH} = -2 \text{ mA}$                                                                                           | 2.9                  | 3.2                  | ]                    |       |        |

|                       |                                       | V <sub>DD</sub> = 2.5 V, I <sub>OH</sub> = -1 mA                                                                                           | 2.1                  | 2.4                  | ]                    |       |        |

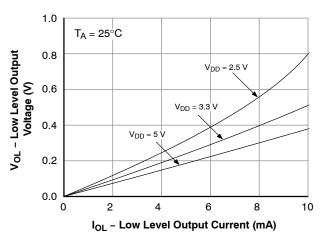

| V <sub>OL</sub>       | Low Level Output                      | V <sub>DD</sub> = 5 V, I <sub>OL</sub> = 4 mA                                                                                              | -                    | 0.1                  | 0.4                  | V     | 12     |

|                       | Voltage                               | V <sub>DD</sub> = 3.3 V, I <sub>OL</sub> = 2 mA                                                                                            |                      |                      |                      |       |        |

|                       |                                       | V <sub>DD</sub> = 2.5 V, I <sub>OL</sub> = 1 mA                                                                                            |                      |                      |                      |       |        |

| V <sub>INT+</sub>     | Rising Input Voltage<br>Threshold     |                                                                                                                                            | -                    | -                    | $0.7 \times V_{DDI}$ | V     |        |

| $V_{INT-}$            | Falling Input Voltage<br>Threshold    |                                                                                                                                            | $0.1 \times V_{DDI}$ | -                    | -                    | V     |        |

| V <sub>INT(HYS)</sub> | Input Threshold Voltage<br>Hysteresis |                                                                                                                                            | $0.1 \times V_{DDI}$ | $0.2 \times V_{DDI}$ | -                    | V     |        |

| I <sub>INH</sub>      | High Level Input Current              | $V_{IH} = V_{DDI}$                                                                                                                         | -                    | -                    | 1                    | μΑ    |        |

| I <sub>INL</sub>      | Low Level Input Current               | V <sub>IL</sub> = 0 V                                                                                                                      | -1                   | -                    | -                    | μΑ    |        |

| CMTI                  | Common Mode Transient<br>Immunity     | V <sub>I</sub> = V <sub>DDI</sub> or 0 V,<br>V <sub>CM</sub> = 1500 V                                                                      | 100                  | 150                  | -                    | kV/μs | 16     |

| C <sub>IN</sub>       | Input Capacitance                     | $\begin{aligned} V_{IN} &= V_{DDI}/2 + 0.4 \times \text{sin } (2\pi \text{ft}), \\ f &= 1 \text{ MHz}, V_{DD} = 5 \text{ V} \end{aligned}$ | -                    | 2                    | -                    | pF    |        |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

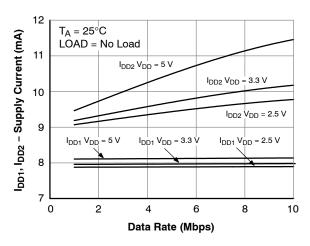

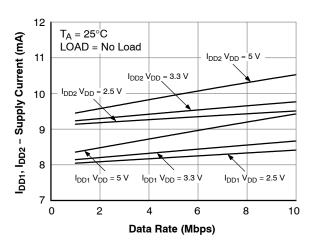

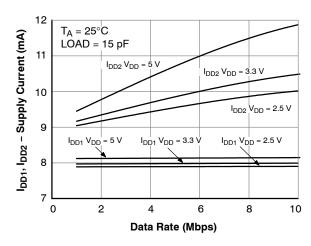

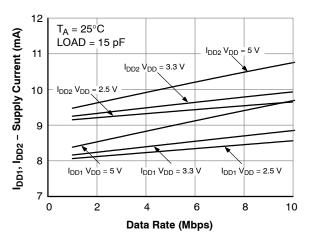

# **SUPPLY CURRENT CHARACTERISTICS**

Apply over all recommended conditions,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  unless otherwise specified. All typical values are measured at  $T_A = 25^{\circ}C$ .

| Symbol           | Parameter                    | Conditions                                                     | Min  | Тур  | Max  | Unit | Figure        |

|------------------|------------------------------|----------------------------------------------------------------|------|------|------|------|---------------|

| I <sub>DD1</sub> | DC Supply Current            | V <sub>DD</sub> = 5 V, EN = 0/5 V,                             | -    | 8.3  | 11.3 | mA   |               |

| I <sub>DD2</sub> |                              | V <sub>IN</sub> = 0/5 V                                        |      | 9.3  | 12.3 | ]    |               |

| I <sub>DD1</sub> |                              | $V_{DD} = 3.3 \text{ V, EN} = 0/3.3 \text{ V,}$                |      | 8.0  | 11   | ]    |               |

| I <sub>DD2</sub> |                              | $V_{IN} = 0/3.3 \text{ V}$                                     |      | 9.1  | 12   | ]    |               |

| I <sub>DD1</sub> |                              | $V_{DD} = 2.5 \text{ V}, \text{ EN} = 0/2.5 \text{ V},$        |      | 7.9  | 10.8 | ]    |               |

| I <sub>DD2</sub> |                              | $V_{IN} = 0/2.5 \text{ V}$                                     |      | 9.0  | 11.8 | ]    |               |

| I <sub>DD1</sub> | AC Supply Current  1 Mbps    | V <sub>DD</sub> = 5 V, EN = 5 V,                               | -    | 8.4  | 11.3 | mA   | 3, 4,<br>5, 6 |

| I <sub>DD2</sub> | - I Mbps                     | C <sub>L</sub> = 15 pF,<br>V <sub>IN</sub> = 5 V Square Wave   |      | 9.5  | 12.3 |      | 5, 0          |

| I <sub>DD1</sub> |                              | V <sub>DD</sub> = 3.3 V, EN = 3.3 V,                           |      | 8.1  | 11   |      |               |

| I <sub>DD2</sub> |                              | $C_L = 15 \text{ pF},$<br>$V_{IN} = 3.3 \text{ V Square Wave}$ |      | 9.2  | 12   |      |               |

| I <sub>DD1</sub> |                              | V <sub>DD</sub> = 2.5 V, EN = 2.5 V,                           |      | 8.0  | 10.8 |      |               |

| I <sub>DD2</sub> |                              | C <sub>L</sub> = 15 pF,<br>V <sub>IN</sub> = 2.5 V Square Wave |      | 9.1  | 11.8 | 1    |               |

| I <sub>DD1</sub> | AC Supply Current<br>10 Mbps | V <sub>DD</sub> = 5 V, EN = 5 V,                               | -    | 8.9  | 12.6 | mA   |               |

| I <sub>DD2</sub> | To Mibbs                     | $C_L = 15 \text{ pF},$<br>$V_{IN} = 5 \text{ V Square Wave}$   | 11.3 | 13.6 |      |      |               |

| I <sub>DD1</sub> |                              | V <sub>DD</sub> = 3.3 V, EN = 3.3 V,                           |      | 8.4  | 11.7 |      |               |

| I <sub>DD2</sub> |                              | $C_L = 15 \text{ pF},$<br>$V_{IN} = 3.3 \text{ V Square Wave}$ |      | 10.2 | 12.7 | 1    |               |

| I <sub>DD1</sub> | 7                            | V <sub>DD</sub> = 2.5 V, EN = 2.5 V,                           | 1    | 8.2  | 11.3 | 1    |               |

| I <sub>DD2</sub> | 7                            | C <sub>L</sub> = 15 pF,<br>V <sub>IN</sub> = 2.5 V Square Wave |      | 9.8  | 12.3 | 1    |               |

### **SWITCHING CHARACTERISTICS - NCID9401/NCID9400**

Apply over all recommended conditions,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  unless otherwise specified. All typical values are measured at  $T_A = 25^{\circ}C$ .

| Symbol               | Parameter                                       | Ch  | Conditions                                      | Min | Тур  | Max  | Unit | Figure |  |  |

|----------------------|-------------------------------------------------|-----|-------------------------------------------------|-----|------|------|------|--------|--|--|

| t <sub>PHL</sub>     | Propagation Delay to Logic Low                  | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -   | 136  | 200  | ns   | 8, 13  |  |  |

|                      | Output (Note 8)                                 |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

| t <sub>PLH</sub>     | Propagation Delay to Logic High                 | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -   | 137  | 200  | ns   |        |  |  |

|                      | Output (Note 9)                                 |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

| PWD                  | Pulse Width Distortion                          | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | _   | 33   | 80   | ns   |        |  |  |

|                      | t <sub>PHL</sub> – t <sub>PLH</sub>   (Note 10) |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

| t <sub>PSK(PP)</sub> | Propagation Delay Skew                          | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -80 | -    | 80   | ns   | 1      |  |  |

|                      | (Part to Part) (Note 11)                        |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      | _      |  |  |

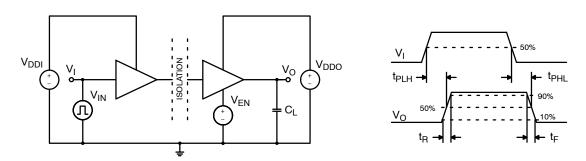

| t <sub>R</sub>       | Output Rise Time (10% to 90%)                   | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | _   | 3    | _    | ns   |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

| t <sub>F</sub>       | Output Fall Time (90% to 10%)                   | All | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | _   | 2    | 2    | _    | ns     |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

|                      |                                                 |     | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |     |      |      |      |        |  |  |

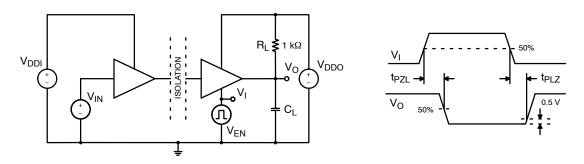

| t <sub>PZL</sub>     | High Impedance to Logic Low                     | All | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | _   | 8.4  | 25   | ns   | 14     |  |  |

|                      | Output Delay (Notes 12, 16)                     |     | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |     | 9.9  | 1    |      |        |  |  |

|                      |                                                 |     | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |     | 12.3 | 1    |      |        |  |  |

| $t_{PLZ}$            | Logic Low to High Impedance                     | All | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | _   | 10.8 | 25   | ns   |        |  |  |

|                      | Output Delay (Notes 13, 16)                     |     | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |     | 14.5 |      |      |        |  |  |

|                      |                                                 |     | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |     | 17.8 | 1    |      |        |  |  |

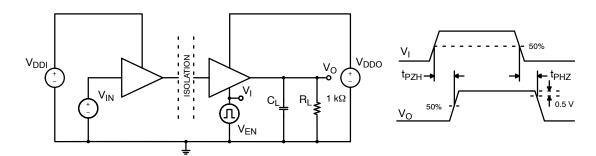

| t <sub>PZH</sub>     | High Impedance to Logic High                    | All | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | _   | 0.53 | 1    | μs   | 15     |  |  |

|                      | Output Delay (Notes 14, 16)                     |     | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |     | 0.50 | 0.50 | 0.50 | 1      |  |  |

|                      |                                                 |     | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |     | 0.50 |      |      |        |  |  |

| t <sub>PHZ</sub>     | Logic High to High Impedance                    | All | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | -   | 11.7 | 25   | ns   | 1      |  |  |

|                      | Output Delay (Notes 15, 16)                     |     | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |     | 13.1 |      |      |        |  |  |

|                      |                                                 |     | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |     | 15.0 | ]    |      |        |  |  |

Propagation delay t<sub>PHL</sub> is measured from the 50% level of the falling edge of the input pulse to the 50% level of the falling edge of the V<sub>O</sub> signal.

<sup>9.</sup> Propagation delay  $t_{PLH}$  is measured from the 50% level of the rising edge of the input pulse to the 50% level of the rising edge of the  $V_O$  signal. 10. PWD is defined as  $|t_{PHL} - t_{PLH}|$  for any given device.

<sup>11.</sup> Part-to-part propagation delay skew is the difference between the measured propagation delay times of a specified channel of any two parts at identical operating conditions and equal load.

<sup>12.</sup> Enable delay t<sub>PZL</sub> is measured from the 50% level of the rising edge of the EN pulse to the 50% of the falling edge of the V<sub>O</sub> signal as it switches from high impedance state to low state.

<sup>13.</sup> Disable delay t<sub>PLZ</sub> is measured from the 50% level of the falling edge of the EN pulse to 0.5 V level of the rising edge of the V<sub>O</sub> signal as it switches from low state to high impedance state.

<sup>14.</sup> Enable delay t<sub>PZH</sub> is measured from the 50% level of the rising edge of the EN pulse to the 50% of the rising edge of the V<sub>O</sub> signal as it switches from high impedance state to high state.

<sup>15.</sup> Disable delay  $t_{PHZ}$  is measured from the 50% level of the falling edge of the EN pulse to  $V_{OH}$  – 0.5 V level of the falling edge of the  $V_{O}$  signal as it switches from high state to high impedance state.

<sup>16.</sup> For devices with EN pin: NCID9401 and NCID9411.

# SWITCHING CHARACTERISTICS - NCID9411/NCID9410

Apply over all recommended conditions,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  unless otherwise specified. All typical values are measured at  $T_A = 25^{\circ}C$ .

| Symbol               | Parameter                       | Ch                                              | Conditions                                      | Min                                             | Тур  | Max | Unit  | Figure    |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|----------------------|---------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------|-----|-------|-----------|--|--|--|--|--|--|----------|----------|--|--|--|--|--|--|--|--|--|

| t <sub>PHL</sub>     | Propagation Delay to Logic      | A, B, C                                         | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 115  | 170 | ns    | 9, 10, 13 |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | Low Output (Note 8)             |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 | D                                               | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 77   | 110 | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>PLH</sub>     | Propagation Delay to Logic      | A,B,C                                           | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 117  | 170 | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | High Output (Note 9)            |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 | D                                               | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 78   | 110 | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| PWD                  | Pulse Width Distortion          | A,B,C                                           | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -70                                             | 26   | 70  | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | t <sub>PHL</sub>                |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 | D                                               | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -40                                             | 13   | 40  | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>PSK(PP)</sub> | Propagation Delay Skew          | All                                             | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -70                                             | -    | 70  | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | (Part to Part) (Note 11)        | (Part to Part) (Note 11)                        |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>R</sub>       | Output Rise Time                | All                                             | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 3    | _   | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | (10% to 90%)                    |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF | 7 1                                             | 7    |     |       |           |  |  |  |  |  |  | <u> </u> | <u> </u> |  |  |  |  |  |  |  |  |  |

| t <sub>F</sub>       | Output Fall Time                | All                                             | V <sub>DD</sub> = 5 V, C <sub>L</sub> = 15 pF   | -                                               | 2    | _   | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | (90% to 10%)                    |                                                 | V <sub>DD</sub> = 3.3 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | V <sub>DD</sub> = 2.5 V, C <sub>L</sub> = 15 pF |                                                 |      |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>PZL</sub>     | High Impedance to Logic         | All                                             | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | -                                               | 8.5  | 25  | ns    | 14        |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | Low Output Delay (Notes 12, 16) |                                                 | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |                                                 | 10.2 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |                                                 | 12.6 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| $t_{PLZ}$            | Logic Low to High Impedance     | All                                             | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | -                                               | 10.8 | 25  | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | Output Delay (Notes 13, 16)     |                                                 | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |                                                 | 14.6 | 1   |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |                                                 | 17.8 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>PZH</sub>     | High Impedance to Logic High    | All                                             | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | -                                               | 0.54 | 1   | μs 15 | 15        |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | Output Delay (Notes 14, 16)     |                                                 | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |                                                 | 0.50 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |                                                 | 0.50 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

| t <sub>PHZ</sub>     | Logic High to High Impedance    | All                                             | $V_{DD} = 5 \text{ V}, R_L = 1 \text{ k}\Omega$ | -                                               | 11.6 | 25  | ns    |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      | Output Delay (Notes 15, 16)     |                                                 | $V_{DD}$ = 3.3 V, $R_L$ = 1 k $\Omega$          |                                                 | 12.9 |     |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

|                      |                                 |                                                 | $V_{DD}$ = 2.5 V, $R_L$ = 1 k $\Omega$          |                                                 | 14.6 | 1   |       |           |  |  |  |  |  |  |          |          |  |  |  |  |  |  |  |  |  |

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. NCID9401/NCID9400 Supply Current vs. Data Rate (No Load)

Figure 5. NCID9411/NCID9410 Supply Current vs.

Data Rate (No Load)

Figure 7. Supply Voltage UVLO Threshold vs.

Ambient Temperature

Figure 4. NCID9401/NCID9400 Supply Current vs.

Data Rate (Load = 15 pF)

Figure 6. NCID9411/NCID9410 Supply Current vs.

Data Rate (Load = 15 pF)

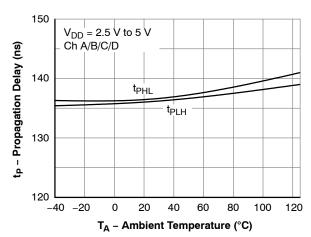

Figure 8. NCID9401/NCID9400 Propagation Delay vs.

Ambient Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

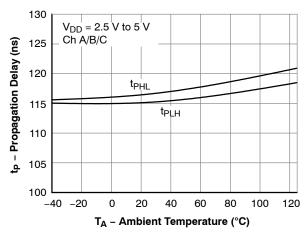

Figure 9. NCID9411/NCID9410 Channel A/B/C Propagation Delay vs. Ambient Temperature

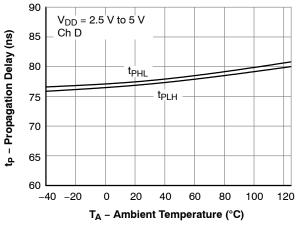

Figure 10. NCID9411/NCID9410 Channel D Propagation Delay vs. Ambient Temperature

Figure 11. High Level Output Voltage vs. Current

Figure 12. Low Level Output Voltage vs. Current

# **TEST CIRCUITS**

Figure 13.  $V_{\text{IN}}$  to  $V_{\text{O}}$  Propagation Delay Test Circuit and Waveform

Figure 14. EN to Logic Low Vo Propagation Delay Test Circuit and Waveform

Figure 15. EN to Logic High V<sub>O</sub> Propagation Delay Test Circuit and Waveform

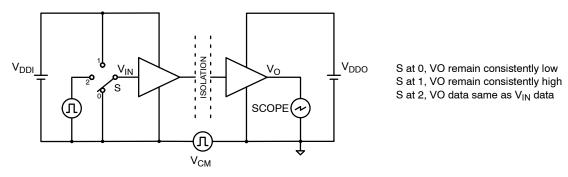

Figure 16. Common Mode Transient Immunity Test Circuit

#### APPLICATION INFORMATION

#### **Theory of Operation**

NCID9401, NCID9411, NCID9400 and NCID9410 are quad-channel digital isolators. The chip to chip galvanic isolation are provided by a pair of off-chip capacitors. Digital circuits are used for processing signals through the 0.5 mm thick isolation barrier.

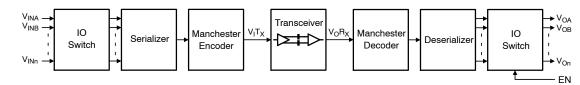

Pins are trimmed internally as input or output at IO Switch. Each direction of communication between two isolated circuits are achieved by implementing a pair of Serializer/Deserializer and Manchester Encoder/Decoder functional blocks as shown in Figure 17. The Serializer circuit converts the parallel data from the IO Switch into a serial (one bit) stream and the Manchester Encoder converts this data stream into coded data making it more robust, efficient and accurate for transmission. After encoding, all inputs signals are coded as V<sub>I</sub>T<sub>X</sub> and transmitted across the isolation barrier via Transceiver.

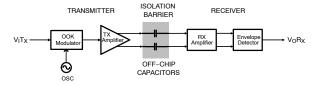

The off-chip ceramic capacitors that serve both as the isolation barrier and as the medium of transmission for signal switching using On-Off keying (OOK) technique are illustrated in the transceiver block diagram in Figure 18

and Figure 19. At the transmitter side, the  $V_I T_X$  input logic state is modulated with a high frequency carrier signal. The resulting signal is amplified and transmitted to the isolation barrier. The receiver side detects the barrier signal and demodulates it using an envelope detection technique and output  $V_O R_X$ .

The output signal of the transceiver  $V_0R_X$  will go to the Manchester Decoder. This decoder is used along with the receiver to recover the original data from the coded form and the Deserializer converts the serial stream back to the original, parallel data and redistributed back to the corresponding output pins. Both the Serializer/Deserializer and Manchester Encoder/Decoder are functional blocks on the transmitting and receiving chips.

For devices with EN, the output enable pin EN controls the impedance of the  $V_{OX}$ . When EN is at LOW, output  $V_{OX}$  is set to high impedance state. The  $V_{OX}$  will only follow the  $V_{INX}$  when EN is set to HIGH.  $V_{OX}$  is at default state LOW when the power supply at the transmitter side is turned off or the input  $V_{INX}$  is disconnected.

Figure 17. Operational Block Diagram of Multi-Channels for Forward Direction

Figure 18. Block Diagram of Transceiver

# V<sub>I</sub>T<sub>X</sub> ISOLATION BARRIER SIGNAL V<sub>O</sub>R<sub>X</sub>

Figure 19. On-Off Keying Modulation Signals

## **Layout Recommendation**

Layout of the digital circuits relies on good suppression of unwanted noise and electromagnetic interference. It is recommended to use 4-layer FR4 PCB, with ground plane below the components, power plane below the ground plane, signal lines and power fill on top, and signal lines and ground fill at the bottom as shown in Figure 20. The alternating polarities of the layers creates interplane capacitances that aids the bypass capacitors required for reliable operation at digital switching rates.

In the layout with digital isolators, it is required that the isolated circuits have separate ground and power planes. The section below the device should be clear with no power, ground or signal traces. Maintain a gap equal to or greater than the specified minimum creepage clearance of the device package.

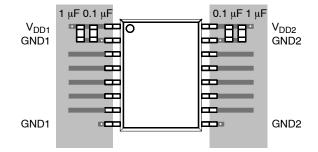

It is highly advised to connect at least a pair of low ESR supply bypass capacitors, placed within 2 mm from the

power supply pins 1 and 16 and ground pins 2 and 15 as shown in Figure 21. Recommended values are 1  $\mu$ F and 0.1  $\mu$ F, respectively. Place them between the  $V_{DD}$  pins of the device and the via to the power planes, with the higher frequency, lower value capacitor closer to the device pins. Directly connect the device ground pins 2, 8, 9 and 15 by via to their corresponding ground planes.

#### **Over Temperature Detection**

NCID9401, NCID9411, NCID9400 and NCID9410 have built-in Over Temperature Detection (OTD) feature that protects the IC from thermal damage. The output pins will automatically switch to default state when the ambient temperature exceeds the maximum junction temperature at threshold of approximately 160°C. The device will return to normal operation when the temperature decreases approximately 20°C below the OTD threshold.

Figure 20. 4-Layer PCB for Digital Isolator

Figure 21. Placement of Bypass Capacitors

### **ORDERING INFORMATION**

| Part Number | Grade      | Package  | Shipping <sup>†</sup>   |

|-------------|------------|----------|-------------------------|

| NCID9401    | Industrial | SOIC16 W | 50 Units / Tube         |

| NCID9401R2  | Industrial | SOIC16 W | 750 Units / Tape & Reel |

| NCIV9401*   | Automotive | SOIC16 W | 50 Units / Tube         |

| NCIV9401R2* | Automotive | SOIC16 W | 750 Units / Tape & Reel |

| NCID9411    | Industrial | SOIC16 W | 50 Units / Tube         |

| NCID9411R2  | Industrial | SOIC16 W | 750 Units / Tape & Reel |

| NCIV9411*   | Automotive | SOIC16 W | 50 Units / Tube         |

| NCIV9411R2* | Automotive | SOIC16 W | 750 Units / Tape & Reel |

| NCID9400    | Industrial | SOIC16 W | 50 Units / Tube         |

| NCID9400R2  | Industrial | SOIC16 W | 750 Units / Tape & Reel |

| NCIV9400*   | Automotive | SOIC16 W | 50 Units / Tube         |

| NCIV9400R2* | Automotive | SOIC16 W | 750 Units / Tape & Reel |

| NCID9410    | Industrial | SOIC16 W | 50 Units / Tube         |

| NCID9410R2  | Industrial | SOIC16 W | 750 Units / Tape & Reel |

| NCIV9410*   | Automotive | SOIC16 W | 50 Units / Tube         |

| NCIV9410R2* | Automotive | SOIC16 W | 750 Units / Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

ON Semiconductor is licensed by the Philips Corporation to carry the  $I^2C$  bus protocol.

<sup>\*</sup>NCIV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

|                  |             | iner remem and dierremeng.                                                                                                                                       |          |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| DOCUMENT NUMBER: | 98AON13751G | Electronic versions are uncontrolled except when accessed directly from the Docum Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in re- |          |

| DESCRIPTION:     | SOIC16 W    | PAGI                                                                                                                                                             | E 1 OF 1 |

= Year

= Work Week

ww

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

XXXXXXXXX

or may not be present. Some products may

not follow the Generic Marking.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative